Микропрограммное устройство управления

Иллюстрации

Показать всеРеферат

Изобретение относится квЭчислительной технике. Цель изобретения - сокращение объема оборудования . Это достигается за счет введения в устройство счетчика, коммутатора адреса, распределителя синхроимпульсов , элемента ИЛИ, элемента И, элемента И-НЕ и двух элементов задержки с соответствующими функциональными связями между ними и известными блоками устройства. Вновь введенные блоки позволяют достигнуть противогоночного эффекта. 3 ил. ю О) ( ел сд

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„SU„„1226455

А (51) 4 С 06 F 9/22

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /, Н ABTOPCH0MV СВИДЕТЕЛЬСТВУ,,/

А (54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ (21) 3815415/24-24 (22) 19.10.84 (46) 23.04.86. Бюл. У 15 (72) Г.Н. Афанасьев, И.В. Волков, В.Я. Порецкий и Г.И. Шестакова (53) 681.32 (088.8) (56) Майоров С.А., Новиков Т.И. Принципы организации цифровых машин.

Л.: Машиностроение, 1974, с. 215.

Авторское свидетельство СССР

Ф 1005050, кл. G 06 F 9/22, 1983. г

Х (57) Изобретение относится к вЖислительной технике. Цель изобретения — сокращение объема оборудования. Это достигается за счет введения в устройство счетчика, коммутатора адреса, распределителя синхроимпульсов, элемента ИЛИ, элемента И, элемента И-HE и двух элементов задержки с соответствующими функциональными связями между ними и известными блоками устройства.

Вновь введенные блоки позволяют достигнуть противогоночного эффекта.

3 ил.

12?6455

Изобретение относится к вычислительной технике.

Цель изобретения — сокращение оборудования.

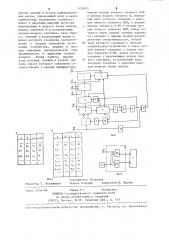

На фиг ° 1 приведена функциональная схема предлагаемого микропрограммного устройства управления, на фиг.2 ,фрагмент структуры второго блока памяти,на фиг.3 — - функциональная схема распределителя синхраимпульсов.

Микропрограммное устройство управления (фиг.1) содержит первый, блок 1 памяти, первый счетчик 2, регистр 3 микрокоманд, коммутатор 4 адреса, второй счетчик 5, второй блок б памяти, дешифратор 7,, группу 8 элементов И, первый и второй элементы ИЛИ 9 и 10, распределитель

11 синхраимпульсав, элемент И 12, элемент И-НЕ l3 первый и второй элементы 14 и 15 задержки, синхравход 16 устройства, вход 17 начальной установки устройства, вход 18 условий устройства, синхравходы 19 и 20, выход 21 устройства.

На фиг.2 обозначены адрес А ячейки блока 6, а также код В условия, код С адреса перехода и кад Д опроса, причем индекс обозначает принадлежность к i микрокоманде, а индекс ц — к а -му по исходному порядку опроса условию в i "й микрокоманде.

Фрагмент а соответствует микрокоманде с тремя проверяемыми условиями, а фрагмент а — той же микрокоманде после перепрограммирования с целью увеличения числа проверяемых в ней условий до четырех, причем вводимая дополнительно проверка с

1 кодами В и С является второй па порядку опроса, а гн — относительный адрес перехода в резервную зону памяти.

Распределитель 11 синхроимпульсов (фиг.3) содержит элемент И-НЕ 22 и элемент И 23.

Устройство работает следующим образом.

В исходном состоянии счетчики

2 и 5 и регистр 3 обнулены сигналоь с входа 17 начальной установки устройства. Сигналом с входа 19 из первого блока 1 считывается в регистр

3 первая микрокаманда, соответствующая нулевому состоянию счетчика 2.

При этом код микрооперации с выхоqa регистра 3 микрокоманд поступает на выход 21 устройства, а кад адре5

55 са ячейки с выхода регистра 3 — на первый информационный вход коммутатора 4 адреса.

Па нулевому содержанию второго счетчика. 5 определяется исходная ячейка второго блока б, в которую, в частности, занесен кад опроса 10.

При указанном коде опроса единичный сигнал с выхода второго блока 6 через второй элемент ИЛИ 10 и элемент 14 задержки, предназначенный для устранения гонок", поступает на управляющий вход распределителя

11 синхроимпульсав, разреДя прохождение очередного синхрасигнала с входа 20 устройства на разрешающий вход второго счетчика 5, а нулевой сигнал с выхода второго блока б через элемент И l2 поступает на управляющий вход коммутатора 4 адреса, разрешая прохождение кода адреса ячейки с второго выхода регистра 3 микракаманц на установочный вход второго счетчика 5. Таким образом обеспечивается занесение ва второй счетчик 5 кода адреса первой ячейки, соответствующей первой микрокоманде.

По этому адресу с выхода второго блока 6 считывается код первого проверяемого условия. Согласно этому коду дешифратор 7 подает единичный сигнал на первый вход соответствующего элемента И группы 8.

В случае выполнения соответствующего условия сигнал с входа 18 yc" ловий вызывает срабатывание элемента И группы 8 и образование единичного сигнала на выходе первого элемента ИЛИ 9, разрешающего прохождение синхроимпульса с входа 28 через введенный с целью устранения гонок" элемент 15 задержки и элемент И-НЕ

13 на разрешающий вход первого счетчика 2. При этом код адреса перехода с выхода второго блока б заносится в первый счетчик 2, чем обеспечивается условный переход устройства в заданное состояние °

Одновременно единичный сигнал с выхода первого элемента ИЛИ 9, вопервых, подается на вход элемента И

12, обеспечивая тем самым нулевой уровень на управляющем входе коммутатора 4 адреса и, во-вторых, поступает через второй элемент ИЛИ 10 и элемент 14 задержки на управляющий вход распределителя ll синхроимпульсов. Благодаря этому обеспечивается занесение во второй счетчик 5 нано1226455 4

1О

55 го кода адреса, содержащегося в новой микрокоманде.

В случае, если проверяемое условие не выполняется, разрешающий вход счетчика 2 блокируется, а дальнейшая работа устройства зависит от кода опроса.

При коде опроса 00 нулевой сигнал на выходе второго блока 6 вызывает установление нулевого уровня на управляющем входе распределителя 11, блокирующего разрешающий вход второго счетчика 5 и разрешающего прохождение синхроимпульса с входа

20 устройства на счетный вход счетчика 5.

При этом содержание счетчика 5 увеличивается на единицу, чем обеспечивается опрос следующего по порядку условия.. При невыполнении второго условия аналогичным образом происходит переход к третьей ячейке и т.д. до последнего относящегося к данной микрокоманде условия, которому соответствует ячейка с кодом опроса 10. При коде опроса 10 счетный вход второго счетчика 5 блокиро— ван ввиду единичного сигнала на выходе второго блока 6.

При этом состояние второго счетчика 5 не изменяется до прихода на счетный вход первого счетчика 2 очередного управляющего сигнала с входа 16 устройства, что вызывает увеличение содержимого счетчика 2 на единицу и, следовательно, переход к следующей по порядку микрокоманде, заносимой далее в регистр 3 микрокоманд. При этом новый код адреса через коммутатор 4 заносится во второй счетчик 5 очередным синхроимпульсом, поступающим с входа 20 устройства через распределитель 11 синхроимпульсов.

При коде опроса 11 (соответствующем непоследовательному переходу к следующей по порядку опроса груп— пе ячеек, относящихся к данной микрокоманде) и невыполнении проверяемого условия на первом и втором входах элемента И 12 устанавливаются соответственно единичный и нулевой уровни, при этом элемент И 12 срабатывает и переключает коммутатор 4 адреса в положение, при котором на установочный вход второго счетчика 5 поступают младшие разряmba кода выхода .второго блока 6. При этом во второй счетчик 5 очередным синхроимпульсом с входа 20 заносится код адреса первой ячейки в следующей по порядку опроса группе ячеек второго блока 6,относящейся к данной микрокоманде. В последнюю по порядку опроса ячейку последней относящейся к данной микрокоманде группы ячеек заносится код опроса 10.

В случае, если в микрокоманде проверяется одно условие, ему также соответствует код опроса 10. При этом работа устройства аналогична случаю последней проверки для микрокоманд с несколькими проверяемыми условиями.

Противогоночный эффект от введения элементов 14 и 15 задержки дос- . тигается при выполнении условий и >и где, и — время 1 задержки, обеспечиваемое элементами

14 и 15 соответственно; — длительность синхроимпульса, поступающего с входа 20; Ы вЂ” время установления многоразрядного кода на выходе вто рого блока 6. формула из обретения

Микропрограммное устройство управления, содержащее первый и второй блоки памяти, регистр микрокоманд, первый счетчик, дешифратор, группу элементов И и первый элемент ИЛИ, причем адресный вход и выход первого блока памяти подключены соответственно к выходу первого счетчика и информационному входу регистра микрокоманд, выход микроопераций которого соединен с выходом устройства, выход дешифратора соединен с первыми входами элементов И группы, вторые входы и выходы которых соединены соответственно с входом условий устройства и входами первого элемента ИЛИ, входы сброса первого счетчика и регистра микрокоманд подключены к входу начальной установки устройства, синхровход регистра микрокоманд и счетный вход первого счетчика подключены соответственно к первому и второму синхровходам устройства, о т л и ч а ющ е е с я тем, что, с целью сокращения оборудования, оно содержит второй счетчик, коммутатор адреса, распределитель синхроимпульсов, второй -элемент ИЛИ, элемент И, элемент И-НЕ и два элемента задержки, 226455

Our. 2

Составитель Логачева

Техред H.Кадар Корректор И. Эрдейи

Редактор Т. Кугрышева аказ ?134/48

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,, Раушская наб., д. 4/5

1р >нзводственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

5 1 причем первый и второй информационные входы, управляющий вход и выход коммутатора подключены соответственно к адресным выходам. регистра микрокоманд и второго блока памяти, выходу элемента И и установочным входам второго счетчика, вход сброса, счетный и разрешающий входы и выход которого соединены соответственно с входом начальной установки устройства, первыМ и вторым выходами распределителя синхроимпульсов и адресным входом второго блока памяти, выходы кода условий, первый и второй выходы опроса которого соединены соответственно с входом дешифратора, первым входом второго элемента ИЛИ и прямым входом элемента И, инверсный вход которого соединен с выходом первого элемента ИЛИ, с первым входом элемента И-HE и вторым входом второго элемента ИЛИ, выход которого через первый элемент задержки соединен с первым входом распределителя синхроимпульсов, второй вход которого соединен с третьим синхровходом устройства и через второй элемент задержки с вторым входом элемента И-HE выход которого соединен с разрешающим входом пер15 вого счетчика, установочный вход которого соединен с адресным выходом второго блока памяти.