Устройство для формирования тестов

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при тестовом диагностировании различных объектов. Цель изобрет ния - расширение области применения за счет обеспечения независимости от тестируемого объекта. Устройство содержит генератор псевдослучайной последовательности, формирователь импульсов, два счетчика, мультиплексор , блок индикации, блок памяти тестовых программ, элемент И и элемент ИЛИ. Генератор псевдослучайной последовательности вырабатывает последовательность импульсов с биномальным распределением по времени. В устройстве обеспечено многократное тестирование одними и теми же тестами . Возможно также обеспечение регулировки частоты генератора псевдослучайной последовательности и регулирование вредности появления выходных импульсов этого генератора, а также формирование любой последовательности тестов, что позволяет оптимизировать диагностику объекта контроля . 2 ил. сл с to INP о 4 tsD

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABBTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3784229/24-24 (22) 24.08.84 (46) 23.04.86. Бюл. Р 15 (72) С.В. Афанасьев (53) 681.3 (088.8) (56) Авторское свидетельство СССР

Н 964647, кл. G 06 F 11/16, 1981.

Авторское свидетельство СССР

N9 792252, кл. G 06 F )1/26, 1978. (54)УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ТЕСТОВ (57)Изобретение относится к области вычислительной техники и может быть использовано при тестовом диагностировании различных объектов. Цель изобрет ния — расширение области применения за счет обеспечения независимости от тестируемого объекта. Устройство содержит генератор псевдослуÄÄSUÄÄ 1226472 A (Я) 4 G 06 F 11/26 чайной последовательности, формирователь импульсов, два счетчика, мультиплексор, блок индикации, блок памяти тестовых программ, элемент И и элемент ИЛИ. Генератор псевдослучайной последовательности вырабатывает последовательность импульсов с биномальным распределением по времени. В устройстве обеспечено многократное тестирование одними и теми же тестами. Возможно также обеспечение регулировки частоты генератора псевдослучайной последовательности и регулирование вредности появления выходных импупьсов этого генератора, а также формирование любой последова- 9 тельности тестов, что позволяет оптимизировать диагностику объекта контроля. 2 ил. С:

1226472

Изобретение относится к области вычислительной техники и может быть использовано при тестовом диагностировании различных объектов, Цель изобретения — расширение области применения за счет обеспечения независимости от тестируемого объекта.

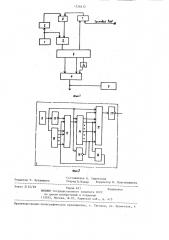

На фиг. 1 представлена блок-схема устройства; на фиг. 2 — схема генератора псевдослучайной последовательности.

Устройство содежит генератор 1 псевдослучайной последовательности, формирователь 2 импульсов, счетчики

31 и 3, мультиплексор 4, блок 5 индикации, блок 6 памяти тестовых программ, элемент И 7, элемент ИЛИ 8.

Генератор псевдослучайной последовательности содержит генератор 9 тактовых импульсов, счетчик 10, блоки

11 и 12.памяти, элемент НЕ 13, регистр 14 сдвига, делитель 15 частоты, ! сумматор по модулю два 16, элемент

НЕ 17.

Устройство работает следукпцим образом.

Цепи сброса условно не показаны.

При пуске устройства начинает работать генератор псевдослучайной последовательности, вырабатывающий последовательность импульсов с практически биномиальным распределением, которое при большой разрядности регистра 14 сдвига ассимптотически соответствует пуассоновскому распределению.

С приходом каждого импульса с выхода генератора 1 псевдослучайной последовательности, счетчик 3, устанавливается в исходное состояние, импульс с выхода формирователя 2 импульсов изменяет состояние счетчика

3, на единицу. Данное состояние счетчика 3 соответствует начальному адресу, по которому из блока памяти тестовых программ начнется считывание тестовых наборов. На один из входов элемента И поступают синхроимпульсы, которые проходят через элемент ИЛИ 8 на счетные вход счетчика 3, при появлении разрешающего импульса с выхода признака смены адреса блока памяти тестовых программ и изменяют выходной код счетчика 3, на единицу.

Блок памяти тестовых программ выполнен таким образом, что по каждо5

55 му адресу из него считывается инфор мания, которая представляет собой тестовые наборы и адреса, по которым будет происходить мультиплексирование этой информации на выход устройства и на блок индикации. Поскольку в устройстве используется генератор псевдослучайной последовательности, то счетчик 3, вырабатывает адреса, распределение которых во времени также определяется биномиальным законом распределения, а следовательно, в устройстве обеслечена возможность многократного тестирования объекта одними и теми же тестами, что приведет к повышению достоверности его диагностики.

Генератор псевдослучайной последовательности работает следующим образом.

Генератор 9 тактовых импульсов вырабатывает импульсы с частотой f, поступающие на счетный вход счетчика 10, изменяя адрес опрашиваемой ячейки блока 11 памяти. По кокнчании импульса на выходе инвертора 13 появится положительный сигнал, воздействующий на вход записи/чтения блока 11 памяти, обеспечивая считывание содержимого выбранной ячейки на вход последовательного сдвига регистра 14 сдвига. При появлении следующего тактового импульса осуществляется сдвиг содержимоro регистра

14 сдвига. Сумматор по модулю два 16 формирует сигнал в зависимости от состояний разрядов регистра 14 сдвига (п — число разрядов регистра 14 сдвига, К = 2,..., п — числа разрядов, которые поступают на сумматор по модулю два 16).

Нулевой потенциал на выходе элемента НЕ 13 переводит блок 12 памяти в режим записи информации и выходной сигнал сумматора по модулю два 16 записывается в опршиваемую ячейку блока 11 памяти. После заполнения счетчика IO сигнал с выхода переполнения переводит его в нулевое состояние и цикл повторяется.

Генератор 1 псевдослучайной последовательности с периодом повторения максимальной длины составляет основу управляемого генератора псевдослучайных чисел с практически биномиальным распределением импульсов формируемого потока, для чего исполу зован принцип случайной выборки сим1226472 волов из детерминированной последовательности.

Каждый тактовый импульс генератора 9 тактовых импульсов, поступающий на вход генератора. псевдослучайной последовательности, обеспечивает формирование на выходе сдвигающего регистра 14 адреса опрашиваемой ячейки блока 12 памяти. Тот же импульс, воздействуя на вход записи-чтения блока 12 памяти, обеспечивает считывание содержимого опрашиваемой ячейки блока 12 памяти. По окончании импульса блок 12 памяти переводится в режим записи информации. В ячейку с адресом, который определяется кодом на выходах сдвигающего регистра 14 записывается сигнал с выхода управляемого делителя 15 частоты..

Следующий тектовый импульс изме- 20 няет адрес опрашиваемой ячейки блока

ll памяти и цикл повторяется. Управляемый делитель 16 работает как преобразователь код — частота. Так как в режиме записи информации на выходе блока 12 памяти присутствует высокий логический уровень, на его выходе присутствует нулевой уровень только при опросе ячейки с нулевым символом.

Поскольку адрес опрашиваемой ячей- 30 ки задается случайным числом, то на выходе генератора I псевдослучайной последовательности формируется инверсная последовательность импульсов за счет элемента НЕ 17 с веро- 35 ятностью появления импульса за один

"Р такт, равной 1 2, где число L— код на управляющих входах управляемого делителя 15 частоты, р — разрядность кода. 40

Регулирование вероятности осуществляется изменением двоичной кодовой комбинации на управляющих входах управляемого делителя 15 частоты. При достаточно больших объемах 45 блоков 11 и 12 памяти выходная последовательность импульсов имеет большой период повторения с распределением, асимптотически приближаю. щимся к пуассоновскому. 50

Сочетание возможностей регулировки частоты генератора 9 тактовых импульсов, регулирования вороятности появления выходных импульсов генератора 1 псевдослучайной последовательности и формирование практически любой последовательности тестов позволяет оптимизировать диагностику объекта. формула изобретения

Устройство для формирования тестов, содержащее блок памяти тестовых программ, элемент ИЛИ и элемент

И, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет обеспечения независимости от тестируемого объекта, оно содержит генератор псевдослучайной последовательности, формирователь импульсов, счетчик, мультиплексор и блок индикации, причем выход генератора псевдослучайной последовательности соединен с входом сброса счетчика и входом формирователя импульсов, выход которого соединен с первым входом элемента ИЛИ, выход которого соединен со счетным входом первого счетчика, разрядные выходы которого соединены с адресными входами блока памяти тестовых программ, выход признака смены адреса которого соединен с первым входом элемента

И, выход которого соединен с вторым входом элемента ИЛИ, второй вход элемента И соединен с входом синхронизаций устройства, группа выходов тестовых программ соединена с первой группой информационных входов мультиплексора, вторая группа информационных входов которого соединена с группой разрядных выходов второго счетчика, счетный вход которого соединен с выходом признака смены тестового набора блока памяти тестовых программ, группа выходов адресов тестовых наборов блока памяти тестовых программ соединена .с группой адресных входов мультиплексора, выходы которого соединены с информационными входами блока индикации и являются информационными выходами устройства.! 226472

7дщтой и AN

Составитель А. Сиротская

Техред В.Кадар Корректор M. Максимишинец

Редактор Т. Кугрь|шева Гираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открьггий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 2135/49

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4