Устройство для сопряжения источника и приемника информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано для согласования скоростей при синхронной передаче данных от источника к приемнику информации. Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается, тем, что в устройст во, содержащее память, группу коммутаторов адреса, первые счетчики записи и чтения, два дешифратора , элемент И и элемент ИЛИ, введены вторые счетчики записи и чтения, триггер, две схемы сравнения и второй элемент И. I ил. с S (Л N9 N5 О) Ч оо

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

<511 4 606 f 13>

/ 3j (,.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2l) 3780150/24-24 (22) 13,08.84 (46) 23,04,86. Бюл. к- 15 (71) Дагестанский политехнический институт (72) О.М. Омаров (53) 681 ° 325 (088.8) (56) Авторское свидетельство СССР

В 752321, кл. С 06 F 3/04, 1978.

Авторское свидетельство СССР

Ф 746488, кл. G 06 F 3/04, 1977.

„„SU„„1226473 A (54)УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ИСТОЧ-

НИКА И ПРИЕМНИКА ИНФОРМАЦИИ (57)Изобретение относится к области вычислительной техники и может быть использовано для согласования скоростей при синхронной передаче данных от источника к приемнику информации.

Целью изобретения является повышение быстродействия устройства. Поставленная цель достигается, тем, что в устройство, содержащее память, группу коммутаторов адреса, первые счетчики записи и чтения, два дешифратора, элемент И и элемент ИЛИ, введены вторые счетчики записи и чтения, триггер, две схемы сравнения и вто- 8 рой элемент И. I ил.

l?26473

Изобретение относится к области вычислительной техники и может быть

45 использовано для согласования скоростей при асинхронной передаче данных от источника к приемнику информации.

Целью изобретения является повышение быстродействия устройства.

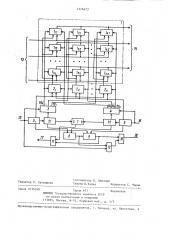

На чертеже представлена функциональная схема устройства.

Устройство содержит память l, коммуторы 2 адреса группы, дешифраторы

3 и 4, первые счетчики 5 и 6 записи и чтения, триггер 7, схемы 8 и 9 сравнения., элемент ИЛИ 10, элементы И 11 и 12, группы информационных входов

13 и выходов 14, входы 15 и 16 стробов записи и чтения, выходы 17 и 18 сигналов блокировки записи и чтения устройства, выходы 19 и 20 дешифраторов 3 и 4, вторые счетчики 21 и 22 записи и чтения. Память 1 содер>кит матрицу запоминающих модулей

1„„ 1„, с произвольной выборкой (Мх1).

Устройство работает следующим образом.

В исходном состоянии счетчики 5, 6, 21 и 22 и триггер 7 обнулены, выходы схем 8 и 9 сравнения возбуждены, по вьгходу 18 выдается сигнал блокирования чтения. Кроме того, выдаются единичные потенциалы по первым выходам 19 и 20 соответственно первого 3 и второго 4 дешифраторов, подготавливая каждый столбец к записи и чтению информации. При поступлении импульса записи по входу 15 стробируетсн дешифратор 3, при этом появляется единичный потенциал по первому выходу 19„ дешифратора 3, 4О который подключен к первому управляющему входу коммутатора 2 и моделей памяти к-го столбца. Далее содержимое счетчика 5 через первый информационный вход к-го коммутатора 2 поступает на адресные входы модулей памчти 1 к-ro столбца и первое слово, поступающее по входам 13, заносится в первую ячейку выбранных модулей. Переключаемый этим же импуль- 50 сом (по срезу) в следующее состояние счетчик 5 подготавливает занесение второго входного слова во вторую ячейку и т.д. до заполнения всех М ячеек модулей памяти к-го столбца. 55

В момент, когда модули окажутся заполненными, счетчик 5 переполнится, и импульс переполнения занесет едилицу B счетчик 21. 1!ри ..>том единич ный сигнал появится на втором 19э выходе 192 дешиф1>ато1>а 3, подготавляя для записи информапии (к — 1)-й столбец модулей памяти 1. Запись информации в другие модупи памяти

1 происходит аналогично.

Сразу после записи первого слова в первую ячейку к-ro столбца модулей памяти 1 с выхода 18 снимается сигнал блокировки чтения. Так как счетчики 6 и 22 находятся в "нулевом состоянии, первое слово будет считываться в приемник информации по первому адресу модулей памяти

1. к-ro столбца. Каждый импульс чтения, поступающий по входу 16, подготавливает адрес очередной ячейки этих модулей до момента считывания всех слов и переполнения счетчика

6, при этом импульс переполнения заносит единицу в счетчик 22. Далее единичный сигнал появится на (к-1)-м выходе дешифратора 4, подготавливая тем самым (к-!)-й столбец модулей памяти 1. Если запись и чтение информации производится из одних и тех же модулей памяти 1, то при записи чтение информации блокируется выдачей сигнала по выходу 18. Если запись и чтение информации производятся из разных модулей памяти 1, то пропессы записи и чтения можно производить одновременно. При полном заполнении памяти, т.е. при переполнении счетчика 21 устанавливается в единицу триггер 7, фиксирующий запись информации во все модули памяти 1. Далее запись информации вновь будет производится в модули к-го столбца, и если запись информации будет опережать чтение информации из памяти 1 и содержимое счетчиков 5, 21 станет равным содержимому счетчиков 6, 22, сработают схемы 8 и 9 сравнения, и выработается сигнал по выходу 17, служащий для блокировки записи информации в память 1.

Таким образом, устройство позволяет осуществлять запись и чтение информации в одни и те же модули памяти, не дожидаясь запись и чтение информации из разных столбцов модулей памяти, запись информации в ранее считанные ячейки памяти, не дожидаясь момента считывания всех слов из памяти, все это позволяет повысить быстродействие устройства.

1226 73

Кроме того, объем памяти устройства может достаточно просто изменяться без изменения его структуры путем исключения или добавления запоминающих модулей вместе с соответствующим коммутатором, частью счетчиков и дешифраторов.

Формула изобретения

Устройство для сопряжения источника и приемника информации, содержащее память, группы информационных входов и выходов которой являются соответственно группами информационных входов и выходов устройства, группу коммутаторов адреса, выходы которых подключены к группе адресных входов памяти, первые счетчики записи и чтения, тактовые входы которых соединены соответственно с входами стробов записи и чтения устройства, информационные выходы — соответственно с первыми и вторыми информационными входами коммутаторов адреса группы, первый и второй дешифраторы, выходы которых подключены соответственно к группам входов управления режимами записи и чтения памяти, первый элемент И, выход которого является выходом сигнала блокировки записи устройства, и элемент ИЛИ, выход которого является выходом сигнала блокировки чтения устройства, о тл и ч а ю щ е е с я тем, что, с 35 целью повышения быстроддиствия устройства, в него введены вторые счетчики записи и счетчик чтения, триггер, две схемы сравнения и второй элемент И, причем информационные выходы вторых счетчиков записи и чтения подключены соответственно к информационным входам первого и второго дешифраторов и первому и второму входам первой схемы сравнения, выход равенства которой соединен с первым входом второго элемента И и управляющим входом второй схемы сравнения, первым и вторым информационными входами подключенной соответственно к информационным выходам первых счетчиков записи и чтения, а выходы равенства к первым входам элемента ИЛИ и первого элемента И, второй вход которого соединен с выходом триггера, единичный и нулевой входы которого подключены соответственно к выходам переполнения вторых счетчиков записи и чтения, тактовыми входами соединенных соответственно с выходами переполнения первых счетчиков записи и чтения, стробирующий вход первого дешифратора соединен с входом строба записи устройства и вторым входом второго элемента И, выходом соединенного с вторым входом элемента ИЛИ, стробирующий вход второго дешифратора соединен с входом строба чтения устройства, выходы первого дешифратора подключены к первым управляющим входам коммутаторов адреса группы, вторые управляющие входы которых соединены с выходами второго дешифратора.!

226473

Составитель В. Вертлиб

Техред Я.Кадар Корректор С. Черни

Редактор Т. Кугрышева

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раутская наб., д. 4/5

Заказ 2135/49

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4