Формирователь импульсов

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и электроники и может быть использовано при построении устройств для считывания информации из накопителей запоминающих устройств в качестве элемента, осуществляющего предварительный подзаряд шин данных. Целью изобретения является расширение области применения устройства за счет обеспечения возможности формирования сигналов предварительного заряда как с исходного нулевого,уровня, так и с высокого уровня без предварительного обнуления подзаряжаемой шины. Формирователь работает в двух режимах: режим восстановления (подготовки) и режим формирования уровня подзаряда. 2 ил. с SS сл с

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (29) а>

<511 4 g 11 ?? 7>

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫИ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ (21) 3794655/24-24 (22) 28.09.84 (46) 23.04.86,Бюл. Н1 15 (72) С.Н.Косоусов, В.А.Максимов, Я.Я.Петричкович и B.Í.Ôèëàòoâ (53) 681.327(088 ° 8), (56) Патент Великобритании Р 2028044, кл. G 11 С 7/00, 1980.

Авторское свидетельство СССР

К - 1123056, кл. С 11 С 7/00, 1984. (54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ (57) Изобретение относится к области вычислительной техники и электроники и может быть использовано при построении устройств для считывания информации из накопителей запоминающих устройств в качестве элемента, осуществляющего предварительный подзаряд шин данных. Целью изобретения является расширение области применения устройства за счет обеспечения возможности формирования сигналов предварительного заряда как с исходного нулевого. уровня, так и с высокого уровня без предварительного обнуления подзаряжаемой шины. Формирователь работает в двух режимах: режим восстановления (подготовки) и режим формирования уровня подзаряда.

2 ил.

1226527

Изобретение относится к вычислительной технике и электронике и может быть использовано при построении устройств для считывания информации из накопителей запоминающих устройств в качестве элемента, осуществляющего предварительный подзаряд шин данных.

Целью изобретения является расширение области применения за счет обеспечения возможности формирования сиг- 10 налов предварительного заряда как с исходного нулевого уровня, так и с высокого уровня без предварительного обнуления подзаряжаемой шины.

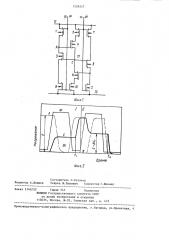

На фиг. 1 приведена схема формирова- 5 теля импульсов; на фиг.2 — кривые переходных процессов.

Формирователь импульсов содержит первый 1 транзистор р-проводимости, второй 2, третий 3, четвертый 4 тран- 2н зисторы п-проводимости, пятый 5, шестой 6, седьмой 7 транзисторы р-проводимости, восьмой 8, девятый 9, десятый lO транзисторы п-проводимости, шину )1 питания, шину 12 нулевого по- 25 тенциала, первую 13 и вторую 14 шины управления, выход 15.

Формирователь импульсов работает в двух режимах: режим восстановления (подготовки) и режим формирования уровня подзаряда.

В режиме восстановления (подготовки) на прямом и инверсном управляющих входах 14 установлен код, соответственно, Ф=О, Ф=1. При этом открытые первый 1 и второй 2 транзисто- З ры обеспечивают формирование в узлах

A u B уровней, соответственно, Е и О.

Закрытые пятый 5 и десятый 10 транзисторы отключают выход 15 от шины ,11 питания и общей шины 12, обеспечивая тем самым пассивное (третье) состояние выхода 15.

Смена управляющего кода 01 на противоположный 10 на входах 13 и 14 переводит схему в режим формирования подэаряда. В зависимости от состояния выхода 15 возможны два варианта переходного процесса: формирование подзаряда из нулевого состояния на выходе

15 — область 1 на фиг.2 и формирование подэаряда из единичного состояния на выходе 15 — область и на фиг.2.

В первом варианте переходного процесса открывающийся седьмой и открытый восьмой 8 транзисторы обеспечивают формирование в узле В логической единицы, закрывающей шестой транзистор 6. Открывающийся пятый 5 и открытый четвертый 4 транзисторы инициируют процесс повышения напряжения на выходе 15 схемы до уровня, определяемого соотношением где E — - напряжение на шине 11 питания относительно общей шины

12;

U,, — пороговое напряжение, коэффициент влияния подложки четвертого транзистора.

В случае,, если ЛБ ? U открываюО ) щийся третий 3 и открытый девятый 9 транзисторы обеспечивают формирование логического нуля в узле А, закрывающего четвертый транзистор 4. B случае, если ЬU < U „, что имеет место при выполнении условия

Š— 2

Uîï четвертый транзистор 4 закрывается по подложке и потенциал узла Й не изменяется.

Исходя из симметричности схемы, характер переходного процесса при формировании уровня подзаряда иэ единичного состояния (фиг.2, часть П) аналогичен рассмотренному, при этом уровень на выходе 15 определяется выражением

Еg +U,р Ð

) — О ор

1 + 1

Таким образом, в результате воздействия управляющих сигналов Ф=1, Ф=О на выходе 15 сформирован импульс о подзаряда, амплитуда которого и U

O находится в пределах Оа лП Е, причем в схеме отсутствуют сквозные токи, а выход 15 отключен от шин 11 питания и общей шины 12 закрытыми четвертым 4 и шестым 6 транзисторами.

Последуюшее изменение состояния управляющих .входов 13 и 14 на противоположное, соответственно Ф=О и Ф=1 обеспечивает сохранение уровня напряо жения йБ на выходе 15 эа счет сохранения его отключенного состояния посредством запирания десятого 10 и пятого

5 транзисторов. Воздействие в момент

t, внешнего импульса переводит выход

15 в состояние логической единицы (на фиг.2, часть 1) либо в состояние логического нуля.

1226527 где U „, — пороговое напряжение, коэффициент влияния подложки шестого 6 транзистора.

Воздействие внешнего импульса в момент с переводит выход 15 в нулевое (показано на фиг,2, часть П) состояние либо в единичное.

Таким образом, формирователь импульсов обеспечивает в течение активной фазы (Ф=1, Ф=О) функционирования подзаряд выходной емкости до промежуточного между логическим нулем и единицей уровня. Во время пассивной фазы (Ф=О, Ф=1) формирователь находится в третьем состоянии по своему выходу и не оказывает влияния на процесс формирования полных логических уровней внешними источниками.

Формула изобретения

Формирователь импульсов, содержащий первый транзистор р-проводимости, второй, третий и четвертый транзисторы п-проводимости, причем сток первого транзистора р-проводимости соединен с затвором четвертого и стоком третьего транзисторов п-проводимости, затвор третьего транзистора и-проводимости подключен к истоку четвертого транзистора п-проD водимости, исток и затвор первого транзистора р-проводимости соединены соответственно с шиной питания и первой шиной управления, исток и затвор второго транзистора и-проводимости соединены соответственно с шиной нулевого потенциала и второй шиной управления, о т л и ч а ю— шийся тем, что, с целью расширения области применения формирователя за счет обеспечения воэможности формирования сигналов предварительного заряда как с исходного нулевого уровня, так и с высокого уровня без предварительного обнуления подзаряжаемой шины, он содержит пя1О тьпу, шестой, седьмой транзисторы р-проводимости, восьмой, девятый и десятый транзисторы п-проводимости, причем истоки пятого и седьмого транзисторов р-проводимости соединены с шиной питания, а их затворы подключены к второй шине управления, сток пятого транзистора р-проводимости соединен со стоком четвертого транзистора п-проводимости, сток седьмого транзистора р-проводимости подключен к истоку восьмого транзистора п-проводимости, сток которого соединен с затвором шестого транзистора р-проводимости и стоком второго транзистора и-проводимости, затвор восьмого транзистора n"ïðîâoäèìîñòè соединен с истоком шестого транзистора р-проводимости, затвором третьего транзистора и-проводимости и является выходом формирователя, затвор девятого и

30 десятого транзисторов n-проводимости подключены к первой шине управления, а их истоки соединены с шиной нулевого потенциала, сток девятого транзистора и-проводимости подключен к истоку третьего транзистора п-проводимости, сток десятого транзистора и-проводимости соединен со стоком шестого транзистора р-проводимости.

1 22652.7

Составитель О.Кулаков

Редактор А.Шандор Техред И.Попович Корректор С.Шекмар

Заказ 2140/52 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г,,ужгород, ул.Проектная, 4