Т-триггер (его варианты)

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в различных пересчетных схемах. Цель изобретения - повышение быстродействия Т триггера - достигается функциональными связями между схемными элементами. Т- триггер по первому варианту содержит транзисторы 1-6, фиксаторы потенциалов 7 и 8, вход 9, дополнительный вход 10, источник тока 11, шины питания 12 и 13, шину опорного напряжения 14. Функциональная схема Т-триггера по второму варианту приводится в описании изобретения. Обратная связь между первой и второй бистабильныни ячейками осуществляется в первом варианте Т-триггера коллекторной связью транзистора.4 с базой транзистора 2. Триггеры имеют, по сравнению с прототипом , в 2 раза большую рабочую частоту и в 2 раза меньшее число составлякйцих элементов. 2 с.п. ф-лы. 2 ил. /3 i СЛ to ю 05 О ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

»«

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3800838/24-21 (22) 15.10.84 (46) 23.04.86. Бюл. № 15 (72) А.С. Сидоров (53) 62 1.374(088.8) (56) Патент Великобритании № 2036495, кл. Н 03 К 3/286, 1980Патент Великобритании ¹ 2085249, кл. Н 03 К 3/286, 1982, (54) Т-ТРИГГЕР (ЕГО ВАРИАНТ!11 (57) Изобретение относится к импульсной технике и может быть использовано в различных пересчетных схемах.

Цель изобретения — повышение быстродействия Т-триггера — достигается функциональными связями между схемными элементами. Т-триггер по пер(19ISU„, 122 15 (51)4 Н 03 К 3 286 вому варианту содержит транзисторы

1-6, фиксаторы потенциалов 7 и 8, вход 9, дополнительный вход 10, источник тока 11, шины питания 12 и

13, шину опорного напряжения 14.

Функциональная схема Т-триггера по второму варианту приводится в описании изобретения. Обратная связь между первой и второй бистабильными ячейками осуществляется в первом варианте Т-триггера коллекторной связью транзистора.4 с базой транзистора 2.

Триггеры имеют, по сравнению с прототипом, в 2 раза большую рабочую частоту и в 2 раза меньшее число составляющих элементов. 2 с.п. ф-лы.

2 ил.

1?266

Изобретение относится к импульсной технике и может быть использовано н различных пересчетных схемах.

Цель изобретения — повышение быстродействия Т-триггера. 5

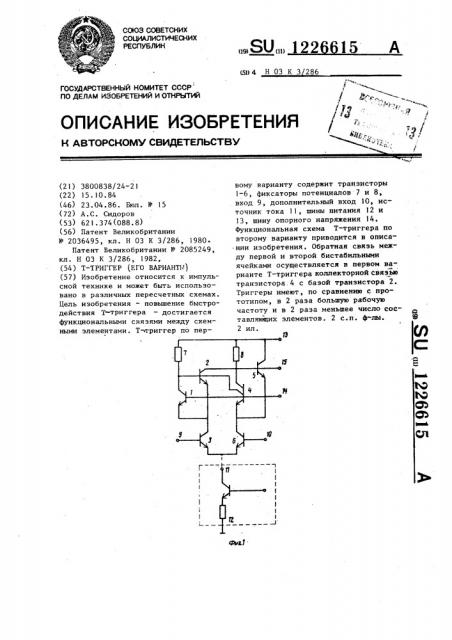

На фиг. l принедена электрическая схема Т-триггера, первый вариант; на. фиг,2 — то же, второй вариант.

Т-триггер (фиг.l) содержит транзисторы 1-6 и первый и второй фикса- !О торы 7 и 8 потенциала, эмиттеры первого и второго транзисторов соединены с коллектором третьего транзистора 3, база которого подключена к входу 9, база второго транзистора 2 !5 подключена к первому выводу первого фиксатора 7 потенциала, коллектор четвертого и база пятого транзисторов 4 и 5 подключены к первому выводу второго фиксатора 8 потенциала, 20 эмиттеры четвертого и пятого транзисторов 4 и 5 соединены с коллектором шестого транзистора 6, база которого подключена к дополнительному входу 10, а эмиттер через источник 25

11 тока соединен с первой шиной 12 питания, коллектор пято ro транзистора

5 соединен с второй шиной 13 питания, база четвертого транзистора 4 подключена к шине 14 опорного напряжения и к базе первого транзистора 1, коллектор которого подключен к первому выводу первого фиксатора 7 потенциала, вторые выводы первого и второго фиксаторов 7 и 8 потенциала подключены .Э«I к второй шине питания, эмиттер третьего транзистора 3 соединен с эмиттером шестого транзистора 6, а дополнительный коллектор четвертого транзистора 4 — с базой второго тран зистора 2, коллектор которого подключен к перному ныводу второго фиксатора 8 потенциала, и выход 15.

По второму варианту поставленная цель достигается тем, что Т-триггер 4 (фиг.2) содержит транзисторы 1-6 (транзисторы 1 и 6 днухэмиттерные), первый и второй фиксаторы 7 и 8 потенциала, первый эмиттер первого и эмиттер нторого транзисторов 1 и 2 соединены с коллектором третьего транзистора 3, база которого подключена к входу 9, коллекторо первого и база второго транзисторов 1 и 2 подключены к первому выводу первого фик- Ы сатора 7 потенциала, коллектор четвертого и база пятого транзисторов

4 и 5 объединены и подключены к пер15 ному выводу второго фиксатора 8 потенциала, эмиттер четвертого и эмиттер пятого транзисторов 4 и 5 соединены с коллектором шестого транэисто" ра 6, база которого подключена к дополнительному выходу 10, а эмиттер через источник 11 тока соединен с первой шиной 12 питания, коллектор пятого транзистора 5 соединен с второй шиной 13 питания, база четвертого транзистора подключена к шине 14 опорного напряжения и к базе первого транзистора 1, причем вторые выводы первого и второго фиксаторов 7 и 8 потенциала подключены к второй шине !

3 питания, второй эмиттер первого транзистора 1 подключен к коллектору шестого транзистора 6, эммитер которого соединен с эмиттером третьего транзистора 3, а коллектор второго транзистора подключен к первому выноду второго фиксатора 8 потенциала и выходу 15, второй эмиттер пятого транзистора 5 может быть подключен к дополнительному выходу 16.

Фиксаторы потенциала T òðèããåðà могут быть выполнены в виде резисторов (фиг,1 и 2), либо могут быть резистивно-диодными.

Варианты Т-триггера содержат дне бистабильные ячейки, каждая из которых реализована на основе двухступенчатого эмиттерно-функционального логического элемента.

На шину 14 подается потенциал с уровнем, расположенным посередине между уровнями логического нуля и единицей нерхнеи ступени двухступенчатых логических элементов.

Прямая связь между первой и второй бистабильными ячейками осуществляется коллекторной связью транзистора 2 с базой транзистора 5 °

Обратная связь между второй и первой бистабильными ячейками осуществляется н первом нарианте Т-триггера коллекторной связью транзистора 4 с базой транзистора 2, но втором варианте — эмиттерной связью транзистора

4 и транзистора

Т-триггер (фиг ° 1) работает следующим образом.

В исходном состоянии на входе 9 и дополнительном нходе 10 присутствуют логические уровни нижней ступени двухступенчатых логических элементов, соответственно уровень логического нуля и уровень логической единицы, 1226615 при этом транзистор 3 закрыт, а транзистор 6 открыт. Пусть в исходном состоянии открыт также транзистор 4.

Тогда ток источника 11 тока поступит через открытый транзистор 6 и далее через открытые эмиттер-коллекторные переходы транзистора 4, разветвляясь на два равных по величине, протекает через оба фиксатора 7 и 8 потенциала.

При этом на базах транзисторов 2 10 и 5 и на выходе 15 присутствует логический уровень верхней ступени двухступенчатого логического элемента— уровень логического нуля, транзистор

5 закрыт. Т-триггер находится в ну- 15 левом состоянии.

При подаче входного тактового сигнала на входе 9 устанавливается потенциал, соответствующий уровню логической единицы, а на дополнительном 20 входе 10 — соответствующий уровню логического нуля. Транзистор 3 отк— рывается, а транзистор 6 закрывается.

Поскольку в этот момент времени потенциал базы транзистора 2 (уро- 25 вень логического нуля) ниже потенциала базы транзистора 1 (уровень порогового напряжения), то транзистор 2 находится в закрытом, а транзистор 1 в открытом со"тоянии. 30

Ток, задаваемый источником 14 тока, протекает через открытые эмиттерколлекторные переходы транзисторов

3 и 4 и далее через фиксатор 7 по— тенциала, поддерживая на базе тран35 зистора 2 уровень логического нуля.

Поскольку грохождение тока через фиксатор 8 потенциала прекращается, то на базе транзистора 5 и на выходе 15 устанавливается уровень логической 40 единицы. Т-триггер переключается в единичное состояние.

После окончания входного тактового сигнала на входе 9 вновь устанавли- 45 вается уровень логического нуля, а на дополнительном входе 10 — уровень логической единицы. Транзистор 3 закрывается, а транзистор 6 открывается.

Поскольку в этот момент времени 50 потенциал базы транзистора 5 (уровень логической единицы) выше потенциала базы транзистора 4 (уровень порогового напряжения, то транзистор 5 находится в открытом, а транзистор 4 в 55 закрытом состоянии.

Ток источника 11 тока протекает через открытые эмиттер-коллекторные переходы транзисторов 6 и 5. При этом потенциал на базе транзистора 5 и на выходе 15 не изменяется. Т-триггер остается в единичном состоянии.

Поскольку прохождение тока через фиксатор 7 потенциала прекращается, то на базе транзистора 2 устанавливается уровень логической единицы.

При подаче следующего входного тактового сигнала вновь открывается транзистор 3 и закрывается транзистор 6.

В этот момент времени потенциал базы транзистора 2 (уровень логической единицы) вьппе потенциала базы транзистора 1 (уровень порогового напряжения), в результате транзистор 2 открыт, а транзистор 1 закрыт.

Ток источника 11 тока протекает через открытые эмиттер-коллекторные переходы транзисторов 3 и 2 и далее фиксатор 8 потенциала. На базе транзистора 2 сохраняется уровень логической единицы, а на базе транзистора 5 и выходе 15 устанавливается уровень логического нуля. Триггер возвращается в нулевое состояние.

После окончания входного тактового сигнала транзистор 3 закрывается, а транзистор 6 открывается.

Поскольку в этот момент времени потенциал базы транзистора 5 (уровен логического нуля) ниже потенциала базы транзистора 4 (уровень порогового напряжения), то транзистор 5 находится в закрытом, а транзистор 4 в открытом состоянии.

Ток потенциала источника 11 тока поступает через открытый транзистор

6 и далее через открытые эмиттерколлекторные переходы транзистора 4, разветвляясь на два равных по величине, протекает через оба фиксатора

7 и 8 потенциала.

При этом на базе транзистора 2 устанавливается, а на базе транзистора 5 и выходе 15 подтверждается потенциал, соответствующий уровню логического нуля. Т-триггер остается в нулевом состоянии.

По второму варианту Т-триггер (фиг.2) работает следующим образом.

В исходном состоянии на входе 9 и на дополнительном входе 10 присутствуют логические уровни нижней ступени двухступенчатых логических элементов, соответственно уровень логического нуля и уровень логической

1226615 единицы, при этом транзистор 3 закрыт, а транзистор 6 открыт.

Пусть в исходном состоянии открыт также и транзистор 4 и первый эмиттер-коллекторный переход транзистора З

1. Тогда ток источника 11 тока поступает через открытый транзистор 6 и далее, разветвляясь на два равных по величине, протекает через транзистор 4 и фиксатор 8 потенциала, а !

О также через первый эмиттерно-коллекторный переход транзистора 1 и фиксатор 7 потенциала.

При этом на базах транзистора 2 и 5 и на выходе 15 присутствует логический уровень верхней ступени двухступенчатого логического элемента — уровень логического нуля, транзистор 5 закрыт. Т-триггер находится в нулевом состоянии. 26

При подаче входного тактового сигнала на входе 9 устанавливается потенциал, соответствующий уровню логической единицы, а на дополнительном входе 10 — потенциал, соответствующий уровню логического нуля.

Транзистор 3 открывается, а транзистор 6 закрывается.

Поскольку в этот момент времени потенциал базы транзистора 2 (уро- 3Q вень логического нуля) ниже потенциала базы транзистора 1 (уровень порогового напряжения), то транзистор 2 находится в закрытом, а транзистор l в открытом состоянии. 35

Ток источника 11 тока протекает через открытый транзистор 3 и открытый второй эмиттерно-коллекторный переход транзистора 1 и далее через фиксатор 7 потенциала, поддерживая gp на базе транзистора 2 уровень логического нуля. Поскольку прохождение тока через фиксатор 8 потенциала прекращается, то на базе транзистора

5 и выходе 15 устанавливается уровень логической единицы. Т-триггер переключается в единичное состояние.

После окончания входного тактбвого сигнала на входе 9 вновь устанавливается уровень логического нуля, а на дополнительном входе 10 — уровень логической единицы. Транзистор 3 закрыт, а транзистор б открывается.

Поскольку в этот момент времени потенциал базы транзистора 5 (уровень 5 логической еджицы) выше потенциала базы транзисторов 1 и 4 (уровень порогового напряжения), то транзистор

5 находится в открытом, а транзистор

1 и 4 в закрытом состоянии, Ток источника тока протекает через открытые эмиттер-коллекторные переходы транзисторов 6 и 5. При этом потенциал на базе транзистора 5 и на выходе 15 не изменится. Т-триггер остается в единичном состоянии.

Поскольку прохождение тока через фиксатор 7 потенциала прекращается, то на базе транзистора 2 устанавливается уровень логической единицы.

При подаче следующего входного тактового сигнала вновь открывается транзистор 3 и закрывается транзистор б.

В этот момент времени потенциал базы транзистора 2 (уровень логической единицы) выше потенциала базы транзистора 1 (уровень порогового напряжения), в результате транзистор

2 открыт, а транзистор 1 закрыт.

Ток источника ll тока протекает через эмиттер-коллекторные переходы транзисторов 3 и 2 и далее через фиксатор 8 потенциала. На базе транзистора 2 сохраняется уровень логической ециницы, а на базе транзистора 5 и выходе 15 устанавливается уровень логического нуля. Т-триггер возвращается в нулевое состояние.

После окончания входного тактового сигнала транзистор 3 закрывается, а транзистор 6 открывается.

Поскольку в этот момент времени потенциал базы транзистора 5 (уровень логического нуля) ниже потенциала базы транзистора 4 (уровень порогового напряжения), то транзистор 5 находится в закрытом, а транзистор 4 в открытом состоянии.

Ток источника ll тока поступает через открытый транзистор 6 и далее, разветвляясь на два равных по величине, протекает через транзистор 4 и фиксатор 8 потенциала, а также через первый эмиттер-коллекторный переход транзистора l и фиксатор 7 потенциала.

При этом на базе транзистора 2 устанавливается, а на базе транзистора 5 и на выходе 15 подтверждается потенциал, соответствующий уровню логического нуля. Т-триггер остается в нулевом состоянии. Функциональное быстродействие Т-триггера определяет ся временем переключения двух бистабильных ячеек.

1226615

Таким образом, максимальная рабочая частота триггера F„«, =1/2 Т, где Т вЂ” среднее время переключения одной бистабильной ячейки. При этом каждый вариант Т-триггера реализован 5 на десяти элементах.

Исходя из особенности функционирования Т-триггера, заключающейся в том, что в момент времени между двумя входными тактовыми импульсами и при нулевом состоянии триггера ток источника тока одновременно протекает через оба фиксатора 7 и 8 потенциала, для достижения максимальных рабочих(частот должны выполняться определенные соотношения между временем переключения бистабильных ячеек, скважностью входных тактовых импульсов, величиной нагрузки на выходную клемму устройства. 20

Например, для реализации предельного быстродействия во втором варианте Т-триггера, при соответствующем конструктивном исполнении и когда выходной сигнал снимается с дополнительного выхода 16 устройства, когда у первой бнстабильной ячейки время переключения из единичного состояния в нулевое в полтора раза больше, чем у второй, а время пере- 30 ключения из нулевого состояния в единичное. у обеих бистабильных ячеек одинаково, скважность входных тактовых импульсов должна быть равна 2,5.

Такая скважность входных тактовых 35 импульсов может быть реализована, например, на входном дифференциальном усилителе-формирователе со сме-. щенным отсносительно постоянной составляющей входного синусоидального . 40 сигнала порогом срабатывания.

Нри работе Т-триггера в широком диапазоне входных тактовых частот от импульсного сигнала типа "меандр когда используются резисторные фик- 45 саторы потенциала, возникает модуляция амплитуды выходного сигнала бистабильных ячеек.

В тех случаях, когда этот эффект нежелателен, возможно исключение мо- 50 дуляции выходного сигнала Т-триггера путем подключения коллектора транзистора 2 к дополнительному выводу второго фиксатора потенциала, к средней точке фиксатора 8 потенциала. Для 55 этой цели можно использовать исключение прохождения части коллекторного тока транзистора 2 через фиксатор

8 потенциала путем подключения дополнительного второго коллектора транзистора 2 к второй шине 13 питания.

В первом варианте Т-триггера возможно исключение модуляции амплитуды выходного сигнала также и на выходе первой бистабильной ячейки. Для этого коллектор транзистора 1 должен быть подключен к дополнительному выводу первого фиксатора 7 потенциала (к средней точке фиксатора 7 потенциала).

Преимуществом предлагаемого триггера по сравнению с известным является его более чем в два раза большая максимальная рабочая частота. Это обусловлено в полтора раза более высоким функциональным быстродействием предлагаемого триггера, в два раза меньшим числом составляющих элементов и соответственно более простой конструкцией, что значительно снижает время переключения каждой бистабильной ячейки н повышает быстродействие

Т-триггера.

Формула и з о б р е т е н и я

1. Т-триггер, содержащий вход, выход, шесть транзисторов и два-фиксатора потенциала, эммитеры первого и второго. транзисторов соединены с коллектором третьего транзистора. база второго транзистора подключена к первому выводу первого фиксатора потенциала, коллектор четвертого транзистора соединен с базой пятого транзистора и подключен к первому выводу второro фиксатора потенциала, эмиттеры четвертого и пятого транзисторов соединены с колле- стором шестого транзистора, эмиттер которого через источник тока соединен с первой шиной питания, коллектор пятого транзистора соединен с второй шиной питания, база четвертого транзистора подключена к шине опорного напряжения и к базе первого транзистора, коллек. тор которого подключен к первому выводу первого фиксатора потенциала, отличающийся тем, что, с целью повышения быстродействия, вторые выводы первого и второго фиксато. ров потенциала подключены к второй шине питания, эмиттер третьего транзистора соединен с эмиттером шестого транзистора, дополнительный коллектор четвертого транзистора — с ба12266

10

)7 г1

I

I

1 (L

Составитель A. Янов

Редактор H. Тупица Техред Л.Олейник Корректор Е. Рошко

Заказ 2145/56 Тираж 8)6 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

ll3035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

9 зой второго транзистора, коллектор которого подключен к первому выводу второго фиксатора потенциала и выходу Т-триггера, а базы третьего и шестого транзисторов соединены соответственно с входами и дополнительным входом Т-триггера ° 2. T-триггер, содержащий вход, вьгход, шесть транзисторов и два фиксатора потенциала, первый эмиттер первого и эмитТер второго транзисторов соединены с коллекторам третьего транзистора, коллектор первого и база второго транзисторов подключены к первому выводу первого фиксатора потенциала, коллектор четвертого и база пятого транзисторов подключены к первому выводу второго фиксатора потенциала, эмиттер четвертого и эмиттер пятого транзисторов соединенъ1 с коллектором шестого транзистора, эмиттер которого через источник тока соединен с первой шиной питания, коллектор пятого транзистора соединен с второй шиной питания, база четвертого транзистора подключена к шине опорного напряжения и к базе первого транзистора, о т л и ч аю шийся тем, что, с целью повышения быстродействия, вторые выводы первого и второго фиксаторов потенциала подключены к второй шине питания, второй эмиттер первого транзистора подключен к коллектору шестого транзистора, эмиттер которого соединен с эмиттером третьего транзистора, коллектор второго транзистора подключен к первому выводу второго фиксатора потенциала и выходу Ттриггера, а база. третьего и шестого транзисторов соединены соответственно с входом и дополнительным входом

Т-триггера.