Запоминающее устройство для программируемого контроллера

Иллюстрации

Показать всеРеферат

Изобретение относится к области., вычислительной техники и может быть использовано при построении запоминающих устройств для программируемых контроллеров. Цель изобретения - упрощение устройства и повышение его информационной емкости. В устройстве используют только два формата: байтовый и битовый. Коммутатор адреса позволяет подавать на адресные входы блока памяти информацию с адресной шины либо непосредственно (байтовый формат) либо сдвинутую на три разряда (битовый формат). Получаемые в - последнем случае три разряда используются для управления дешифратором и выходным коммутатором данных с целью выбора только необходимых кристаллов в блоке памяти и коммутации на младший разряд блока двунаправленных ключей требуемого бита из байта4 1 ил. (Л с ю ю сх 4 аь

СО1ОЭ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК.

„„SU„;, 1228146 (59 4 С 11 С ll/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ Ь е Й

1 ил.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ ИОТНРЫТИЙ (21) 3720126/24-24 (22) 03.04.84 (46) 30.04.86. Бюл. N 16 (71) Всесоюзный ордена Трудового Красного Знамени научно-исследовательский проектно-конструкторский и технологический институт релестроения (72) Л.А.Андрианова, Н.А.Гаранин, А.В.Грннштейн и А.С.Крупко (53) 681 .327 .(088 ° 8) (56) Патент США У 3825907, кл. 340174, опублик. 1974 °

Авторское свидетельство СССР

У 526019, кл. С 11 С 11/00, 1974. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ДЛЯ

ПРОГРАММИРУЕМОГО КОНТРОЛЛЕРА (57) Изобретение относится к области,, вычислительной техники и может быть использовано при построении запоминающих устройств для программируемых контроллеров ° Цель изобретения - упрощение устройства и повышение его информационной емкости. В устройстве используют только два формата: байтовый и битовый, Коммутатор адреса позволяет подавать на адресные входы блока памяти информацию с адресной шины либо непосредственно (байтовый формат) либо сдвинутую на три разряда (битовый формат). Получаемые в . последнем случае три разряда используются для управления дешифратором и выходным коммутатором данных с целью выбора только необходимых крисИ таллов в блоке памяти и коммутации Е на младший разряд блока двунаправленных ключей требуемого бита из байта.

1228146

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ), и может быть использовано при построении ЗУ программируемых контроллеров, 5

Цель изобретения — упрощение и повьппение информационной емкости устройства.

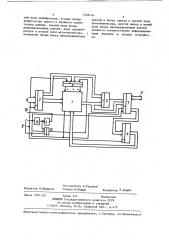

На чертеже изображена структурная схема запоминающего устройства для 10 программируемого контроллера.

Устройство содержит блок 1 памяти, формирователь 2 сигналов (явля1ощийся повторителем с открытым коллекторным выходом), коммутатор "3 адреса, вход- 15 ной 4 и выходной 5 коммутаторы данных, дешифратор 6, блок 7 двунаправленных ключей, адресную шину 8, образуемую адресным входом устройства, управляющую шину 9, образуемую управ- 20 ляющими входами устройства, управляющий выход 10, шину 11 данных, образуемую информационнымн входами и выходами устройства. Устройство также содержит одновибратор 12 и мультиплексор 13.

Блок 1 памяти построен на БИС ОЗУ с битовой организацией (например, КР537РУ2). Адресные входы и выходы

ЧТЕНИЕ/ЗАХП1СЬ БИС ОЗУ обьединены параллельно, а входы и выходы данных— поразрядно (не показаны). Все входы

ВЫБОР КРИСТАЛЛА БИС ОЗУ управляются раздельно. К адресным входам БИС ОЗУ подсоединен один из выходов коммутатора

3 адреса, к входам данных — выходы входного коммутатора 4 данных, к входам ВЫБОР КРИСТАЛЛА — выходы дешифратора 6, к входу ЧТЕНИЕ/ЗАЛИСЬ— один иэ управляющих входов устрой- 4р ства, к выходам данных — информационные входы выходного коммутатора 5 данных и, за исключением младшего разряда, входы блока 7 двунаправленных ключей. Блок 7 может быть пост- 45 роен на микросхемах К589АП16.

Принцип работы устройства заклю,чается в следующем.

Коммутатор 3 адреса позволяет в зависимости от используемого формата подавать на адресный вход блока 1 памяти информацию с адресной шины 8 либо непосредственно (байтовый формат), либо сдвинутую на три разряда (битовый формат). Получаемые в последнем случае три разряда используются для .управления дешифратором 6 и выходным коммутатором 5 данных с целью выбора только необходимых кристаллов в блоке 1 памяти и коммутации на младший разряд блока 7 двунаправленных ключей требуемого бита иэ байта. Три старших разряда адреса, поступающего на блок 1 памяти, в этом случае фиксированы, т.е. битовый доступ возможен только к.части всего массива памяти. Число адресуемых бит определяется разрядностью, адресной шины. При байтовом обращении на коммутатор 5 данных и дешиф" ратор 6 поступает с коммутатора 3 адреса фиксированный код для обеспечения коммутации на блок 7 байта полностью. Число адресуемых байт, таким образом, также определяется разрядностью адресной шины 8.

Таким образом организуется работа

ЗУ на двунаправленную шину 11 данных в асинхронных системах (т.е. работа по "отклику").

Формула изобретения

Запоминающее устройство для программируемого контроллера, содержащее блок памяти, входной и выходной коммутаторы данных и дешифратор, о т— л и ч а ю щ е е с я тем, что, с целью упрощения и повышения информационной емкости устройства, в него введены мультиплексор, одновибратор, формирователь сигналов, блок двунаправленных ключей и коммутатор адреса, первый вход которого является адресным входом устройства, один из выходов соединен с первым входом блока памяти, другой — с первыми входами дешифратора и выходного коммутатора данных, второй вход которого соединен с выходом блока памяти и первым входом блока двунаправленных ключей, второй вход блока памяти подключен к выходу входного коммутатора данных, первый вход которого соединен с одним из выходов блока двунаправленных ключей, выход одновибратора подключен к входу формирователя сигналов и первому входу мультиплексора, выход которого соединен с вторым входом дешифратора, выход которого подключен к третьему входу блока памяти, выход выходного коммутатора данных соединен с вторым входом блока двунаправленных ключей, выход формирователя сигналов является управляющим выходом устройства, управляющими входами которого являются соответственно тре1228)46

Составитель В.Рудаков

Редактор Н.1Пвыдкая Техред В. Кадар Корректор .Ро

Е.Рошко

Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Заказ 2291/52

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4 тий вход дешифратора, вторые входы коммутатора адреса и входного коммутатора данных, третий вход блока двунаправленных ключей, вход одновибратора и второй вход мультиплексора, четвертые входы блока двунаправленных

4 ключей и блока памяти и третий вход мультиплексора, другой выход и пятый вход блока двунаправленных ключей являются соответственно информационными выходом и входом устройства.