Делитель-счетчик многофазного кода (его варианты)

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой и преобразовательной технике и может быть использовано в электроприводах постоянного и переменного тока с цифровым управлением. Цель изобретения - повышение достоверности функционирования. Устройство содержит m RS-триггеров, от 1-1 до 1-т, блок 2 элементов И-НЕ, узел 3 исправления ошибок и узел 4 обнаружения ошибок многофазного кода, тактовые входы 5 и 6. В описании приведены структурные схемы и описаны два варианта выполнения, блок 2 элементов И-НЕ, при четном числе разрядов (т 4) и при нечетном числе разрядов (т 3). Приведен пример вьтолнения узла 3 исправления и узла 4 обнаружения ошибок многофазного кода для случая m 5. 2.с и 1 з.п. ф-лы, 4 ил., 1 табл. йя ffm i (Л N IsD 00 N О CO

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3529220/24-21 (22) 29.12.82 (46) 30.04.86. Бюл. N - 16 (72) В.И.Кочергин и С.В.Кульбицкий (53 ) 621.374.32 (088.8 ) (56 ) Пятлин А.А., Овсищер П.И., Лазер И.М. и др. Проектирование микроэлектронных устройств. M. Советское радио, 1977, 272 с.

Авторское свидетельство СССР

N 139715, кл. Н 03 К 23/02, 1961.

Hunt R.N., Kohli R.R. Decade

counter. Patent СВ 1041104, 25, 1964.

Авторское свидетельство СССР

351326 кл. Н 03 К 23/02, 1971.

Hilberg N. Die Eccles. JordanSchaltung mit Transistoren Fur sehr.

schelle Zahler. — Те1еХцпсКеп-Zeitung, 1960, Jg 33, Н 128.

Breic I "Ideally ГасС" decimal

counters with bistables. — IEEE, Transactions on Electronic comPuters, 1965, v. 14, № 5.

Jonson Counters even-and add

cycle length. — Electronic Fngineer, 1971. ¹ 9.

ÄÄSUÄÄ 1228269 А1 (5D 4 H 03 К 23/42, 21/40

Авторское свидетельство СССР

N - 834935, кл. Н 03 К 23/02, 1977 (54)ДЕЛИТЕЛЬ-СЧЕТЧИК МНОГОФАЗНОГО

КОДА (ЕГО ВАРИАНТЫ) (57)Изобретение относится к цифровой и преобразовательной технике и может быть использовано в электроприводах постоянного и переменного тока с цифровым управлением. Цель изобретения — повышение достоверности функционирования. Устройство содержит m RS-триггеров, от 1-1 до

1-m, блок 2 элементов И-НЕ, узел 3 исправления ошибок и узел 4 обнаружения ошибок многофазного кода, тактовые входы 5 и 6. В описании приведены структурные схемы и описаны два варианта выполнения, блок

2 элементов И-НЕ, при четном числе разрядов (m = 4) и при нечетном числе разрядов (m = 3). Приведен пример выполнения узла 3 исправления и узла 4 обнаружения ошибок многофазного кода для случая m = 5. 2 с и

1 з.п. ф-лы, 4 ил., 1 табл.

I 12

Изобретение относится к цифровой и преобразовательной технике и предназначается н основном для использования в электроприводах постоянного и переменного токов с цифровым управлением.

Варианты изобретения объединены единым замыслом, состоящим в обна3 ружении ошибки функционирования на каждом такте работы, и характеризуют особенности выполнения устройства при нечетном и четном числах разрядон.

Цель изобретения — повышение достоверности функционирования.

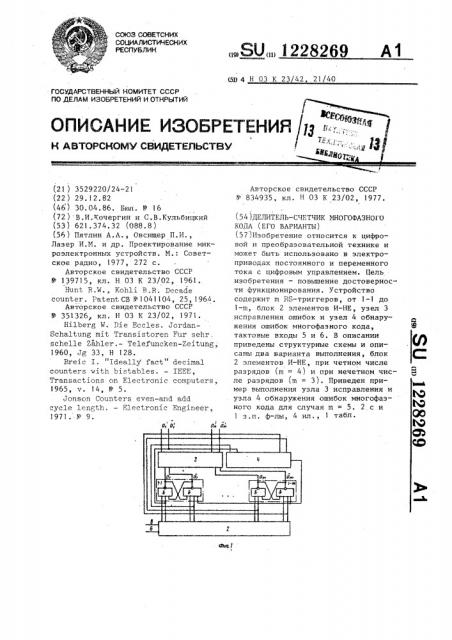

На фиг. 1 показана структурная схема делителя-счетчика многофазного кода; на фиг. 2 — пример выполнения блока элементов И-HE при нечетном числе разрядов (ш=3); на фиг. 3 — пример выполнения блока элементов И-НЕ при четном числе разрядов (ш=4); на фиг. 4 — пример выполнения узла исправления ошибок и узла обнаружения ошибок многофазного кода для случая m=5.

Делитель-счетчик многофазного ко-. да содержит m RH-триггеров, от 1-1 до 1-m, блок 2 элементов И-НЕ, узел 3 исправления ошибок многофазного кода и узел 4 обнаружения ошибок многофазного кода. Шины управления блока элементов И-НЕ являются тактовыми входами 5 и 6 делителясчетчика многофазного кода.

В устройстве по первому варианту блок 2 элементов И-НЕ содержит 2m двухвходоных элементов И-НЕ от 7-1 до 7-2m, и узел 3 исправления ошибок многофазного кода, содержащий

m групп двухвходовых элементов И (8-1)-(8 — 2т +1) по два в каждой группе, кроме первой, которая содержит три элемента И и m элементов ИЛИ (9-1)-(9m) выходы элементов И i-й. группы (i=1,2,3..., m) соединены с нходами i-го элемента ИЛИ, прямые и инверсные выходы элементов ИЛИ

9.-1 соединены с выходными шинами узла исправления ошибок многофазного кода, в блоке элементов И-HE npu

m=2K+1 (K=I 2,.„.) элементы И-НЕ объединены в две группы по элементов в каждой, первые входы элементов И-НЕ первой и второй группы соединены с первой и второй шинами управления соответственно, выход ,1-го элемента И-HE первой группы

28269

5

l5

55 (,1 =1,2„..., m-1) соединен с первым S-входом j +1-ro RS-триггера, выход m-ro элемента И-НЕ этой группы соединен с первым R -входом первого RS -триггера 1 — 1, выход g -го элемента И-НЕ второй группы соедиHPH с IIeрным Н входом,1+1-ro RSтриггера 1-,j+1, выход m — го элемен-та И-НЕ этой группы соединен с первым S-входом первого RH-триггера

1-1, В узле 4 обнаружения ошибок многофазного кода 2 входных шин соединены с прямыми и инверсными выходами узла 3 исправления ошибок многофазного кода, прямой и инверсный выходы i-! фазы делителя-счетчика многофазного кода соединены с вторыми соответственно R- и $-входами i-го BS-триггера 1 †и вторыми вхоцами i-x элементов И-НЕ первой и второй групп блока 2 элементов ИНЕ, выходная шина узла 4 обнаружения ошибок соединена с третьими Rвхоцами RS-триггера I-i в узле 3 исправления ошибок входы элементов

И первой группы соединены соответственно с прямым выходом первого и инверсным выходом m — ro, прямыми выходами первого 1-1 и второго 1-2, прямым выходом второго 1-2 и инверсным выходом m-ro RS-триггеров, 1-m, входы первого и второго элементов И каждой i+1-й группы, кроме последней,, соединены соответственно с выходами i+1-ãî и i+2-го, и i-го и i+2-го 1-i+2 RH-триггеров, а входы первого и второго элементов И последней группы соединены с прямым выходом m-го 1-m и инверсным выходом первого 1-1, прямым выходом m1-го 1-m-1 и инверсным выходом первого 1-1 BS-триггеров, прямой и инверсный выходы i-ro элемента ИЛИ

9-i являются соответствующими выходными шинами 10-1 i†-й " фазы делителя-счетчика многофазного делителя— счетчика.

В делителе-счетчике по второму варианту блок 2 элементов И-HE содержит 2m двухвходовых элементов И-НЕ от 7 — 1 до 7-m, узел 3 исправления ошибок многофазного кода, содержащий ш групп днухнходовых элементов

И (8-1) †(8-2m+1), по два в каждой группе, кроме первой, которая содержит три элемента И (8-1)-(8-3), и m элементов ИЛИ (9-!)-(9 †), выходы элементов И i-й группы соединены с входами i-го элемента HJIH 9-1, прямые и инверсные выходы элементов ИЛИ (9-1)-(9-m) соединены с выходными шинами узла исправления ошибок многофазного кода, в блоке 2 элементов И- 5

НЕ при m-2K первые входы m-х четных и m-x нечетных элементов И-НЕ соеди— иены с первой и второй шинами управления соответственно, выход i-го элемента И-НЕ соединен с первым t0

S-входом )+1-ro RS-триггера 1-j+I, выход m-го элемента И-HE соединен с первым R -входом первого RS-триггера l-l, выход m+j-го элемента ИНЕ соединен с первым В-входом j+) го !5

RS-триггера 1-)+1, выход 2ш-го элемента И-НЕ соединен с первым S-входом первого RS-триггера 1-1. 3 узле

4 обнаружения ошибок многофазного ко-. да 2m входных шин соединены с прямыми и инверсными выходами узла 3 обнаружения ошибок многофазного кода, прямой и инверсный выходы -й фазы делителя-счетчика многофазного кода

25 соединены соответственно с вторыми

R- и 8-входами i-го RS-триггера

1-i и первыми входами i-го 7-i u

m+i-ro 7-m+i элементов И-HE соответственно, выходная шина узла 4 обнаружения ошибок многофазного кода соединена с третьими R-входами RS-триггеров 1-1, в узле 3 исправления ошибок многофазного кода входы элемептов И 8-1, 8-2 и 8-3 первой группы соединены с прямым вы- 35 ходом первого 1-1 и инверсным выходом п -го 1-!и, прямыми выходами перво1 "о l-l и второго 1-2, прямым выходом второго 1-2 и инверсным выходом m-го 1-m Ж-триггеров соот40 ветственно, входы первого и второго элементов И каждой +1-й группы, кроме последней, соединены i+1 и

i+2, i и i+2 x RS-триггеров соответственно, а входы первого и второ- 45 го элементов И последней группы соединены соответственно с прямым выходом tn-го и инверсным выходом первого 1-1., прямым выходом m-1-го

1-m-1 и инверсным выходом первого

1-m RS-триггеров, прямой и инверсный выходы i-х элементов ИЛИ 9-i ° соединены с выходными шинами 10 — i, -й фазы делителя-счетчика много-фазного кода. 55

Узел 4 обнаружения ошибок многофазного кода содержит rn элементов

И оТ !1 †до !! — г„, имеющий -, †входов каждый, выходи которых соединены с входами п -входового элемента ИЛИ 12, выход которого соединен с выходной шиной узла обнаружения ошибок многофазного кода.

Предлагаемый делитель-счетчик многофазного кода работает следующим образом.

Перед рассмотрением работы всего устройства остановимся первоначально на работе блоков исправления и обнаружения ошибок, которая основана на распознавании непрерывности множеств сигналов 0 и 1 многофазного кода. Рассматривая замкнутый ряд сигналов многофазного кода нетрудно увидеть, что здесь содержится только два непрерывных и неизменных по длине множества сигналов: множество сигналов 0 и мно жество сигналов 1. Например, пятифазный код для цифры обычного кода "0"

4 представляется этими множествами в следующем виде: 0 0 0 0 0 1 1 1 1 1 а для цифры "1" — в виде

1 0 0 0 0 0 1 1 1 1- и т.д..

При записи многофазного кода ограничиваются только первыми сигналами из этого ряда (таблица).

Аргументы

v 0

М1 а, Мд

Методика обнаружения и исправления ошибок многофазного кода в блоке

3 основана на распознавании непрерывности этих двух множеств: появление в множестве однотипных сигналов инверсного к ним сигнала, когда он отстоит от края множества на два сигнала и более воспринимается как стопроцентная ошибка. Например, при

5 1228269 эквивалентной цифре 1 появление сигнала а„=l должно„восприниматься, какоп1ибка 00100 ! 0

В I àáëèöå поясняется работа llQ исправлению, например, одиночных ошибок многофазного кода, и показано значение исправленного сигнала фазы

d в зависимости от сигналов сосед1 них фаз d; „,d . „, которые являются аргументами логической функции.

В соответствии с методикой при нулевьгх сигналах фаз Р,Б -триггеров

a,„ =.О, а,, =О независимо от значения сигнала фазы на выходной шине б1. сигнал на выходе делителя1 счетчика для этой фазы должен быть нулевым (d = О, первая строка таблицы). Аналогично при наличии сигналов фаз a,, = 1, а., = 1 независимо от значения сигнала а сигнал на вьгходе делителя-счетчика должен быть равен единице, а, =-1 (последняя строка таблицы). Если обозначить множество значений сигналов d.; когда сигал а должен передаваться 25 без изменения через И, то в соответствии с правилами логики получим

1 значение исправленного сигнала . а, =d„. a ., 7М„а,. Вместо множества

И! можно использовать множество 30

М,(N, N,), которое содержит все сочетания сигналов Я .. . а, кроме значения первой строки таблицы, К =

=- а.. Л, тогда — 1 11а! ные ошибки при расстоянии между ними в два сигнала и более, например

- ак, . орк--, — -й — -, 1110110110010010

Тогда блок 3 в соответствии с рассмотренной методикой исправит все оциночные ошибки d - 1, a. -" 1,,1,,- 0, I1 - О и сигналы на выход1 l0 ных шинах фаз d, — бг.„ будут соответствовать многофазному коду. Эти сигналы установят все BH-триггеры, воздействуя на их вторые входы, в устойчивые состояния многофазного !

5 кода. Все это время на выходе блока

4 будет существовать сигнал A =l.

BH-триггеры устанавливаются в рп одно из (2 — 2 рай!) состояний, когда в коде фаз cl„ — 01„, имеются одиноч20 ные ошибки при расстоянии между ними в один сигнал, например для предельного случая

В блоке 3 совершаются состязания": сигналы d, и и стремятся установить Х, 1, а сигналы 3., и В,— .=1. †. 0 и т.д.. Развитие процесса зависит при этом от соотношения времен переключения RS-триггеров. Поскольку в это время сигналы фаз Л

1 не соответствуют многофазному коду, то на выходе блока 4 будет сигнал j "-О, который устанавливает все 1<Н-триггеры в исходное, например нулевое состояние многофазного кода.

RS-триггеры устанавливаются в одно из (2 — 2 гл ) состояний, когда в коде фаз 01„— 1, имеются пачки ошибок, например

Д =а,ск,,1VD д,1 ;

1 35 что соотгетствует логической структурной схеме блока 3.

Рассмотрение работ всего устройства начнем с момента подачи питаю- !0 щего напряжения, когда на входы 5 и

6 не поступают тактовые импульсы.

При этом возможны четыре случая установки В 0-триггеров делителя-счетчика. 45

RS -триггеры устанавливаются в одно из 21-л состояний, которые полностью соответствуют одиночным циф рам обычного кода. В этом случае блок 3 пропускает сигналы фаз a,—

d без каких-либо изменений на вы—

1 та 1 ходные шины фаз 00.„ — 8, . При этом на выходе блока 4 выдается сигнал

1=1.

Блок 3 не может исправлять этот тип ошибок и поэтому на выходных шинах

cl„ — А будет эта же комбинация сигналов фаз, а на выходе блока 4 будет

50 сигнал A =0, который установит все

Р,Н -триггеры в исходное состояние.

В любом случае при подаче питания все RH -триггеры устанавливаются в положения мггогофазного кода. При по-55 очередном поступлении «а входные ши™ ны 25 импульсов Ы и !3 ггБ-триггеры совершают переключения в установленном порядке для суммирования либо

ББ-триггеры устанавливаются в одно из (2 — 2 ) состояний, когда

tn в коде фаз Л„ — д имеются одиноч0 1 0 1 0 1 0 0 1 0 1 Ñ 1 0

1 l 1 О О 1 1 О О О О О О 0 О.

1228269 вычитания этих импульсов. При этом всевозможные помехи, которые могут, например, поступая по цепям питания, переключать 1Е-триггеры делителясчетчика, подавляются блоком 3 и не позволяют помехам переключить RSтриггеры в нерабочие состояния.

Формула изобретения

30

1. Делитель-счетчик многофазного кода, содержащий m RS — триггеров, блок элементов И-НЕ, содержащий 2гп двухвходовых элементов И-НЕ, узел исправления ошибок многофазного кода, 15 содержащий гп групп двухвходовых элементов И, по два в каждой группе, кроме первой, которая содержит три элемента И и т элементов ИЛИ, выходы элементов И i-й группы (i — 1,2,3..., m) соединены с входами -го элемента ИЛИ, прямые и инверсные выходы элементов ИЛИ соединены с выходными шинами узла исправления ошибок многофазных кодов, в блоке элементов И-НЕ при m=2K+1 (К=1,2...,) элементы И-НЕ объединены в две группы по г элементов в каждой, первые входы элементов И-НЕ первой и второй группы соединены соответственно с первой и второй шинами управления, выход . -го элемента И-НЕ первой группы (1 = 1,2..., m 1) соединен с первым S †вход .j +1 — го RS -триггера, выход гт -го элемента И-НЕ этой группы соединен с первым R -входом первого RS -триггера, выход J --ro элемента И-НЕ второй группы соединен с первым R -входом 1 +1-го Я-триггера, выход rn -го элемента И-НЕ этой 40 группы соединен с первым S -входом первого 1 -триггера, о т л и ч а ю— шийся тем, что, с целью повышения достоверности функционирования в делитель-счетчик многофазного кода 45 введен узел обнаружения ошибок многофазного кода, 2 " входных шин которого соединены с прямыми и инверсными выходами узла исправления ошибок многофазного кода, прямой и инверсный выходы -й фазы делителя-счетчика многофазного кода соединены с вторыми соответственно R- и $-входами i -ro RS -триггера и вторыми вхо— дами i -х элементов И-НЕ первой и 55 второй групп блока элементов И-НЕ, выходная шина узла обнаружения ошибок соединена с третьими R -входами

ЙБ -триггеров, в узле исправления ошибок входы элементов И первой группы соединены соответственно с прямым выходом первого и инверсным выходом m-го, прямыми выходами первого и второго, прямым выходом второго и инверсным выходом m-ro RS-триггеров, входы первого и второго элементов И каждой i+1-й группы, кроме последней, соединены соответственно с выходами +1-ro и i+2-го, и i — го и

i +2-го 1 8 -триггеров, а входы с прямым выходом гп -го и инверсным выходом первого, прямым выходом чI-ro и инверсным выходом первого

RS-триггеров, прямой и инверсный выходы i --го элемента ИЛИ являются соответствующими выходными шинами -й фазы делителя-счетчика многофазного делителя-счетчика.

2. Делитель-счетчик многофазного кода, содержащий m RS-триггеров, блок элементов И-НЕ, содержащий

2 пдвухвходовых элементов И-НЕ, и узел исправления ошибок многофазного кода, содержащий rn групп двухвходовых элементов И, по два в каждой группе, кроме первой, которая содержит три элемента И, и т элементов ИЛИ, выходы элементов И i --й группы соединены с входами i -ro элемента ИЛИ, прямые и инверсные выходы элементов ИЛИ соединены с выходными шинами узла исправления ошибок многофазного кода, в блоке элементов И-НЕ при г =2К первые входы т -х четны. и п-х нечетных элементов И-НЕ соединены соответственно с первой и второй шинами управления, выход i --ro элемента И-НЕ соединен с первым S -входом +1-ro " -триггера, выход rn -го элемента И-НЕ соединен с первым к -входом первого

R -триггера, выход m+j-ro элемента И-НЕ соединен с первым R -входом j +1 — го "S-триггера, выход 2 -ro элемента И-HE соединен с первым

$-входом первого RS -триггера, о тл и ч а ю шийся тем, что, с целью повышения достоверности функционирования, в делитель †Счетч многофазного кода введен узел обнаружения ошибок многофазного кода, 2 w входных шин которого соединены с прямыми и инверсными выходами узла обнаружения ошибок многофазного кода, прямой и инверсный выходы

i é фазы делителя-счетчика многофаз1228269

20 ного кода соединены соответственно с вторыми R- и Б-входами i-го RSтриггера и первыми входами соответственно i-го и т+ -го элементов

И-НЕ, выходная шина узла обнаружения ошибок многофазного кода соединена с третьими R,--входами RS-триггеров, в узле исправления ошибок многофазного кода входы элементов И первой группы соединены соответственно с прямым выходом первого и инверсным п -го, прямыми выходами первого и второго, прямым выходом второго и инверсным п-го RS-триггеров, входы первого и второго элементов И каждой +1-й группы, кроме последней, соединены соответственно i+1 и

i+2, i и i+2-х RS-триггеров, а входы первого и второго элементов

И последней группы соединены соответственно с прямым выходом ш-го и инверсным выходом первого, прямым выходом m-1-го и инверсным выходом первого RS-триггеров, прямой и инверсный выходы i-х элементов ИЛИ соединены с выходными шинами i-й фазы делителя-счетчика многофазного кода.

3. Делитель-счетчик по пп.1 и 2, отличающийся тем, что узел обнаружения ошибок многофазíîro кода содержит m элементов И, имеющий

m-1 входов каждый, выходы которых соединены с входами m-входового элемента ИЛИ, выход которого соединен с выходной шиной узла обнаружения ошибок многофазного кода, входы

i-ro элемента И соединены соответственно с 2i -1,2i, 2i +1,...,2i +

+ m- 3-и выходами узла исправления ошибок многофазного кода.

12282б9

Составитель О. Скворцов

Техред И.Верес Корректор Т.Колб

Редактор Т. Митейко

Заказ 2297/58

Тираж 816

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4