Арифметическое устройство

Иллюстрации

Показать всеРеферат

Со!оэ Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Е,л. 42m, 14

Заявлено 10.Ill.1959 (№ 621645/26) с присоединением заявки ¹

1!1ПК G 060

iËÊ

Приоритет

Опубликовано 17.XI.1966. Бюллетень № 23

Дата опубликования описания 1.1.1967

Комитет по делам иэобретений и открытий при Совете Министров

СССР

Автор изобретения

Н. Н. Бородин

Заявитель

АРИФМЕТИЧЕСКОЕ УСТРОЙСТБО

Арифметические устройства, выполняющие операцию умножения, известны. Основной недостаток подобных устройств заключается в том, что операция умножения требует значительного времени. Это отрицательно сказывается на быстродействии машин. Значительное сокращение времени выполнения умножения в известных устройствах достигается одновременной расшифровкой значений пар разрядов множителя, но это значительно усложняет арифметическое устройство вычислительной машины.

Предлагаемое устройство обеспечивает сокращение времени необходимого для выполrIPIIHsI операции умножения без значительного усложнения арифметического устройства. Это достигается применением в электронной вычислительной машине параллельного действия логической схемы для выработки управляющих импульсов при расшифровке значений пар разрядов множителя.

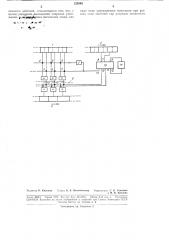

Скелетная схема устройства приведена на чертеже, где даны следующие обозначения:

1 — регистр множимого, 2 — регистр множителя, 8 — регистр произведения, 4 — логические устройства «ИЛИ», 5 — логическая схема «НЕТ», 6 — вентили, — цифра, соответствующая младшему из пары разрядов вшожителя, на который производится у»liomeние, 8 — цифра, соответствующая старшему из пары разрядов множителя, 9 — единица переноса, возникающая в результате предшествующего такта частичного произведения, 10 — переключательная функция, по призна5 ку которой и частичному произведению прибавляется произведение множпмого на 2", 11 — перекл!Очательная функция, пo признаку которой и частичному произведению прибавляется произведение множимого íà 2l, 10 12 — единица переноса в старший разряд

;;II0liaIzeля, 18 — переключающая функция, lIo признаку которой к частичному произведешно прибавляется произведение множимого на 2" в прямом плп в обратном ходе, 14—

15 цепь задсржки на время одного такта, 15— логическая схема для выработки управляющих импульсов.

Используя устройства «ИЛИ» и подавая через них на сумматор в прямом или обратном

20 коде произведение хшожнмого на 2- или толь .0 В IlРЯМОХ! !.ОДЕ ПР01!ЗВЕДЕ!ШЕ МНОЖИМОГО на 2, прснзводяг умноже:ше одновременно на дьа разряда хшожнтеля за один такт. Прп этох! СДВНГ х!НОЖнтеля li I2CTII IIIOI 0 IlpOII3BP.25 дения должен осуществляться одновременно на дьа разряда.

Предмет изобретения

Арифме!нческое устройство для электроп30 ной цифровой вычнслпгельной машины парал122948 ф»,. вФ

Редактор P. Киселева Тскред А. А. Камышникова Корректоры: С. Н. Соколова и В. В. Крылова

Заказ 390671 Тираж 1075 Формат бум. ВОУ90 бв Объем 0,13 изд. л. Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Центр, пр. Серова, д. 4

Типография, пр. Сапунова, 2 лельного действия, отличаюш1ееся тем, что, с целью..ускоруниялыполнения операции умножения, у,.неэуу1 Щнена логическая схема для чф и«« «Ф в „.Ф . pg 4 вырг. отки управляющих импульсов при рас.

u»«(овкe з»аче»ий пар разрядов множителя.