Устройство сравнения импульсных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматическому регулированию и может быть использовано для получения информации о разности двух сравпиваемы.х сигналов, иричем с одного выхода устройства поступает информация о коде модуля разности амплитуд сравниваемых сигналов, а с другого вы- .хода - информация о знаке разности. Устройство содержит первый 1 и второй 2 блоки памяти, первый 3, второй 4 и третий 5 компараторы, первый 6 и второй 7 управляемые источники тока, второй элемент И 8, элемент 9 задержки, триггер 10, элемент 11 антисовпадения, первый элемент И 12, генератор 13 кодовой частоты, первый 14 и второй 15 источники импульсов. Наличие элементов 2-11, 13, 15 позволяет с первого выхода устройства получать цифровой код модуля разности амплитуд сравниваемых импульсов, а на втором выходе устройства , с выхода третьего 5 компаратора, получать информацию в логической форме о знаке разности амплитуд сравниваемых ИМПУЛЬСОВ. 2 ил. (Л ю N3 СО 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 G 05 В 1 03

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, К А BTOPCHOMY СВИДЕТЕЛЬСТВУ офиг. /

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3775279/24-24 (22) 24.07.84 (46) 07.05.86. Бюл. ЛЪ 17 (71) МГУ им. М. В. Ломоносова (72) H. Н. Баламатов и А. А. Социленков (53) 62 50 (088,8) (56) Авторское свидетельство СССР

¹ 424106, кл. G 05 В 1/03, 1972.

Anторское свидетельство СССР

Л0 506120, кл. Ci 05 1/03, 1977. (54) УСТРОЙСТВО СРАВНЕНИЯ ИМПУ:1ЬСНЫХ СИГНАЛОВ (57) Изобретение относится к автоматическому регулированию и может быть использовано для получения информации о разности двух сравниваемых сигналов, причсм с одного Bnlxo. tn устройства поступает информация о коде модуля разности амплиÄÄSUÄÄ1229718 A 3 туд сравниваемых сигналов, а с другого выхода — информация о знаке разности.

Устройство содержит первый 1 и второй 2 блоки памяти, первый 3, второй 4 и третий 5 компараторы, первый 6 и второй 7 управляемые источники тока, второй элемент И 8, элемент 9 задержки, триггер

10, элемент 11 антисовпадения, первый элемент И 12, генератор 13 кодовой частоты, первый 14 и второй 15 источники импульсов.

Наличие элементов 2 в ll, 13, 15 позволяет с первого выхода устройства получать цифровой код модуля разности амплитуд сравниваемых импульсов, а на втором выходе устройства, с выхода третьего 5 компаратора, получать информацию в логической форме о знаке разности амплитуд сравниваемых импульсов. 2 ил.

1229718

Изобретение относится к автоматическому регулированию и управлению теxlIHческой кибернетики и может быть Hclloël,— зовано в цифровой измерительной техник(, электронике, экспериментальной фпз!(к«.

Целью изобретения является раси!и р(н,l( функциональных возможностей устройс гB<1 путем определения знака разности ам!)литуд импульсов и повышение надежности функционирования при одновременно поступагсщих импульсах.

>О

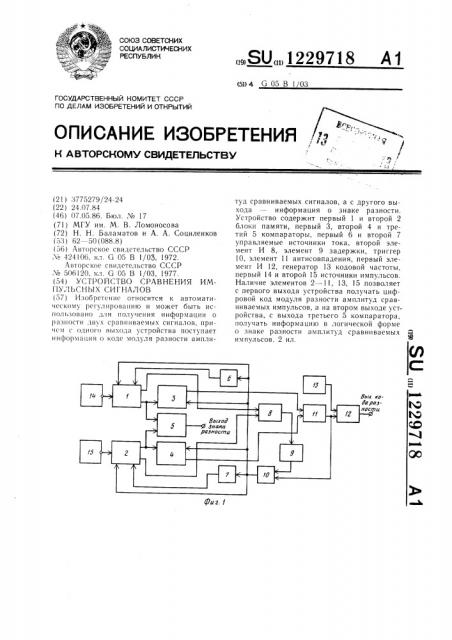

На фиг. 1 показана структурная схема предлагаемого устройства; на фиг. 2 — временные диаграммы, поясняк)щис его работу.

Устройство содержит первый I и второй 2 блоки памяти, первый 3, второй 4 и третий 5 1, компараторы, первый 6 и второй 7 i llp

Первый 1 и второй 2 блоки памяти являются амплитудными пиковыми детекторами, помимо информационного входа, перBbIM H BTOpblill ) Hp3B 1HIOllIH i1H ВХОд3хlи. Управляемые источники 6 и 7 тока являются источниками стабильного тока.

Устройство работает следующим образом.

Поступающие на входы первого и второго 2 блоков памяти сигналы UI> т U,5 заряжают емкость этих блоков до амплитуды импульсов. В момент окончания их заряда блоки 1 и 2 памяти вырабатьпзают логические сигналы U l и U), поступаю(цпе на входы второго элемента И 8. При совпадении во времени Lll и U) второй элемент

И 8 генерирует сигна„3 U, который через З задержку t;l устанавливает в «1» триггер

10. Логический потенциал !. 1(> с входа триггера 10 осуществляет следую!цие функции: блокирует Ilo первым входам блоки 1 и 2 памяти, подключает первый 6 и второй 7 управляемые источники тока для заряда емкос- 40 тей С и С, снимает блокировку компараторов 3 и 4. С этого момента происходит стадия линейного разряда С1 и С> стабильным !Оком I p, O исходного состо<1ни я. В т(чение разряда емкостей компараторы 3 и 4 вырабатывают на выходе логические сигналы

U1 и U.l длительностью tl и 1>, поступающие на входы элемента 11 антисовпадения. Элемент 11 антисовпадения Bblдаст на выходе импульс L l l длительностью t. = tl — t . И1:тервал t пропорционален измеряемой раз— ности амплитуд двух импульсов. Затем

1!реобразуется элементом И 12 и генерато;, >и )3 кодои>й частоты в числовой после,(ов(1 г(льный код. Спадом сигнала (з(1 с вы. <>да элемента 11 31г1 и(;)3113!CIIHH триггер

I I I BoBBp3Ll(3(TcsI В н,,зс ВоР нсхо (но(состояи (е. Н3 этом цикл измерения закан !ивается.

Устройство позволяет получить результат измерения непосредственно в цифровом ниде, что дает возможность HcllOëüçîâàòü его в автоматизированных системах управления и регул ирования, экс пер и мента I bHbl x системах регулирвания технологическими процесc3ми и цифровой измсрп ге IbHÎH I p>.HHêp с поп мене н нем ЭВМ. Оно позвол яст lloëó÷ àòü результаты измерения с точностью дo 1-О, I, >.

Фор,!!у.!и и-!Ой р(.тeии!

Устройство сравнения импульсных сигналов, содержащее первый источник импульсоВ, соедин HHbIH с информационным входом первого блока памяти, второй источник импульсов и первый элемент И, выход которого является первым выходом устройства, отли<(а>ои(ее(з! тем, что, с цельк> расширения функциональных возможностей путем определения знака разности амплитуд импульсов и повып>ения i13дежп()сти (!>ункционирования при одновремеш!о поступающих импульсах, в него введены второй блок памяти, псрвь!й и ВТорОН управляемые источники тока, второй элемент И, элсмсHT задержки, триггс р, элемент антисовпадения, генератор кодовой частоты, первый, второй и третий компараторы, выход последнего является вторым выходом устройства, а первый и второй входы соединены с вторыми входами и аналоговыми выходами соответственно первого и второго компараторов и первого и второго блоков памяти, логические выходы которых соединены с соответствующими входами второго элемента И, выход которого ч(рез последовательно соединенные элемент задержки и триггер соединен с первыми входами первого и второго блоков памяти и первого и второго компараторов непосредственно и через первый и второй управляемые источники тока с вторыми входами соответственно первого и второ(о блоков памяти, информационный вход последнего соединен с вторым источником импульса, первый вход первого элемента И соединен с выходом элемента антисовпадсния и вторым входом триггера, а второй вход с выходом генератора кодовой частоты.

Составитель h. Кирсанов

Редактор О. Юрковецкая Тс крея И. Всрес Корректор F.. Рошко

Заказ 2228 14 7 Тираж 836 11одниснос

ВНИИПИ Государственного комитета СССР

llo делам изобретений и оз крытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 415

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4