Цифровой релейный коррелятор

Иллюстрации

Показать всеРеферат

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для построения релейных корреляторов , определяющих оценку взаимной корреляционной функции двух сигналов. Цель изобретения - расширение динамического диапазона релейного коррелятора при незначительном усложнении устройства - достигается за счет введения в известное устройство двух групп элементов И, группы элементов ИЛИ и трех групп триггеров с соответствующими функциональными связями . 1 ил. tsD Ю СО VI а

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

158 4 С 06 F 15/336

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ /1,:;

К А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 3773988/24-24 (22) 23.07,84 (46) 07.05.86. Бюл. 11- 17 (71) Акустический институт им. акад.

Н.Н. Андреева и Приборостроительный занод им. 50-летия Киргизской ССР (72) В.П. Абрамович, В.Б. Дычаковский, Г.Ф. Страутманис, Г.Н. Щербаков и И.И. Якимович (53) 681.3(088.8) (56) Анторское свидетельство СССР

1"- 942038, кл. G 06 F 15/336, 1980.

Авторское свидетельство СССР

Р 1130875, кл. G 06 F 15/336, 1984.

„.SU,» 1229776 А1 (54) ЦИФРОВОЙ РЕЛЕЙНЫЙ КОРРЕЛЯТОР (57) Изобретение относится к специализированным средствам вычислительной техники и может быть использовано для построения релейных корреляторов, определяющих оценку взаимной корреляционной функции двух сигналов.

Цель изобретения — расширение динамического диапазона релейного коррелятора при незначительном усложнении устройства — достигается за счет введения н известное устройство двух групп элементов И, группы элементов ИЛИ и трех групп триггеров с соответствующими функциональными связями. 1 ил. Ж

1229776

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано"для построения релейных корреляторов„ определяющих оценку взаимной корреля- 5 ционной функции двух сигналов.

Цель изобретения — расширение динамического диапазона релейного коррелятора при незначительном усложне-. нии устройства. !О

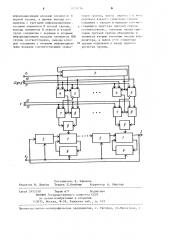

На чертеже изображена структурная схема релейного коррелятора.

Коррелятор содержит ь1 сумматоров 1, регистров 2, регистр 3 сдвига, первую 4, вторую 5 и третью 6 группы триггеров, первую 7 и вторую 8 группы элементов И, группу элементов ИЛИ 9, вход 10 первого разряда первого информационного входа коррелятора, вход 11 второго разряда. первого ин — 20 формационного входа коррелятора, вход 12 первого разряда второго информационного входа коррелятора, вход 13 второго разряда второго информационного входа коррелятора. 25

В цифровом релейном корреляторе определяется оценка релейной взаимной корреляционной функции двух сигналов х и у.

К„„() = Hgx(t+a)) sign y(t) где M — знак математического ожидания;

s ign y — a(-1 )ь

l при а = 1, b = 0

sign y - О, прн а = 0

-1, при а = b = 1.

Сигналы а и b поступают на входы первого и второго разрядов первого информационного входа коррелятора. Сигнал а определяет интервалы времени анализа сигнала у(t) а сигнал

Ь можно сформировать, например, пропуская y(t) через компаратор.

Так как арифметические операции в корреляторе выполняются над последовательными кодами, то двоичные коды второго исследуемого сигнала х подаются на входь1 первого и второго разрядов второго информационного входа коррелятора последовательно. Для преобразователя сигнала x(t) в такие коды можно, например, использовать аналого-цифровой преобразователь,, информация с выходов которого записывается в регистры сдвига, выходы которых подключены к входам первого и второго разрядов второго информационного входа коррелятора. Старшие раз- . ряды двоичных кодов сигнала х определяют его знак, а разрядность двоичных кодов — динамический диапазон коррелятора, на входы 12 и 13 коррелятора; поступают соответственно р— разрядные последовательные двоичные коды положительных и отрицательных ! значений входного сигнала х

=(Ср1,....,С, ) и -x= (d ...,d,) начиная с младших разрядов С и d причем

-х = х + 1.

Коррелятор работает следующим образом.

На первый и второй тактовые входы коррелятора поступают тактовые импульсы ТИ1 и ТИ2, частоты следования которых соответственно равны f, и f

=Р f„,, где Р— разрядность регистра 2), Число Р определяет динамический диапазон коррелятора. Частота 1 1 является частотой дискретизации входных сигналов по оси времени. Значения сигналов х. и у соiÊ ответствуют моментам времени ь

=(M(i-1)+k-13 !Г„, где i = 1,N, И— количество усреднений, М вЂ” число определяемых ординат оценки взаимной релейной корреляционной функции, которое равно числу сумматоров 1.

Каждое значение х. поступает в корiK релятор эа Р тактов. Значения й. и b. н, первого сигнала у поступают на счет1К ные входы триггеров 4 и 5 соответственно с частотой f . Если в регистре 3 единица находится в k-м разряде и нули в остальных разрядах, то на входы установки k-х триггеров 4 и 5 поступает высокий разрешающий потенциал и отрицательный фронт импульса ТИ1 записывает в эти триггеры числа,q и . и сдвигает единицу к к в (K +1) -й раэряд регистра 3. При этом содержимое остальных триггеров не изменяется. После прохождения 1 импульсов THl в триггеры 4 и 5 с номерами 1, 2. ..,1-1 эапись1ваются соответственно числа а „b;,,а; Ь. а. 1,. „В триг ерах 4 и 5 формируются сдвийутые во времени коды сигнала у.

Дешифратор, собранный на элементах И 7, 8 и ИЛИ 9, реализует логическую функцию =c лo, nb vdnanb

В нем производится перемножение входных сигналов. За Р тактов работы коррелятора через этот дешифратор

Проходят последовательно двоичные числа .

1229776

О, при = О (cÄ,,...,с. ),, при 3= 1, Ь= р при a=b = ) = х sign y

На первый и второй информационные входы сумматоров 1 с частотой f

2 поступают соответственно значения разрядов чисел Б = (Б,...,S, ) с

1О

Р1 а выходом регистров 2 и С = (g . .., ) с выходов элементов ИЛИ 9. При этом сумма младших разрядов $, = S, + g и результат переноса П1 отрицательным фронтом первого импульса ТИ2 за15 писываются соответственно в регистр 2 и триггер 6. В следующий такт суммирования определяется сумма Б = $ +

1 1

+ g,+ П, и перенос П . Отрицательный фронт второго импульса ТИ2 сдвигает информацию в регистре 2 на один разряд вправо и записывает значение П в триггер 6. За Р тактов в регистре 2 сформируется сумма Б = S + G =25 (БР1в ° ° эБо )

В исходном состоянии регистры 2 и триггеры 4-6 устанавливаются в нулевое положение, и единица записывается в первый разряд регистра 3. В первый цикл вычисления длительностью ЗΠ— 1/i, на выходе первого элемента ИЛИ 9 за Р тактов сформируется произведение х„з Ю У1 и во втором регистре 2 сформируется 35 сумма S, = C.. В течение второго цикла вычисления во втором регистре 2 сформируется сумма

S = х. sign y а в третьем регистре 2 — сумма

4б

+ x. sign y.

За М-й цикл вычисления во 2,3,..., М-м регистрах 2 сформируются соответственно суммы

Бм-1=. х;мз яп у э Бм. = Бм- +

+ х у ю ° ° ° ь

ià а на вход первого регистра 2 с вы ода М-ro сумматора I поступает последовательно, начиная с младших разрядов, код суммы

М

$, = (Б ...,,S, ) = х, sign y

В последующие циклй вычисления на выходе 7 М-ro сумматора I сформируют-55 ся суммы

М

$. = х sign y

К=1

iK где r = 0,(М-!)..

Через MN циклов на выходе коррелятора сформируется М сумм

М вЂ” с;

r Г.

Чтобы исключить переполнение, разрядность регистров 2 должна быть не меньше разрядности сумм S

Для получения ординат оценки релейной взаимной корреляционной функции достаточно значение Б„ умножить на коэффициент пропорциональности

Я (г/i, ) = S„

Формула изобретения

Цифровой релейный коррелятор, содержащий группу из и сумматоров, группу из и регистров и регистр сдвига, тактовый вход которого является первым тактовым входом коррелятора, тактовые входы всех регистров группы объединены и являются вторым тактовым входом коррелятора, первый информационный вход К-ro сумматора группы (К = 1,2,...,п) соединен с выходом К-го регистра группы, причем выход и-ro сумматора группы является выходом коррелятора, о т л и— ч а ю щ и и о я тем, что, с целью расширения динамического диапазона, в него введены первая и вторая группы элементов И, группа элементов ИЛИ; первая, вторая и третья группы триггеров, причем тактовые входы триггеров первой и второй групп объединены и являются первым тактовым входом коррелятора, выходы регистра сдвига соединены с установочными входами триггеров первой и второй групп, а выход младшего разряда регистра сдвига соединен с входом его же старшего разряда, информационные входы триггеров первой и второй групп являются входами первого и второго разрядов первого информационного входа коррелятора. соответственно, первые информационные входы элементов И первой и второй групп являются входами первого и второго разрядов второго информационного входа коррелятора соответственно, вторые информационные входы элементов И первой и второй групп соединены с выходами соответствующих триггеров первой группы, инверсные выходы триггеров второй группы соединены с третьими

}2)")! 7h

Составитель Е. Ефимова

Редактор И, Дербак Техред Л.Олейник Корректор А. Обручар

Заказ 245? /50 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул.Проектная, и ф входами элементов И первой группы, а прямые выходы соединены с третьими информационными, входами элементов И второй группы, вьгходы элементов И первой и второй групп соединены с первыми и вторыми информационными входами элементов ИЛИ группы соответственно, вьгходы которых соединены с вторыми информацион- 10 ными входами соответствующих сумматорс в группы, выход перово< и tf я переноса каждог о сумматор» t р;ппы с.оединен с входом и выходом сос тветствующего триггера третьей группы соответственно, гактовые входы три геров третьей группы объединены и являются вторым тактовьсм входом коррелятора, а выход г -го сумматора группы подключен к входу первого регистра группы °