Устройство для индикации

Иллюстрации

Показать всеРеферат

Изобретение относится к отображению информации и может быть использовано при создании шкальных устройств для индикации с матричной адресацией индикаторных элементов. Целью изобретения является повышение качества изображения за счет увеличения его контрастности. Поставленная цель достигается введением в устройство логического блока, трех триггеров и формирователя импульсов. Введение указанных блоков позволяет разделить во времени моменты переключения общих и информационных электродов индикаторов, что способствует повышению контрастности. 1 з.п. ф-лы, 3 ил. ьэ 1чЭ со оо

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„Я0„„1229804 A 1 (504 G09GЗ 10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ry/

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3777831/24-24 (22) 02.08.84 (46) 07.05.86. Бюл. № 17 (72) А. П. Логинов, А. А. Александров, В. А. Решетаров, В. Л. Фролов, Г. А. Шляховская и А. П. Шевьев (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 819817, кл. G 09 G 3/04, 1978.

Патент США № 4060801, кл. 340 — 324, опублик. 1977. (54) УСТРОИСТВО ДЛЯ ИНДИКАЦИИ (57) Изобретение относится к отображению информации и может быть использовано при создании шкальных устройств для индикации с матричной адресацией индикаторных элементов. Целью изобретения является повышение качества изображения за счет увеличения его контрастности. Поставленная цель достигается введением в устройство логического блока, трех триггеров и формирователя импульсов. Введение указанных блоков позволяет разделить во времени моменты переключения общих и информационных электродов индикаторов, что способствует повышению контрастности. 1 з.п. ф-лы, 3 ил.!

229804

Изобретение относится к изображеник) информации и может быть использовано при создании шкальных устройств для индик»ции с матричной адресацией индикаторных элементов.

Цель изобретения — повышение качества изображения за счет повышения его контрастности.

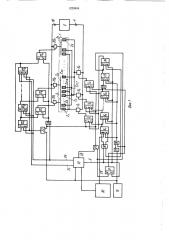

На фиг. 1 приведена структурная схема устройства; на фиг. 2 структурная cхсма логического блока; на фиг. 3 — диаграм- (О мы работы устройства.

Устройство содержит индикаторы 1, ипформационные электроды 2, управ IHII»»He электроды 3, первый вывод 4 источника питания, источник 5 питания, ключи 6i 6„ первой группы, разряды первого регистра

7i--7„, разряды второго регистр» 8, 8,„ четвертый вы. од 9 блока ОННУрОНН»»ННН, блок 10 синхрони s»IIHи, первый триггер 1. второй элемент И 2, второй триггер 13, третий триггер 14, генератор 15 тактовы. импульсов, первый элемент И 16, формирователь 17 импульсов, логический блок 18, второй вывод 19 источника питания, ключи

20i — 20„ второй группы, разряды третьего регистра 21 -21„, разряды четвертого регистра 22 †„, третий элемент И 23, второй 24 2s и третий 25 выходы блока синхронизации, первый 26 и второй 27 элементы ИЛ И, пятый выход 28 блок» . H II xpoIIH»cI II HH, BhlYoJ, 29 датчика 30 информации, элементы 1-1Е-: 31 33, элементы И вЂ” HF. 34

38, четвертый 39 и пятый 40 триггеры.

Устройство раоотает следующим образом.

Перед началом работы устройства блок 10 синхронизации вырабатывает на выходс 24 единичный импульс сброса (фиг. 3), усзанавливающий в нулевое состояние разряды регистров 21>, 2! ь...,21„, 22ь 22,...,22, Блок 10 синхронизации вырабатывает и» Bi Iходе 25 импульс, устанавливающий ll c;IHничное положение триггер 22 и импульс на выходе 9, который устанавливает в единичное состояние триггер 11, а разряды 1О блоков 8,...8;I,...,8„13 и 14 сбрасывает в ноль. В этом состоянии устройство готово для приема отображаемой информации.

При поступлении на выход 29 информ»ционных импульсов (фиг. 3) начинается запись информации в разряды регистров Hi, 82,...,8. первого регистра, после m-го тактового импульса регистр оказывается заполненным, и единичное состояние, записанное первоначально в разряд регистра 8i, переписывается в триггер 13. В результате появления на выходе триггера 13 единичного логического уровня происходит сброс триггера 11 и прохождение тактовых импульсов на разряды регистров 8i,...8,...8„через элемент И 16 прекращается, записанная в разряды регистров 8i, 8,...8„инфор- 55 мация фиксируется. Следуioll(HYI (гп+1) -м тактовым импу Ibco i переключается триггер

14, и на его выходе появляется единичный логический уровень, l10 которому отобр»жаемая информация из разрядов регистров 8ь 8,...,8„переписывается в разряды регистров 7ь 72,...,7„и через ключи 6I, 6,...,6, подается на информационные электроды в виде соответствующих напряжений и токов. Одновременно на m+1 также единичное состояние из триггера переписывается в разряд регистра 22, благодаря наличию единичного уровня на входе элемента И 23, соединенного с выходом через элемент ИЛИ

27 триггера 13. Переключение регистра 22i приводит к включению регистра 21 i, и управляющий электрод 3 через ключ 20 оказызается соединенным с выходом 19 источника 5 питания.

К HIH)lope»i(Ho>IHI>i электродам 21, 2,..., 2„прикладывается flo. lloc напряжение источника 5 питания, H они переводятся во включенное состояние. Д»лее ila выходе 9 блока 10 синхронизации снов» вырабатывает сигнал, по которому триггер 1! и разряд 8 устанавлин»ются и единичное. состояние, а разряды рс истров 82, 8;I,...,8„, 13 и 4 сбрасываются, после чего повторяется процесс записи информации в разряды регистров 8i, 82,...,8. и перенесения его в регистры 7ь 72,...,7„.

Одновременно со сбросом регистров 7i, 72,..., 7,, происходит сброс разряда регистра 21i и далее переключение разрядов регистров

22 и 21 и т.д.

В результате описанного процесса число включенных на индикаторе 1 индикаторных элементов оказывается равным числу информационных импульсов, поступивших на вход.

Управление яркости индикаторных элементов осуществляется подачей импульсов сброса и» разряды регистров 7i, 7,, 7„с выхода

28 блока 10 синхронизации — в промежутке между тактовыми импульсами. Кажуп(аяся яркость индикатора 1 определяется выражением:

1, Тп гдe t время включенного состояния индиKBTopHblx элементов; гп число общих электродов индикатора;

Т время заполнения разрядов регистров 8i, 8г,...,8,;

В<> яркость индикаторных элементов.

Введение в устройство логического блока и триггеров позволяет разделить во времени моменты переключения общих и информационных электродов индикаторов, что способствует повышению контрастности.

Формула изобретения

Устройство для индикации, содержащее первый регистр, выходы разрядов которого соединены с установочными входами разрядов второго регистра, выходы которого

1229804 соединены с первыми входами ключей первой группы, выходы которых соединены с соответствующими информационными электродами индикаторов, управляющие электроды которых соединены с выходами ключей второй группы, первые входы которых соединены с выходами разрядов третьего регистра, вторые входы ключей групп соединены с источником питания, входы установки разрядов третьего регистра соединены с выходами разрядов четвертого регистра, блок синхронизации, датчик информации, вход которого соединен с первым выходом блока синхронизации, а выход — с управляющим входом первого разряда первого регистра, элементы И, ИЛИ, отличающееся тем, что, с целью повышения качества изображения за счет повышения его контрастности, в устройство введены три триггера, формирователь импульсов и логический блок, выходы которого соединены с установочным входом и входом сброса первого разряда первого регистра, тактовые входы разрядов которого соединены с выходом первого элемента и выход последнего разряда первого регистра соединен с первым входом второго элемента И, второй вход которого и первый вход первого элемента И соединены с выходом первого триггера, выход второго элемента И соединен с управляющим входом второго триггера, тактовый вход которого соединен с выходом первого элемента И, выход второго триггера соединен с управляющим входом третьего триггера, выход которого соединен с управляющими входами разрядов второго регистра, второй выход блока синхронизации соединен с входами сброса разрядов четвертого регистра и с первым входом первого элемента ИЛИ, выход которого соединен с входами сброса разрядов третьего регистра, второй вход первого элемента ИЛИ и первый вход третьего элемента И соединены с входами сброса разрядов второго регистра и выходом второго элемента ИЛИ, первый вход которого соединен с выходом второго триггера и входом сброса первого триггера, выход третьего элемента И соединен с тактовыми вхо5 0

40 дами разрядов четвертого регистра, установочный вход последнего разряда четвертого регистра соединен с третьим выходом блока синхронизации, а выход с управляющим входом первого разряда четвертого регистра, четвертый выход блока синхронизации соединен с установочным входом первого триггера, первым входом логического блока, входами сброса разрядов первого регистра, кроме первого, и входами сброса второго и третьего триггеров, выход генератора тактовых импульсов соединен с входом формирователя импульсов, входом блока синхронизации, вторым входом третьего элемента И, с BTopblM входом логического блока и с тактовым входом третьего триггера, пятый выход блока синхронизации соединен с вторым входом второго элемента ИЛИ, выход формирователя импульсов соединен с вторым входом первого элемента И.

2. Устройство по п. 1, отличающееся тем, что логический блок содержит три элемента НЕ, пять элементов И-НЕ и четвертый и пятый триггеры, выходы первого и второго элементов НЕ соединены с входами первого элемента И-НЕ, вход первого элемента НЕ является первым входом блока, выходы второго и третьего элемента И вЂ” НЕ соединены с входами четвертого триггера, выход которого является первым выходом блока, выход пятого триггера соединен с первым входом второго элемента И вЂ” НЕ и является вторым выходом блока, второй вход второго элемента И вЂ” НЕ соединен с выходом первого элемента И вЂ” НЕ, выход третьего элемента НЕ соединен с первым входом третьего элемента И вЂ” НЕ, второй вход которого соединен с выходом второго элемента НЕ, выход первого элемента

НЕ соединен с первыми входами второго и четвертого элементов И вЂ” НЕ, вторые входы которых и вход второго элемента HE являются вторым входом блока, выходы четвертого и пятого элементов И-НЕ соединены с входами пятого триггера, выход первого элемента НЕ соединен с входом третьего элемента НЕ.

1229804

1229804

15 фи/

Редактор Н. Бобкова

Заказ 2229/51

Составитель А. Кулиева

Техред И. Верес Корректор А. Зимокосов

Тираж 455 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП <Патент», г. Ужгород, ул. Проектная, 4