Устройство для контроля логических блоков

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для контроля блоков и узлов цифровой техники. Цель изобрет тения - повышение достоверности контроля . Устройство ,:одержит генератор тестов, группу переключателей, мультиплексор , блок анализа реакции контролируемого логического блока, счетчик , блок анализа тестов, мультиплексор , элементы И, элемент НЕ, конт-- ролируемый логический блок, регистр сдвига, сумматор, группу переключателей , группу согласующих резисторов, шину питания, регистр сдвига, сумматор , генератор тактовых импульсов. При опросе мультиплексором выходов контролируемого блока импульсы с выхода генератора поступают на синхровходы регистров, при опросе входов - через элемент И на синхровход регистра. После того, как всеконтакты контролируемого блока будут опрошены , по сигналу счетчика генератор теста формирует новую тестовую комбинацию, поступающую на входы логического блока и процесс опроса выводов блока последнего повторяется . 1 ил. I (Л с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (511 4 G О6 F 11/26

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3786852/24-24 (22) О!.09.84 (46) 15.05.86. Бюл. 1! 18 (72) С.С.Спиваков, В.В.Богданов, В.С.Лупиков и В.С.Иаслеников (53) 68I.Ç (088.8) (56) Авторское свидетельство СССР

9 830391, кл. С 06 F 11/26, 1979.

Авторское свидетельство СССР В 792256, кл. G 06 F 11/00, 1979. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ БЛОКОВ (57) Изобретение относится к вычислительной технике и может быть использовано для контроля блоков и узлов цифровой техники. Цель изобре .. тения — повышение достоверности контроля. Устройство,одержит генератор тестов, группу переключателей, мультиплексор, блок анализа реакции контролируемого логического блока, счетчик, блок анализа тестов, мультиплек сор, элементы И, элемент НЕ, конт-ролируемый логический блок, регистр сдвига, сумматор, группу переключателей, группу согласующих резисторов, шину питания, регистр сдвига, сумматор, генератор тактовых импульсов.

При опросе мультиплексором выходов контролируемого блока импульсы с выхода генератора поступают на синхровходы регистров, при опросе входов — через элемент И на синхровход регистра. После того, как все- контакты контролируемого блока будут опрошены, по сигналу счетчика генератор теста формирует новую тестовую комбинацию, поступающую на входы ло-. гического блока и процесс опроса выводов блока последнего повторяется. 1 пл.

1231504

Изобретение относится к вычислительной технике и может быть использовано для контроля блоков и узлов цифровой техники.

Цель изобретения - повышение достоверности контроля.

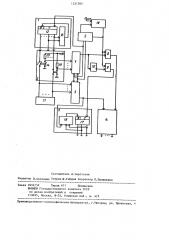

На чертеже изображена структурная схема устройства для контроля логических блоков.

Устройство содержит генератор тестов 1, группу переключателей 2, мультиплексор 3, блок анализа реакции контролируемого логического блока 4, счетчик 5, блок анализа тестов

6, мультиплексор 7, элементы И 8 и

9, элемент НЕ 10, контролируемый логический блок 1), регистр сдвига

12, сумматор 13, группу переключателей 14, группу согласующих резисторов 15, шину питания 16, регистр сдвига 17, сумматор 18, генератор тактовых импульсов 19.

Генератор теста 1 содержит регистр сдвига с сумматором по модулю два в цепи обратной связи.

Через переключатели 2 и 14 осуществляется подключение входов контролируемого блока к выходам генератора тестов 1 и выдача сигналов низкого уровня на соответствующие им выходы высокого уровня, если соответствующие выводы контролируемого блока 11 являются выходами.

Блоки анализа 4 и 6 выполнены на регистрах сдвига с сумматором по модулю два в цепи обратной связи.

Мультиплексоры 3 и 7 осуществляют подключение соответствующих входов к выходу в зависимости от кода на управляющих входах и могут быть выполнены на мультиплексорах, например 155КП1, 155КП7.

Устройство работает следующим образом.

В исходном состоянии регистр 17 в блоке 6 (4), счетчик 5 сброшены, в регистр 12 занесена исходная комбинация, генератор 19 остановлен (цепи установа в исходное состояние на чертеже не показаны), переключатели 2 обеспечивают подключение выходов генератора тестов I к входам контролируемого блока 11. При пуске устройства генератор 19 начинает выдавать импульсы, изменяюшие состояние счетчика 5, а мультиплексор 3 преобразует сигналы на выводах конт . ролируемого блока 11 в последовательный код,, поступающий на синхровходы регистров блоков 4 и 6 анализа тестов и реaêöèè контролируемого блока. При этом, если осуществляется выдача сиг" нала с входа блока 11, то на выходе мультиплексора 7 присутствует низкий уровень сигнала, а если мультиплексором 3 выбирается сигнал с выхода контролируемого блока 11„ то на выходе мультиплексора 7 присутствует высокий уровень сигнала.

Таким образом, при опросе мульти" плексором 3 выходов контролируемого блока импульсы с выхода генератора

19 через элемент 4 и 8 поступают на синхровходы регистров в блок 4, при опросе входов — через элемент И

9 на синхровход регистра в блоке 6.

После того, как все контакты контролируемого блока 11 будут опрошены, по сигналу счетчика 5 генератор теста 1 формирует новую тестовую комбинацию, поступающую на входы блока ll и процесс опроса выводов блока 11 повторяетсяо

В результате в блок 4 анализа реакции контролируемого блока вводится последовательность, соответствующая значениям сигналов на выходных контактах блока 11, а в блок анализа тестов 6 вводится последовательность, соответствующая значениям тестовых, сигналов на входах контролируемых контактах блока 11. После подачи необходимого числа тестогых комбинаций сигналом с выхода счетчика 5 производится останов генератора 19.

Сдвигающий регистр 17 с линейными обратными связями через сумматор 18 осуществпяет деление многочлена, описывающего входную двоичную последовательность, на характеристический многочлен сдвигающего регистра с об ратны я связями, и по окончанию блок анализа тестов содержит код ос-,. татка от деления, характеризующий последовательность сигналов на входах блока 11, а блок анализа реакции контролируемого блока 4 содержит код, характеризующий последовательность сигналов на выходах блока 11.

Эталонные коды определяются для к:аждого типа исправных объектов экспериментально или расчетом на 3ВМ

/ и используются оператором для сравнения с реальными.

1231

Формула изобр етен ия

Устройство для контроля логических блоков, содержащее генератор тестов, генератор тактовых имп...льсов, счетчик, первый мультипл=-rccop блок анализа реакции контро.ируемо—

ro логического блока, причем блок анализа реакции контролируемого логического блока содержит регистр и сумматор, вход пуска устроцства соединен с входом пуска генератора тактовых импульсов, выход которого соединен с счетным входом счетчика, выходы которого соединены с управляющими входами первого мультиплексора, выход переполнения счетчика соединен с входом запуска генератора тестов, информационный выход первого мультиплексора соединен с первым входом сумматора блока анализа контролируемого логического блока, выход которого соединен с информа.ционным входом регистра блока анали-за, реакции контролируемого логического блока, выходы которого соедине-. ны с группой входов сумматора, блоi

1231504

Составитель А.Сиротская

Редактор И.Сегляник Техред И.Гайдош Корректор Л.Пилипенко

Заказ 2652/52 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Óÿòoðoä, ул. Проектная, 4