Аналоговое запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники, в частности к технике запоминающих устройств , и может быть использовано в аналого-цифровых преобразователях, в устройствах обработки информации и т.д. для запоминания аналоговых . сигналов. Цель изобретения - повышение точности устройства за счет введения ключа и преобразователя.напряжение - временной интервал с соответствующими функциональными связями с блоком ввода информации и задающим генератором. I з.п. ф-лы, 3 нл. (Л с

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ugl 01) 15В 4 0 11 С 27 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,-„

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО делАм изОБРетений и ОткРытий

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3542919/24-24 (22) 21.01.83 (46) 15.05.86. Бюл. Н 18 (71) Институт кибернетики АН ЭССР (72) М.J<. Рохтла (53) 681.327.66(088.8) (56) Авторское свидетельство СССР

У 813506, кл. G ll С 27/00, 1981.

Авторское свидетельство СССР

У 752493, кл. G 11 С 27/00, 1980. (54 ) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к области вычислительной техники, в частности к технике запоминающих устройств, и может быть использовано в аналого-цифровых преобразователях, в устройствах обработки информации и т.д. для запоминания аналоговых . сигналов. Цель изобретения - повышение точности устройства эа счет введения ключа и преобразователя.напряжение — временной интервал с соответствующими функциональными связями с блоком ввода информации и задающим генератором. 1 s.ï. ф-лы, 3 ил.

30 Формула изобретечия

1 1?31

Изобретение относится к вычислительной технике, в частности к технике запоминающих устройств, и может быть использовано в аналого-цифровых преобразователях, в устройствах обработки информации для запоминания аналоговых сигналов.

Цель изобретения — повышение точности устройства.

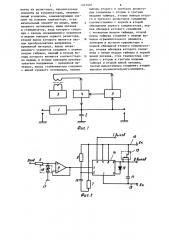

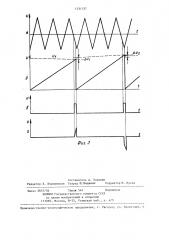

На фиг. 1 приведена функциональная IG схема предложенного устройства,", на фиг . 2 — функциональная схема преобразователя аналог-код; на фиг. 3 временные диаграммы, поясняющие работу устройства. 15

Предложенное устройство образуют блок 1 ввода информации, накопительный элемент на конденсаторе 2, задающий генератор 3, ключ 4 и преобразователь 5 напряжение — временной ин- 20 тервал, который содержит пассивные элементы — резисторы 6-8 операционный усилитель 9, накопительные элементы — конденсаторы 10 и 11, ограничительный элемент 12, компенсирующий элемент на транзисторе 13, таймер 14, шины 15 и 16 питания, шину

17 нулевого потенциала и стабилизат,ор 18.

Устройство работает следующим образом.

Конденсатор 2 через блок 1 ввода информации подключается к источнику запоминаемого сигнала (не показан)

I и заряжается до запоминаемого значения V ° Задающий генератор 3 непрерывно нарабатывает синусоидальные или пилообразные сигналы (фиг.3a) поступающие на один из входов ключа

4 и на первый выход преобразователя

4О

5, в котором вырабатывается пилообразный потенциал (фиг. Зб). На втором выходе преобразователя 5 непосредственно до сброса пилообразного

Д 3 потенциала вырабатывается нормированный импульс (фиг. Зв) для запуска ключа 4. Ключ 4 замыкается, и к потенциалу на конденсаторе 2 добавляется потенциал задающего генератора

3 (фиг . Зг).

59

Если напряжение на конденсаторе

2 за временной интервал, пропорциональный запоминаемому сигналу, уменьшается (фиг. Зв), то преобразователь 5 непосредственно до начала следующего временного интервала выдает нормированный импульс (фиг.Зб) ,который подается на вход ключа 4

537 2 (ключ 4 замыкается), и к сигналу на конденсаторе 2 добавляется положительный потенциал и U < (фиг. За) .

Если напряжение на конденсаторе 2 за временной интервал, пропорциональный запоминаемому сигналу, увеличивается (фиг. Зв), то преобразователь

5 вьдает непосредственно до начала следующего временного интервала нормированный импульс (фиг. Зб), который подается на вход ключа 4 (ключ

4 замыкается), и к сигналу на конденсаторе 2 добавляется отрицательный потенциал hU (фиг. Зг). Если напряжение на конденсаторе 2 за временной интервал, пропорциональный запоминаемому сигналу, остается неизменным, то к напряжению на конденсаторе 2 потенциал не добавляется.

Технико-экономическая эффективность изобретения заключается в повышении точности запоминания сигнала в результате обеспечения запоминания сигнала без промежуточного преобразования (аналоговый код — цифровой код — аналоговый код), что позволяет избежать дополнительных погрешностей.

1. Аналоговое запоминающее устройство, содержащее задающий гснератор, блок ввода информации, выход которого из обкладок накопительного элемента на конденсаторе, другая обкладка которого соединена с шиной нулевого по" тенциала, вход блока ввода информа\ ции является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности устройства, в него введены ключ и преобразователь напряжение — временной интервал, вход которого соединен с выходом блока ввода информации, первый выход преобразователя напряжение — временной интервал соединен с выходом задающего генератора и первым входом ключа, второй вход которого соединен с вторым выходом преобразователя напряжение — временной интервал, выход ключа соединен с выходом блока ввода информации.

2. Устройство по и. 1,, о т л и— ч а ю щ е е с я тем, что преобразователь напряжение — временной интервал содержит таймер, пассивные эле1231537

Фиг. 8 менты на резисторах, накопительные элементы на конденсаторах, операционный усилитель, компенсирующий элемент на полевом транзисторе, ограничительный элемент на диоде, шину нулевого потенциала, шины питания и стабилизатор, вход которого соединен с входом операционного усилителя и первым выводом первого резистора, второй вывод которого является вхо- 10 дом преобразователя напряжение— временной интервал, выход операционного усилителя соединен с первым входом таймера, первый и второй выходы которого являются соответствен- 15 но первым и вторым выходами преобразователя напряжение — временной интервал, выход стабилизатора соединен с шиной нулевого потенциала, первые выводы второго и третьего резисторов соединены с вторым и третьим входами таймера, вторые выводы второ" го и третьего резисторов соединены соответственно с первой и второй обкладками первого конденсатора, первая обкладка которого соединека с четвертым входом таймера, второй выход таймера соединен с первым выводом ограничительного элемента, затвором и истоком транзистора и первой обкладкой второго конденсатора, вторая обкладка которого соединена с пятым входом таймера и первой шиной питания, сток транзистора соединен с вторым и третьим входами таймера и второй шиной питания, третий выходтаймера соединенс вторым выводом ограничительногоэлемента.

1231537

Составитель А. Воронин

Редактор Л. Пчелинская Техред М. Ходанич Корректор И. Куска

Заказ 2657/54 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4