Устройство компенсации межсимвольной интерференции многоуровневых сигналов в каналах передачи данных

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и обеспечивает повышение точности коррекции мёжсимвольной интерференции. Блок сравнения (ВС) 2 сравнивает многоуровневые входной и опорный сигналы, которые поступают соответственно с АЦП 1 и блока формирования многоуровневых опорных (Л С

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) Ai (5D 4 Н 04 В 3/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

Г10 делАм изОБРетений и ОтнРытий

К А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 2410515/24-09 (22) 04.10.76 (46) 15,05.86, Бюл. Ф 18 (72) Л.И.Сулин, К.П.Бочаров и В.В.Романов (53) 621.395.664:621.397.27(088.8) (56) Патент Великобритании 9 1386466, кл. Н 04 В 3/14, 1975. Кловский Д.Д. Николаев Б.И. Инженерная реализация радиотехнических схем. M,: Связь, 1975, с. 45. (54) УСТРОЙСТВО КОМПЕНСАЦИИ МЕЖСИМВОЛЬНОЙ ИНТЕРФЕРЕНЦИИ МНОГОУРОВНЕВЫХ

СИГНАЛОВ В КАНАЛАХ ПЕРЕДАЧИ ДАННЫХ (57) Изобретение относится к электросвязи и обеспечивает повышение точности коррекции межсимвольной интерференции. Блок сравнения (БС)

2 сравнивает многоуровневые входной и опорный сигналы, которые поступают соответственно с АЦП 1 и блока формирования многоуровневых опорных

1 сигналов. (БФМОС) 7, БС 2 выполнен в виде в-разрядных сумматоров, соединенных последовательно. После каждого сдвига выборок входного сигнала в БС 2 осуществляются два цикла преобразования. В первом цикле я разрядов кода с центрального а -разрядного сумматора переписываются в блок 3 хранения предварительных решений.

Во втором цикле осуществляется принятие окончательного решения о значении переданного сигнала, предварительное решение о котором хранится

231615 в блоке 4 коррекции предварительных решений. Для этого первый решающий блок (РБ1 5 анализирует сигнал, поступающий в БС 2. Если предварительное решение принято неверно, то на

РБ 5 поступает сигнал, соответствующий сумме выборок шума и ошибки.

В этом случае с РБ 5 на БФМОС 7 и на блок 4 коррекции предварительных решений поступают соответствующие сигналы. Управление весом кода в БФМОС

7 осуществляется по сигналам со второго РБ 6. 2 з.п. ф-лы, 3 ил.

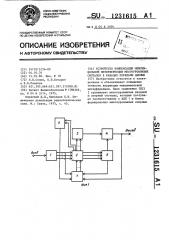

Блок 2 сравйения многоуровневых входных и опорных сигналов состоит из т-разрядных двухвходовых сумматоров 8.

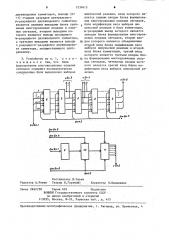

Блок 7 формирования многоуровневых ofIopHblK сигналов содержит блок

9 вычисления выборок импульсной ре-. акции, блок 10 модификации веса вы30

Изобретение относится к электросвязи и может быть использовано для коррекции межсимвольной интерференции в принимаемых сигналах данных.

Цель изобретения — повышение точ- 5 ности коррекции межсимвольной интерференции.

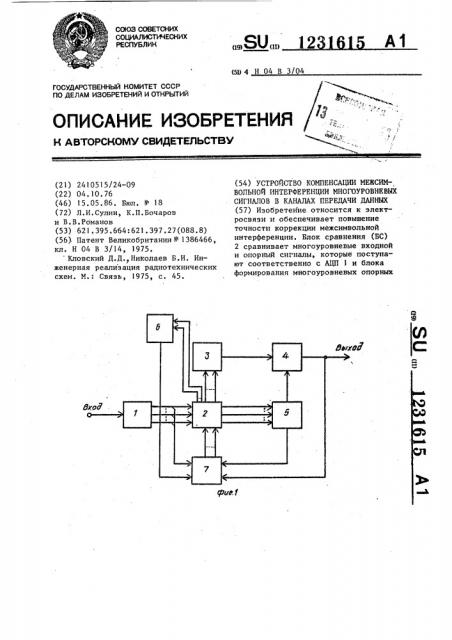

Па фиг. 1 изображена структурная электрическая схема устройства компенсации межсимвольной интерференции многоуроцневых сигналов в каналах передачи данных; на фиг. 2— структурная электрическая схема блока сравнения многоуровневых входных и о1 орных сигналов, иа фиг. 3 — струк-:1 туриая электрическая схема блока формирования многоуровневых опорных сигналов..

Устройство компенсации межсимвольной интерференции многоуровневых 20 сигналов в каналах передачи данных содержит аналого-цифровой преобразователь 1, блок 2 сравнения многоуровневых входных и опорных сигналов, блок 3 хранения предварительных решений, блок 4 коррекции предварительных решений, первый 5 и второй

6 решающие блоки, блок 7 формирования многоуровневых опорных сигналов. борок импульсной реакции и блок ll коммутации.

Устройство компенсации межсимвольной интерференции многоуровневых сигналов в каналах передачи данных работает следующим образом.

Устройство реализует критерий максимального правдоподобия и минимизирует пиковую ошибку

21 Т(-2:, "как в соответствии с критерием где Z)iTj — выборки принимаемого сигнала;

Ь„ - отсчеты импульсной реакции канала;

d — количество элементарных импульсов, учитываемых при анализе;

Ю f — функция плотности вероятности; а„ вЂ” кодовый символ с порядковым номером К, соответствующий -й позиции.

Выборки принимаемого сигнала с выхода аналого-цифрового преобразоваз 1231 теля 1 в параллельном щ -элементном коде поступают на первые входы m-разрядного двухвходового сумматора 8 блока 2. После каждого сдвига выборок в блоке 2 осуществляется два цик- 5 ла преобразования.

В первом цикле 0 разрядов центрального m-разрядного двухвходового сумматора 8 переписываются в блок 3.

В зависимости от знака выборки, на 1Î выходах центрального m-разрядного двухвходового сумматора 3 в блоке

-ъ .Ф

2 осуществляется алгебраическое суммирование выборок импульсной реакции h; и выборок преобразуемого сиг- 15 нала. В случае, если сигнал на выходе решающего блока 5 сформирован правильно, то в центральном m-разрядном двухвходовом сумматоре 8 останется величина 20

-I ь=n,+ С. h;g„,, =-d к=-d

25 где и, — отсчеты шумовой составляю" щей входного сигнала.

С целью сокращения числа операций сложения (вычитания) выборки импульсной реакции h; алгебраически суммируются с выборками, хранящимися в m-разрядных двухвходовых сумматорах 8 с весами сигналов, зафиксированных в блоке 3. Управление весом кода в блоке 11 осуществляется З5 по сигналам, поступающим от блока 6.

Во втором цикле осуществляется принятие окончательного решения о значении переданного сигнала, предварительное решение о котором хра- 4О нится в блоке 4. Для этого посредством решающего блока 6 анализируется сигнал на выходах последнего ш-разрядного двухвходового сумматора 8, в котором к этому моменту за- 45 писаны только выборки шума, если . предварительное решение принято верно, Если же предварительное решение

Принято неверно, то на выходах IIQ следнего m-разрядного двухвходового сумматора 8 будет сигнал, соответствующий сумме выборок шума и ошибки.

При этом в решающем блоке 5 формируются сигналы алгебраического сложения, подаваемые на блок !1, блок

1О, а также сигналы коррекции результата. Этот процесс повторяется до тех пор, пока в последнем m-paз615 4 рядном двухвходовом сумматоре 8 величина выборки по абсолютному значению не будет меньше величины h /2.

Формула изобретения

1, Устройство компенсации межсимвольной интерференции многоуровневых сигналов в каналах передачи данных, . содержащее последовательно соединен". ные аналого-цифровой преобразователь, блок сравнения многоуровневых входных и опорных сигналов и первый решающий блок, блок формирования многоуровневых опорных сигналов, первый вход которого соединен с выходами аналого-цифрового преобразователя, а выходы подключены к вторым входам бло«са сравнения многоуровневых входных и опорных сигналов, о т л ич а ю щ е е с я тем, что, .с целью повышения точности коррекции межсимвольной интерференции, в него вве,дены последовательно соедине«1««ые блок хранения предварительных решений и блок коррекции предварительных решений, второй решающий блок, входы которого соединены с вторыми входами блока сравнения многоуровневых входных и опорных сигналов, а выход подключен к второму входу блока формирования многоуровневых опорных сигналов, третий вход которого сое— динен е первым выходом первого решающего блока, второй выход которого подключен к второму входу блока коррекции предварительных решений, вы,ход которого подключен к четвертому входу блока формирования многоуровневых опорных сигналов, третьи выхо-. ды блока сравнения многоуровневых входных и опорных сигналов соединены с входами блока хранения предваритель-. ных решений.

2. Устройство по п. 1, о т л и " ч, а ю щ е е с я тем, что блок сравнения многоуровневых входных и опорных сигналов содержит последовательно соединенные 1п -разрядные двухвходовые сумматоры, нечетное количество которых равно числу анализируемых выборок входного сигнала,. при этом первые входы первого 1«)-разрядного двухвходового сумматора являются первыми входами блока сравнения многоуровневых входных и опорных сигналов, вторыми входами которого являются вторые входы каждого из а-разрядных

1231á15

3. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что блок формирования многоуровневых опорных сигналов содержит последовательно соединенные блок вычисления выборок е к&b дю. 7 дтпл. фиг.З

Составитель Ш,Эвьян

Редактор А.Ревин Техред О.Гортвай Корректор Л.Пилипенко

Заказ 2бб2/58 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР . по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 (двухвходовых сумматоров, выходы (и+

+1)-старших разрядов центрального рп-разрядного двухвходового сумматора являются первыми выходами блока сравнения многоуровневых входных и опор- ных сигналов, вторыми выходами которого являются выходы последнего Ф-разрядного двухвходового сумматора, а третьими выходами являются выходы п разрядов m-разрядного двухвходово- го сумматора, предшествующего центральному. импульсной реакции, вход которого является первым входом блока формирования многоуровневых опорных сигналов, блок модификации веса выборок импульсной реакции и блок коммутации, 1п-разрядный выход которого является выходом блока формирования многоуровневых опорных сигналов, вторым вхо10 дом которого являются объединенные второй вход блока модификации веса выборок импульсной реакции и второй. вход блока коммутации, третий вход которого является третьим входом бло1 ка формирования многоуровневых опорных сигналов, четвертым входом которого является третий вход блока модификации веса выборок импульсной реакции.