Последовательный двоичный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в цифровых системах управления . Целью изобретения является расширение области применения за счет обеспечения возможности работы в обычном и ускоренном режимах. Последовательный двоичный сумматор содержит одноразрядньй комбинационный сумматор (оке) и схему хранения переноса , состоящую из двух триггеров с блоками управления из логических элементов , двух выходных элементов И и одного элемента ИЛИ. В сумматор дополнительцо введены два элемента И и один элемент ИЛИ, причем выход первого триггера связан с информационным входом первого дополнительного элемента И, выход которого подключен к первому входу дополнительного элемента ИЛИ, имеющего по выходу связь с информационным входом второго триггера , с которым через второй дополнитель 1ый элемент И и второй вход дополнительного элемента ИЛИ связан выход переноса ОКО. Шина разрешения двухтактного режима соединена с управляющим входом первого дополнительного элемента И. Шина разрешения потактного режима соединена с управ,- ляющим входом второго дополнительного элемента И и зттравляющим входом выходного элемента И первого тригге- . ра. 1 ил. ct ю сл го со W Ьо 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (5!) 4 С 06 F 7/50

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3811292/24-24 (22) 05 ° 11.84 (46) 23.05.86. Бюл. !! 19 (71) ЛГУ им. А.A.)Êäaíîâà (72) А.Ç.Подколзин и Н.А.Подколзина (53) 68!.325(088.8) (56) Дроздов Е.А. и др. Электронные цифровые вычислительные машины.

N.: Воениздат, 1968, с. 600.

Авторское свидетельство СССР

l! 637811, кл. С 06 F 7/50, 1978. (54) ПОСЛЕДОВАТЕЛЬНЫЙ ДВОИЧ%!Й СУМ—

МАТОР (57) Изобретение относится к области вычислительной техники и может быть использовано в цифровых системах управления. Целью изобретения является расширение области применения за счет обеспечения воэможности работы в обычном и ускоренном режимах. Последовательный двоичный сумматор содержит одноразрядный комбинационный сумматор (ОКС) и схему хранения переноса, состоящую из двух триггеров с блоками управления из логических элементов, двух выходных элементов И и одного элемента ИЛИ. В сумматор дополнительпо введены два элемента И и один элемент ИЛИ, причем выход первого триггера связан с информационным входом первого дополнительного элемента И, выход которого подключен к первому входу дополнительного элемента ИЛИ, имеющего по выходу связь с информационным входом второго триггера, с которым через второй дополнительный элемент И и второй вход дополнительного элемента ИЛИ связан выход переноса ОКС. Нина разрешения двухтактного режима соединена с управляющим входом первого дополнительного элемента И. Нина разрешения нотактного режима соединена с управляющим входом второго дополнительного элемента И и управляющим входом выходного элемента И первого триггера. 1 ил.

l?33!33

Изобретение относится к вычислительной технике и может быть использовано н цифровых системах управ.пения.

Цель изобретения — расширение области применения за счет обеспечения возможности работы в обычном (двухтактном) и ускоренном (потактнам) режимах.

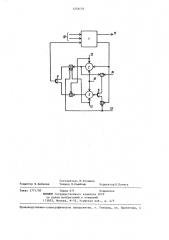

На чертеже представлена структурная схема последовательного дваичного сумматора.

Предлагаемый сумматор содержит одноразрядный комбинационный сумматор 1, два триггера 2 и 3, элементы

И 4 и 5, элемент ИЛИ 6, элементы

И 7 и 8, элемент ИЛИ 9, входы 10 одноразрядного комбинационного сумматора ), вьгход 11 суммы, тактирующий вход 12 триггера 2, тактирующий вход.

13 триггера 3, шину 14 разрешения двухтактного режима последовательного двоичного сумматора, шину 15 раз,решения потактного режима последовательного двоичного сумматора, шину

16 установки н "0".

Сумматор работает следующим образом.

В двухтактном режиме работы для определенности принимают, что складывается два трехразрядных двоичных числа 101 и 101. Перед началом сложения оба триггера 2 и 3 устанавлинаются в "О" управляющим тактовым сигналом, подаваемым на шину 16. На шину

14 подается потенциальный сигнал, соответствующий двухтактному режиму работы.

По такту Т на входы 10 подаются младшие разряды слагаемых. На входе переноса 0КС сигнал отсутствует,, так как триггер 3 предварительно установлен н 0 . В результате сложения двух и и

1 на выходе переноса ОКС образуети 1! ся l сигнал, который поступает на хранение в триггер 2. На выходе 11 суммы сигнал отсутствует.

По такту Т перенос из триггера 2 через элемент И 7 и элемент ИЛИ 9 переписывается в триггер 3.

По очередному такту Тг на входы

10 информация не поступает, так как вторые разряды слагаемых равны "0".

С выхода триггера 3 через элемент

И 5 и элемент ИЛИ 6 на вход переноса

ОКС поступает "1". На выходе. 11 появляется сигнал. На выходе переноса

ОКС сигнал отсутствует и триггер 2 устанавлинается в "О

По очередному такту Т триггер 3 устананлинается в 0

По третьему такту Т, на входы 10 поступают третьи разряды чисел, а на входе перенося ОКС информация отсутствует. В результате сложений двух

"1" на вьгходе переноса ОКС образуется 1 сигнал, поступающий на хранение н триггер 2. На ньгхоце 11 сигнал отсутствует.

По третьему такту Тд на входы 10 информация не поступает. Перенос из триггера 2 через элемент И 7 и элемент ИЛИ 9 переписьгвается в триггер 3 .

Сложение двух трехразрядных чисел закончилось: в результате образовалось число 1010, три младших разря— да которого по первым трем тактам Т, поступают на выход 11, а старший раз. ряд поступает на выход 11 уже по четвертому такту Т, (с выхода элемента памяти через элемент И 5, элемент ИЛИ 6 и комбинационньrA сумматор l). На получение результата затрачивается четыре такта Т, и четыре такта Т>, причем .информация поступает на входы ОКС только по тактам Т, .

По занершении сложения сигнал с шины

14 снимается.

В патактном режиме работы для определенности принимают, что складываются трехразрядные числа 101и 011.

Перед началом работы оба триггера 2 и 3 устанавливаются в 0 тактовым сигналом, приходящим на шину 16. На шину 15 подается потенциальный сигнал, соответствующий потактнаму режиму работы.

По такту Т, на входы 10 подаются младшие разряды слагаемых. На нходе переноса ОКС сигнал отсутствует, так как триггер 3 предварительно установлен н О, В результате сложения двух "l" на. выходе переноса ОКС образуется "l" сигнал, который поступает на хранение в триггер 2. На выходе

11 суммы сигнал отсутствует.

По такту Т на один из входов 10 поступает "1", на второй информация не поступает. С выхода триггера 2 через элемент И 4 и элемент ИЛИ 6 на вход переноса СКС поступает и суммируется с в орым разрядом второrо числа. В результате на выходе l! сигнал отсутствует, а перенос ат сло- жения поступает из ОКС нл хранение через элемент И 8 и элемент ИЛИ 9 в триггер 3.

По очередному такту Т на один из входов !О поступает "!", на второй информация не поступает. С выхода триггера 3 через элемент И 5 и элемент ИЛИ 6 на вход переноса ОКС поступает !, которая суммируется с третьим разрядом первого числа. В результате на выходе- l! сигнал отсутствует, а перенос от сложения поступает из ОКС на хранение в триггер 2.

Сложение двух трехразрядных чисел закончилось, в результате образовалось число !000, старший разряд которого поступает на выход l! уже по вторму такту Т (с выхода триггера 2 через элемент И 4, элемент ИЛИ б.и комбинационный сумматор !). На получение результата затрачивается два такта Т, и два такта Т, причем информация поступает на входы ОКС как по тактам Т,, так и по тактам Т .

Сигнал с шины !5 по завершении сложения снимается.

Ф о р м у л а изобретения

Последовательный двоичный сумматор, содержащий одноразрядный комбинационный сумматор и узел хранения переноса, содержащий два триггера, два элемента И и первый элемент ИЛИ, причем выходы первого и второго триггеров подключены к первым входам соответствующих элементов И, выходы ко233!33 4 торых подключены к входу первого эле мента ИЛИ, входы слагаемых одноразрядного комбинационного сумматора являются входами последовательного двоичного сумматора, а вход переноса подключен к выходу первого элемента

ИЛИ, первый и второй тактовые входы последовательного двоичного сумматора соединены с вторыми входами второго и первого элементов И соответственно, отличающийся тем, что, с целью расширения области применения за счет обеспечения возможности работы в обычном (двухтактном) и ускоренном (потактном) режимах, в него дополнительно введены третий и четвертый элементы И и второй элемент ИЛИ, причем выход первого триггера соединен с первым входом третьеО го элемента И, выход которого подключен к первому входу второго элемента

ИЛИ, выход которого соединен с информационным входом второго триггера. второй вход второго элемента ИЛИ соединен с выходом четвертого элемента

И, первый вход которого соединен с выходом переноса одноразрядного комбинационного сумматора, и информационным входом первого триггера, шина разрешения двухтактного режима последовательного двоичного сумматора соединена с вторым входом третьего элемента И, шина разрешения потактного режима последовательного двоичного сумматора соединена с вторым входом

35 четвертого элемента И и третьим входом первого элемента И.

1233133

Составитель N.Åñåíèíà

Техред JI.Îëåéíèê Корректор В. Бутяга

Редактор Н.Бобкова

Заказ 2771/50

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4