Устройство для суммирования

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано для построения быстродействующих арифметических устройств, работающих как в системе остаточных классов (СОК), так и в позиционноостаточной системе счисления (ПОС). Цель изобретения - расширение функциональных возможностей за счет формирования устройством сигнала переполнения . Устройство для сложения содержит первую и в/орую группы из п сумматоров (п - число оснований СОК), первые и вторые входы которых объединены и являются входами соответственно первого и второго операндов в СОК. Новьм в. устройстве является то, что в него дополнительно введены п мультиплексоров , переключатель режима, формирователь переполнения и два преобразователя позиционного кода в код СОК, входы которых являются входами соответственно первого и второго позиционных операндов, а их выходы подключены соответственно к первьм и вторЕям входам каждого из п су маторов первой группы, выходы которых подключены к соответствующим входам формирователя переполнения и первым входам п мультиплексоров, вторые входы которых подкяючейы к соответствующим выходам п сумматоров второй группы выходы п мультиплексоров являются выходом суммы устройства, а их управлянщие входы объединены, подключены к выходам формирователя переполнения и переключателя режима и являются выходом переполнения устройства 1 з.п. ф-лы. 2 ил. i (О С ю 00 И-А СП 00

А1 союз советских социАлистичесних

РЕСПУБЛИК аю <и) рр 4 G 06 F 7/72

ОПИСАНИЕ ИЗОБРЕТЕНИЯ и ASTQPCH0MV ОВИДЕТИЗЬСТВУ гос щмственный иомитет ссср по делдм иэоь чтений и открытий (2i ) 3812982/24-24 (22) 15.11.84 (46) 23.05.86. Бюл. У 19 (72) В.Г.Евстигнеев, А.Н.Кошарновс йй, А.В.Иаркин и А.С.Новожилов (53) 681.325(088.8) (56). Авторское свидетельство СССР

Ф 446056, кл. С 06 F 7/72, 1975.

Авторское свидетельство СССР

В 883903, кл. С 06 F 7/72, 1981. (54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ (57) Изобретение относится к области вычислительной техники и может быть использовано для построения быстродействующих арифметических устройств, работающих как в системе остаточных . классов (СОК), так и в позиционноостаточной системе счисления (ПОС).

Цель изобретения — расширение функциональных возможностей за счет формирования устройством сигнала переполнения. Устройство для сложения содержит первую и вторую группы из п сумматоров (и — число оснований СОК), первые и вторые входы которых объедииены и являются входами соответственно первого и второго операндов в СОК.

Новью в устройстве является то, что в него дополнительно введены и мультиплексоров, переключатель режима, формирователь перенолнеяия и два пре« образователя позиционного кода в код

СОК, входы которых являются входами соответственно первого и второго позиционных операндов, а их выходы подключены соответственно к первым и вторым входам каждого из и сумматорбв первой группы, выходы которых подключены к соответствующим входам формирователя переполнения и первым входам и мультиплексоров, вторые входы которых подключены к соответствующим выходам и сумматоров второй . группы выходы и мультиплексоров являются выходом суммы устройства, а их управляющие входы объединены, подключены к выходам формирователя переполнения и переключателя режима и являются выходом переполнения устройства 1 з.н. ф-лы. 2 ил.

123..(1 53

Изобретение относится к вычислительной технике и может быть использовано для построения быстродействующих арифметических устройств, работающих как в системе остаточных классов {СОК), так и в позиционно-остаточной системе счисления (ПОС).

Цель изобретения — расширение функциональных возможностей за счет формирования устройством сигнала переполнения, 1

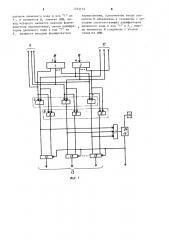

На фиг. 1 представлена структурная схема устройства для сложения; на фиг. 2 — структурная схема формирователя переполнения„

Устройство содержит первый преобразователь позиционного кода 1 в кад системы остаточных классов,, второй преобразователь 2 позиционного када в код системы остаточных классов, вход 3 первого позиционного операнда вход 4 второго позиционного операнда, первую группу 5 из и сумматоров, вторую группу 6 из и сумматоров, сумматор 7 первой группы из и сумматоров, сумматор 8 второй группы из и сумматоров, вход 9 первого операнда в

СОК, вход 10 второго операнда в СОК, формирователь 11 переполнения, п коммутаторов 12, выход 13 суммы устройства, переключатель 14 режима, элемент И 15.

Формирователь 11 переполнения содержит и дешифраторов 16 двоичного кода в код "1" из Р„ (Р„ — основания

СОК), вход 17 формирователя переполнения, элементы И 18 на п входов„ элемент ИЛИ 19, выход 20 формирователя переполнения.

Переключатель 14 режима представляет собой ключ, с помощью которого на управляющие входы и коммутаторов

12 подается нулевой потенциал.

Предлагаемое устройство может работать в двух режимах1 суммировать числа, представленные кодом СОК, и суммировать числа, представленные позиционным (двоичным) кодом.

Необходимость разработки такого устройства связана с тем, что эа счет перехода в позиционных устройствах к основанию системы счисления S, значительно превышающему двойку, быстро растет скорость вычислений. Наиболее подходящий (по крайней мере в настоящее время) величиной основания является S =- 2 . Эта величина, как

0 извесгна, называется байтом. Если же

1 1

45 в пределах байта оставить традиционную двоичную арифметику, то эффекта

8 от перехода к S = 2 не получится.

Если же в пределах байта применить другое кодирование (например, СОК), позволяющее распараллелить операцию по нескольким независимым основаниям, то эффект от перехода к большому Б возрастает при увеличении S.

Машинное слово современной ЭВМ имеет длину обычно 2 или 4 байта.

Тогда сумматор такой ЭВМ может быть построен на основе двух или четырех предложенных устройств. При этом каждый байт исходных данных, представленных двоичным кодом, с помощью преобразователей 1 и 2 преобразуется в код СОК по и основаниям Р таким, > чтобы S Р/2, где Р = Р; — диапаJ:i зан СОК. Такое требование к Р связано с необходимостью формирования сигнала v переноса (переполнечия через

S) из младшего S-ичного разряда в старший S-ичный разряд. Поскольку основания Р; СОК взаимно простые числа, из которых только одно может быть четным или кратным степени двойки, то невозможно подобрать такое S, которое удовлетворяло бы условию 2

S = P/2 (где, в частном случае, 1 = 8). Поэтому в дальнейшем будем полагать, что S -. Р/2. Наиболее удачным набором оснований СОК для S = 2 является значения Р, = 8, P2 = 5, Р = 13, для которых P = 520, P/2 — 260. Удобство таких оснований состоит и в упрощении преобразователей

1 и 2, поскольку в качестве остатка от двоичного числа по основанию Р

1 — 8 можно взять три его младших двоичнь"х разряда. Тогда преобразователи

1 и ? должны формировать только остатки по основаниям Р = 5 и Р

2 3 — 13. В общем случае добиться такого упрсщения не всегда удается, поэтому чертеж выполнен для общего случая.

Двоичная разрядность основания равна .m = )log P, (где 1(— ближайшее

J 2 большое целое. Так для приведенного набора оснований m = m + m + m

1 т э

3 + 3 + 4 =- 10 бит.

Если преобразователи 1 и 2 выполнять на основе ПЗь(556 серии, та для каждого из них потребуется применить по;.ри корпуса 256х4 бит.

Устройство работает следующим образам.

Режим с аперандами в коде (ОК.

123315 " 4 ну — (S) P по каждому из оснований

СОК. Так, для рассмотренного в материалах заявки набора оснований величина имеет вид S = /О, 1, 9/, т.е.

5 по первому основанию коррекция равна

0 и = 0 n = -1 п = -9, с помою з 3 т щью сигнала v на выходы и коммутаторов12передается либо G,ëèáo б,а свыхода! 5снимается сигнал переполнения.

10 Таким образом, предлагаемое устройство формирует сигнал переполнения, что позволяет ему работать в

СОК, ПОС и с двоичными операндами. формула изобретения

Переключатель 14 режима подает нулевой потенциал. Операнды, представлен ные кодом СОК по и основаниям в виде

А = (о(,, сС»,, ...,о .„) и Ц= (P, Е ...,P ), причем А с.Р, В с Р, по входам 9 и 10 поступают на соответствующие входы сумматоров 7 и 8 первой 5 и второй 6 групп. На выходе сумматоров 7 первой группы 5 формиру ется величина

G = А+ В = (d„,ñl, ...tel ) +

+ (N„p,, ° ° °, p„) °

Выходные сигналы сумматоров 8 вто рой группы 6 в данном случае не используются, поскольку переключатель 15

14 режима обнуляет выход формирования переполнения и на выходы ко1ммутаторов 12 пройдет величина С = G.

Результат суммирования С, как и исходные операнды, представлены остат- gp ками по и основаниям СОК.

Режим с операндами в позиционном (двоичном коде). Переключатель 14 режима не подает нулевой потенциал.

Операнды представленные 1 разряд- 25

1-1 ным двоичным кодом в виде A = о . 2

t=t и В= Ь. 2 причем А

S = 2, где S — величина основания

I системы счисления. Операнды А и В по входам 3 и 4 поступают на первый

1 и второй 2 преобразователи, где они преобразуются в код СОК, каждый 35 по и основаниям. С выходов преобразо.вателей 1 и 2 операнды А и В в коде

СОК А = (< о ° Ыл ) и В (p p ..., p ) поступают на пер вые и вторые входы сумматоров 7 и 8 40 первой 5 и второй 6 групп,. на выходах которых образуются величины G u

С, где

С = А +  — S =- (ol„,ì,...,ot .„) +

Формирователь 11 переполнения формирует сигнал v по правилу

О, если С < S

1, если G > $, 50

Поскольку величина S является константой, то ее вычитание можно учесть при составлении таблиц, по 55 которым выполняются операции в сумматорах 8 группы 6. Эти таблицы рассчитываются со смещением на величиp, если Ч =О тогда С

G, если < =1.

1. Устройство для суммирования, содержащее первую группу из и сумматоров, первые и вторые входы которых являются входами соответственно первого и второго операндов, представленных в системе остаточных классов устройства, о т л и ч а ю щ е ес я тем, что, с целью расширения функциональных возможностей эа счет формирования устройством сигнала переполнения, устройство содержит вторую группу иэ и сумматоров, п коммутаторов, переключатель режима и элемент И, формирователь переполнения и два преобразователя позиционного кода в код системы остаточных классов, первые и. вторые входы первой группы сумматоров соединены соответственно с первыми и вторыми входами второй группы сумматоров, входы преобразователей позиционного кода в код системы остаточных классов являются входами соответственно первого и второго позиционных операндов устройства, а выходы подключены соответственно к первым и вторым входам каждого иэ и сумматоров первой группы, выходы которых подключены к соответствующим входам формирователя перекл ачения и первым информационным входам коммутаторов, вторые информационные входы которых подключены к соответствующим выходам сумматоров второй группы, выходы коммутаторов являются выходом суммы устройства, а управляющие входы коммутаторов подключены к выходу переполнения устройства и выходу элемента И, входы которого подключены к выходу формирователя переполнения и переключателя режима.

2, Устройство по п. 1, о т л и ч а ю щ е е с я тем, что формирователь переполнения содержит п дешиф1233153 раторов двоичного кода в код "1" из

Р, и элементов И, элемент ИЛИ, вы—

J ход которого является выходом формирователя переполнения, входы дешифраторов двоичного кода в код "1" из

Р являются входами формирователя переполнения, одноименные входы элементов И объединены и соединены с выходами соответствующих дешифраторов двоичного кода в код "1" и Р выхоt ды элементов И соединены с входом элемента ИЛИ.

l235 1 53

7á

Составитель F..Åñåíèíà

Техред О.Сопко

Редактор А.Сабо

Заказ 2772/51

Корректор С.Черни

Тираж 671

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4