Устройство для выполнения дискретных ортогональных преобразований

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, в частности к цифровой обработке радио-, гидрои звуколокационных сигналов, и может быть применено при построении быстродействующих процессоров, работающих в условиях жестких временных ограничений . Цель изобретения - увеличение быстродействия за счет представления дискрет преобразуемого сигнала двухстрочными сигналами. Устройство содержит два коммутатора., четыре блока регистров, два умножителя двухрядного кода, пять сумматоров двухрядного кода с соответствующими связями, 5 ил. О 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

|5|1 4 С 06 F 15/332

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3816255/24-24 (22) 23. 11. 84 (46) 23.05.86. Бюл. N - 19 (72) Г.А. Поляков, П. А. Брандис и В. Е. Козлов (53) 681.32(088.8) (56) Авторское свидетельство СССР

Р 875387, кл. G 06 F 15/332, 1981.

Авторское свидетельство СССР

1013971, кл. G 06 F 15/332, 1983. (54) УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНЪ|Х ОРТОГОНАЛЬНЪ|Х ПРЕОБРАЗОВАНИЙ (57) Изобретение относится к вычислительной технике, в частности к циф„„SU„„12331 8 ровой обработке радио-, гидро- и звуколокационных сигналов, и может быть применено при построении быстродействующих процессоров, работающих в условиях жестких временных ограничений. Цель изобретения — увеличение быстродействия за счет представления дискрет преобразуемого сигнала двухстрочными сигналами. Устройство содержит два коммутатора, четыре блока регистров, два умножителя двухрядного када, пять сумматоров двухрядного кода с соответствующими связями.

5 ил.

1 2 3 3 I t .>8

Изобретение относится к вычислительной технике, н частности к цифроно1г обработке радио-, гидро- и знуколокационкьгх сигналов, и может быть применено при построении быстро- 5 действующих процессоров, работающих в условиях жестких временных ограни— чений.

Цель изобретения — увеличение быстродействия за счет представления дискрет преобразуемого сигнала,цвухстрочными кодами.

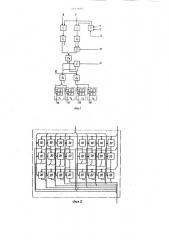

На фиг. 1 представлена функциональная схема умножителя для преобразования Фурье; на фиг. 2 — схема умножителя двухрядного кода для случая m, = .4, m, = 3; на. фиг. 3 — функциональная схема сумматора двухрядного кода; на фиг. 4 — процесс свертывания матрицы частичных произведений в узле свертки с помощью трехвходовых одноразрядных сумматоров; на фиг. 5 — управляющие сигналы, обес. печивающие функционирование устройства.

Устройство (фиг. I) содержит два умножителя 1 и 1 двухрядного кода, 1 сумматоры 2, — 2 двухрядного кода, коммутатор 3, коммутатор 4, сумматор по модулю два 5, восемь регистров 6, 3Q объединенных н блоки 7 — 7,, регистров. Устройство также содержит входы двухстрочного кода мнимой 8 и действительной 9 частей первого и второго

10 элементов преобразуемого сигнала, входы 11 и 12 действительной и мнимой частей коэффициента устройства, первый 13 и второй l4 управляющие входы устройства, вход 15 =àäàíèÿ режима устройства, тактовые входы щб

16 — 19 устройства.

Умножитель двухрядного кода (фиг. 2) содержит элементы И 20.

Сумматор двухрядного кода (фиг.3) содержит слои сумматоров 21, состоя. щие из блоков 22 сумматоров, объеди-. няющих одноразрядные сумматоры 23 одинакового веса. Каждый одноразрядный сумматор 23 имеет прямые шины сумм Я и переносов Р инверсные >пины сумм S и переносов P.

Устройство работает следующим образом.

Базовая операция быстрого преобразования Фурье (БПФ) выполняется за два полутакта, При выполнении прямого преобразонакня Фурье на второй управляющий вход 14 устройства г>ода-, ется нулевой сигнал (при выполнении

О бра т нгп О пр еО Г>р я .> >>н;>>п>я (". t> е- г > т .>т сигнал должен быть единия>н.м), в остальном работа устройства в обоих режимах одинакова.

Рассмотрим режим прямого преобразонания Фурье. В течение перного полутакта на входы днухстрочног0 кода узлов по шинам 8 и 9 поступают двухстрочные коды соответственно мнимой Х В, и действительной R В;частей первого элемента преобразуемого сиг- . нала В, со знаками. На входы 11 и

12 коммутатора поступают однострочные коды действительной и мнимой час. тей коэффициента устройства W соответственно и проходят на однострочные входы первого 1„ и второго 1 узлов. Узлы 1, и 1 формируют многострочные матрицы частичных произведении I В I. W и К В. R W которые по шинам многострочного кода поступают на узлы 2, и 2 соответственно, Виц матрицы частичных произведений и процесс преобразования многострочного кода н узлах 2, — 2 изоб-ражены на фиг. 4.

На второй вход коммутатора 4 поступает нулевой сигнал, а информация на третий узел 2 — с инверсного выхода второго узла 2

Одновременно на третий узел 2 пог!тупает двухстрочный код с перво-. го узла 2,. Полученная четырехстрочная матрица преобразуется н третьем узле 2 в двухстрочный код, что соответствует выполнению операции сложения Re 8 R W + I-ь,В iLW Результаты свертки с прямого и

:инверсного выходов третьего узла 2 поступают на вторые входы соответственно четвертого 2„ и пятого 2 узлов з (в сумматоре по модулю два 5 знак ке изменяется), на первые входы которых поступает двухстрочный код дейстнительнг>й части второго элемента преобразуемого сигнала Л; . многострочные коды К Л +JR В R W +

+ IВ I W и КВ W,— 1 В I M,)преоб— разуются: н соответствующих узлах

2, н 2„до днухстроч ного кода. По тактовым сигналам, поступающим на шины 16 и 18, полученные результаты записываются соответственно н первый и третий блоки регистров.

В течение второго палутакта под

:воздействием единичного сигнала на нходе 13 на входы однострочного кода первого 1, и второго 1, узлов посту1233168

Il;\(AT (()ОТНР 1 Г Т Б(- Н11О Д(Й((ТАИТ(ll I,II;(II !

1 W и мнимая 1 W части коэффици(11е т та устройств». На вход 15 задания рс жима устройства подается едиш(нный сигнал, и на третий узел 2 поступает информация с инверсного выхода второго узла. Двухстрочные коды

I Л; + !1 В(Ке Re8(,I W($

I A — (I B.RW + RB I W) соответе 1 e е ственно с четвертого 2 и пятого 2 10 узлов по тактовым си1 налам, поступа— ющим на шины 17 и 19, записываются во второй и четвертый блоки регист— ров.

Формула изобретения

Устройство для выполнения дискретных ортогональных преобразований, содержащее первый коммутатор, первый и второй информационные входы которого являются соответственно входами реальной и меньшей частей коэффициента устройства, управляющий вход первого коммутатора соединен с тактовыми входами первого и второго бло- ков регистров и является первым тактовым входом устройства, второй так-.. товый вход которого соединен с тактовым входом третьего и четвертого блоков регистров, а первый вход сумма30 тора по модулю два является входом задания режима устройства, о т л и— ч а ю щ е е с я тем, что, с целью увеличения быстродействия, в него введены первый и второй умножители двухрядного кода, первый, второй, третий, четвертый и пятый сумматоры двухрядногб кода и второй коммутатор, выход которого подключен к пер- вому входу первого сумматора двухр Р jill (((1 к()Ц;1 1!рЯ MA(I IlbIX(1j(I((1Т()рог() подключен к второму входу сумматора по модулю два и первому входу второго сумматора двухрядного кода, выход которого подключен к информационным входам первого и третьего блоков регистров, инверсный выход первого сумматора двухрядного кода подключен к первому входу третьего сумматора двухрядного кода, выход второго и четвертого блоков регистров которого подключен к информационным входам, прямой и инверсный выходы сумматора по модулю два подключены к знаковым разрядам первых входов соответственно второго и третьего сумматоров двухрядного кода, вторые входы которого являются входами соответственно реальной и мнимой частей первого операнда устройства, входы мнимой и реальной частей второго операнда соединены с первыми входами соответственно первого и второго умножителей двухрядного кода, выходы разрядов которых подключены к соответствующим входам соответственно четвертого и пятого сумматоров двухрядного кода, выход четвертого сумматора двухрядного кода подключен к второму входу первого сумматора двухрядного кода, а прямой и инверсный выходы пятого сумматора двухрядного кода подключены соответственно к первому и второму информационным входам второго коммутатора, управляющий .вход которого соединен с управляющим входом первого коммутатора, первый и второй выходы которого подключены к вторым входам соответственно первого и второго умножителей двухрядного кода.

77

12 ю 1 °

° ° Ф ° ° Ф ° 4 Ь 1 ° 1

Ф ° ° ° ° Ф ° °

° ° ° 4 4 °

° ° °

° ° Ф ° Ф ° Ф

° ° ° 4 ° ° ° 4 4 ° ° Ф Ф

° ° ° ° ° ° Ь 4

° ° ° 4 Ф °

° °

° Ф ° Ф ° ° ° 4 ° ° ° Ф °

Ф ° ° а Ф ° Ф Ф 4 - ° Ф

Фиг.Ф

Составитель А. Баринов

Редактор С. Саенко Техред Q.cîïêî Корректор С . Шекмар

Заказ 2772I51 Тираж 671 Подписное

PHHHHH Государственного комитета СССР по делам изобретений и открытий

1130 3з, Москва, Ж-35, Раушская наб., д. 4/5

Произволстненнс †полиграфическ предприятие, г. Ужгород, ул. Проектная, 4, И

° ° ° ° 4 ° ° ° 4 ° Ф °

° Ф 4 ° ° ° Ф ° Ф ° Ф

Ф 4 Ф ° ° ° ° °

° ° Ф ° ° 4 Ф

° ° 4 ° ° Ь

° ° ° ° Ф

Farm

Танпь ч игл.