Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, Б частности к технике запоминающих устройств, и может быть использовано в устройствах обработки информации для изменения последовательности следования сигналов валгоритмах преобразования Фурье. С целью повьшения быстродействия устройство дополнительно имеет синхронизатор и четыре регистра, которые позволяют уменьшить время изменения следования элементов входной последовательности чисел. 2 ил. ю W со ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (1I) (50 4 G ll В 21/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3793037/24-24 (22) 21,09.84 (46) 23.05.86 Бюл. 9 19 (72) Е.Л.Полин, Е.Б.Великая, А.В.Дрозд, !О.Г.Клименко и В.С.Волошук (53) 681.327.66(088.8) ,(56) Электроника, 1982, 1(- 13, с. 67.

Электроника, 1983, !(7, с. 62, (54) ЭАПОМИНА!0ЦЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике, в частности к тех— нике запоминающих устройств, и может быть использовано в устройствах обработки информации для изменения последовательности следования сигналов в алгоритмах преобразования Фурье.

С целью повышения быстродействия устройство дополнительно имеет синхронизатор и четыре регистра, которые позволяют уменьшить время изменения следования элементов входной последовательности чисел. 2 ил.

12332!2 гистры по сигналам Пр Р „и Пр Р 1 соответственно. При этом на выходах регистров 9 и 10 считынаются соответственно последовательности чисел г a,a4,а,,аь,а,,а8 и b,,b,Ьэ

b,,Ü,,Ü,b,b . Вторая последовательность чис.ел записывается в первый блок 6 памяти. Блок 6 под действием приходящих на его адресный вход сигналов Адр (с выхода счетчика 5) и на вход запись/чтение сигнала

Зп/Чт (с выхода синхронизатора 1) реализует функцию задержки, обеспечивая считывание указанной последовательнссти через четыре такта с момента ее поступления на его вход.

Считанная последовательность чисел пр»нимается в регистр 11 по сигналу

Пр Р 3, К моменту L появления на выходе регистра 11 числа b, счетчик

5 прин»мает па счетный вход =4 перепадов О/1" сигнала СиСч (начиная с момента установк» счетчика 5 сигналом Сбр) и вырабатывает сигнал считыван»я, под действием которого триггер 3, работающий как Т-триггер, изменяет свое состояние на инверсное.

При этом сигнал Упр.К, поступающий с )зыхода триггера 3 HB управляющий вход кОммутатОра 3,, вызывает его ;и:реключение, в ре-,,:.". тате которогс первый и второй входы оказ ".ваK>T :ÿ подключенными соответственно к второму » первому его выхоцам.

Указанное переключение коммута тора 2 обеспечивает поступлен»е на информационный вход второго блока 7 памяти последовательности а„.а,а а, до момента времени и †.последовав

" ельности Ь„,Ь,,Ьз,Ь, сч»танной с выхода регистра 11 после момента 1.. .";ipQ:" блок 7 памят», рябо-ающий аналогично первому блоку 6 памят», задерживает поступающую .:à его »и— формационный вход послеповательность на (-4 такта, которая далее принимается в регистр 8 (по сигналу ПрРу)

» с его выхода поступает на второй вход регистра 12.

Через второй выход коммутатора

2 на первь:й вход регистра 12 поступают последовательность чисел а,, а,а,,ац. (до момента времени 1.) и b;,Ь6,Ь,Ья (после момента L).

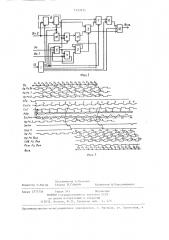

Временные диаграммы (фиг. 2) позволяют проследить работу устройства. И

Входная последовательность чисел поступает на информационные .входы регистров 9 и 10 и принимается в реРегистр 12 является сдвигоным.

ПО налу Пр Р7 „,хв его запись(на ется информация н-нечетные разрядь>

Изобретение относится к вычислительной технике, н частности к технике запоминающих устройств, и может, .быть использовано в устройствах обработки информации, например, для изменения последовательности следования сигналов н алгоритмах преобразования Фурье °

Цель изобретения — повышение быстродействия устройства. 10

На фиг. 1 приведена функциональная схема предлагаемого устройства., на фиг. 2 — временные диаграммы, поясняющие его работу.

Устройство содержит синхрониза- fS тор 1, коммутатор 2, триггер 3, элемент И 4, счетчик 5, блоки 6 и 7 памяти, регистры 8-!2, шину 13 упранления и шину 14 сброса.

Регистр 9 выполнен на двух после- 20 донательно соединенных регистрах.

Устройство работает следующим образом.

Последовательности чисел a,,b, а,Ь,а з,Ьз,а „,Ь,а,,Ь,-, а,Ъ,,а,,Ь,, >5 а,Ъд поступают на информационный вход (Вх.2) устройства, начиная с некоторого числа . Ha вход (Вх.1) устройства подается код величины задержки, определяющ»й глубину переком- g поповки элементов последовательности, например 1 =-4. На шину 14 сброса поступает сигнал, устанавливающии триггер 3 и управляемый им коммутатор 2 в,"-ходное состояние.. Исходное состоя-.. !б нис коммутатора 2 заключается в поцключении первого и второго входов соотвел ственно к его первому и второму выходам, Кроме того, через элемент И 4 сигнал сброса обеспеч»вает прием в счетчик 5 кода g . На вход синхронизатора 1 поступает сигнал типа меандр . Синхронизатор 1 вырабатывает си. :- алы Реж. Р,„,„, Пр Р, 45

Пр Р 3, Пр Р,„, поступающие соответственно на синхровходы регистров 812, входы запись/чтение блоков 6 и

7 памяти и на счетный вход счетчика

5. Эти сигналы (фиг. 2) получены из

50 входного сигнала синхронизатора 1 путем задержки на. логических элементах (повторителях, инверторах).

1233212 через первый вход и в четные разряды через второй вход, выходная информация снимается с нечетных выходов регистра .)2.

Следовательно, по сигналу Пр Р аы„ на выходе устройства считываются. элементы последовательности а ...а,а,,а

b<,b,b>,b„, а по сигналу С,Р,„„„ с учетом сигнала режима Реж Р „,„осуществляется сдвиг содержимого регистра 12 на один разряд и на выходе считьгваются элементы последовательности а„,а,а,а,Ь„,Ь,Ь.,Ь, . Таким образом, на выходе устройства считывается последовательность а,а,,а,а г,аз,ад,а4,Ь,Ь1,ЪБ,Ь,,Ь,,Ьз Ьв,Ь

Коммутатор 2 имеет поразрядную однородную структуру. Каждый разряд коммутатора 2 реализуется на элементах И и ИЛИ.

Счетчик 5 изменяет свое состояние е приходом на счетный вход сигнала

СИС1 (перепада "О/!"). Сигнал считывания вырабатывается 11ри нулевом состоянии счетчика 5 и перепаде сигнала 25

CuCv "1/О", Сигнал считывания через элемент И 4 обеспечивает прием в счетчик 5 кода . Выход счетчика 5 принимает значение состояния счетчика по г1ерепаду "1/О" сигнала Си1.

Сигнал Си1 является сдвинуть1м па фазе сигналом СиСч и обеспечивает выработку адреса Адр.

По сравнению с известным устройством предлагаемое позволяет умень35 шить время изменения следования элементов входной последовательности чисел, что находит применение при реализации алгоритмов преобразования Фурье, вторым входом, и шину управления, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены синхрапизатор, второй, третий, четвертый и пяты11 регистры и коммутатор, вы5 хад которого соединен с вторым входам второго блока памяти, третий вход второго блока памяти соединен с первым выходам синхронизатора, второй и трстпй 1зыхады которого соединены с первым и вторым входами второго регистра, третий вход второ го регистра ягляется вторым информационным входом устройства, выход второго регистра саеди11ен с первым Вхо дам коммутатора, первый вхац третьего регистра соедине с третьим 1зходом второго регистра,,второй вхсд которого соединен с третьим выходом с11нхраппзатара, выход третг его регистра сасдппе с Hl арым входом первого алака памяти» Бь!хОд ХОТО1эага саедппеп с первым входам четвертого регистра, второй хад которого сoe.— дипен с четвертым выходам спнхрапп— затора, I:hIõoä .Отпертого регистра соединен с вторым входом коммутатора, третий иха., катсрага соединен с

Вторым выходом триггсра, третий вхоц тРИ1 ГЕРа СОЕДзП1ЕН С 1ЗтаРЫМ ВЫХаДОМ счетчика, в горой в"ад пср1зсга регистра и перг1ый 1зхад пятага регистра соединены соответственно с пятым и шес Гым ВыхОдами CIIHxpОнизGTopclр вхОд которого соединен с шиной управления, второй вход пятого регистра соединен с вторым выходом коммутатора, выход первого регистра соединен с третьим входом пятого регистра, выход которого является выходам устройства.

45

Формула изобретения

Запоминающее устройство, содержащее первый блок памяти, первый вход которого соединен с первым выходом счетчика и с первым входом второго блока памяти, элемент И, первый вход которого соединен с первым входом триггера и шиной сброса, второй вход элемента И соединен с вторым выходом счетчика, первый вход которого является первым информационным входом устройства, второй вход счетчика соединен с выходом элемента И, выход второго блока памяти соецинен с первым входом первого регистра, первый выход триггера соединен с его

)2332)2 а, Ь, а, Ь, а, 4 о, Ь 5 4 > Ье Ь ae >a г 3 Ье. ЬЗ ьц Ь&- М437 4ЮГ О

С с г-- =х=

Ги! 1 Г \..Г l " Ъ вЂ” d — l.--l 1.— т 1 Г 1 Х

3n /um " з Хг — 1 гз- . .ю -а зу у.ч ю — чав

С Cv Сч С С» Сч Lv t:v ev Cv

". 1, „ 6 . иПдpzз — г-) .г — г г : Р. ю —

Заев 1

Уп /1 пц 7 а .а, аз -0v > Ьг -lyz пр П вЂ” л — г-г — = ..-" — .х ==а - -.a -.

-tts «аа ат «По Ьр Ьд» Ь Ь8 (7р Ре был

Гдд Ре Й/)(— аЛ - --тЛ= :Р . " а3 =сРPP2K Pc", д

О t> 3 2 1 D Ч --J "I.- Г 1-U

О„- а п, "-z Р з Яв а„й Ь, >s hz Д, >y ghq.

9 -р --,Р .=.- .. У- — „ь — @ .@в @ @ @=ф л Щ р, Ных.

Составитель A.Âîðîíètt

Редактор О.Бугир Техред И.Гайдол Корректор М.Максими пинец

Заказ 2777/54

Тираж 543 Пс днис все

ВИИИПИ Государственного комитета СССР

t1o делам изобретений и открытий

113035, Москва, >К-3, Раушская наб., д. 4/5

Производственно — полиграсрическое предприятие, г. Ужгород, y!t. Проектная, 4