Динамическое оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычиолительной техники, в частности к запоминающим устройствам динамического типа, и может быть использовано в цифровых вычислительных машинах , системах сбора и обработки данных , системах отображения информации. Целью изобретения является повьшение надежности устройства. Устройство содержит блок памяти и контроллер регенерации , который содержит ключ, элемент 2 ИЖЬНЕ, генератор импульсов , триггер, таймер и счетЧик, Контроллер регенерации обеспечивает регенЬрациго динамического запоминающего устройства в случаях, когда частота обращений ниже допустимой. I з.п. ф-лы, 2 ил. ю 00 00 ND 14)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (Ш 511 4 С 11 С 11/ОО

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

1 /

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1019493 (21) 3511013/24-24 (22) 10.11.82 (46) 23.05.86. Бюл. Ф 19 (72) Ю.П.Кудреватых (53) 681.327.6(088.8) (56) Авторское свидетельство СССР

У 1019493, кл. G 11 С 11/00, 1982. (54) ДИНАМИЧЕСКОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ. УСТРОЙСТВО (57) Изобретение относится к области вычиолительной техники, в частности к запоминающим устройствам динамического типа, и может быть использовано в цифровых вычислительных машинах, системах сбора и обработки данных, системах отображения информации.

Целью изобретения является повышение надежности устройства. Устройство содержит блок памяти и контроллер регенерации, который содержит ключ, элемент 2 ИЛИ-НЕ, генератор импульсов, триггер, таймер и счетчик, Контроллер регенерации обеспечивает регенерацию динамического запоминающего устройства в случаях, когда частота обращений ниже допустимой. l з.п. ф-лы, 2 ил.

1233213 3 ь риод ооращения в М.N раз меньше периода регенерации (М вЂ” число строк накопителя, например, 128 у 565 РУЗ;

Ч вЂ” число групп накопителей) при условии обращения к данному ЗУ или период обращения в М раз меньше периода регенерации при условии обращения к другим ЗУ, импульсы обращения проходят через элемент 2ИЛИ-НЕ 4, откры1О вают транзистор raAMepa,, конденсатор

RC-цепи периодически разряжается и напряжение на нем не превышает пороГовое, таким образом, таймер 7 не вырабатывает импульс установки триг1l5 гера 6„ и сигнал с прямого выхода триггера 6 устанавливает ключ 3 в состояние, при котором импульсы обращения поступают .Га ДЗУ 1, и регенерация и обращение к ДЗУ 1 осуществля20 ется такии же образом, как и в известном устройстве. Инверсный сигнал с выхода триггера 6 удерживает счетчик 8 в нулевом состоянии.

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам (ЗУ) динамического типа, может быть использовано в различных .цифровых вьгчислительных машинах, системах сбора и обработки данных, системах отображения информации и является усовершенствованием устройства по основнбму авт.св. М 1019493.

Цель изобретения — повышение надежности устройства.

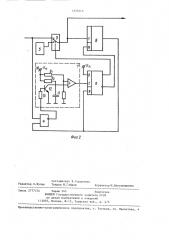

На фиг ° 1 изображена структурная схема предлагаемого устройства, на фиг. 2 — структурная схема контроллера регенерации и пример конкретной реализации таймера.

Устройство содержит динамическое запоминающее устройство (ДЗУ) 1 и контроллер 2 регенерации. Контроллер 2 регенерации содержит электроннь|й ключ 3, элемент 2ИЛИ-HE 4, генератор 5 импульсов, триггер 6, таймер 7 и счетчик 8, Таймер 7 представляет собой компаратор напряжения, выход которого является выходом таймера. На инверсный вход компаратора .подается пороговое напряжение с резистивного делителя 9 напряжения, а на прямой вход — экспоненциально возрастающее напряжение со средней точки последовательно включенной КС-цепи, вывод резистора которой п к источнику 10 питания, а вывод конденсатора 11 — c общему проводу. Средняя точка этой

RC-цепи подключена, кроме того, к коллектору ключевого транзистора 12,l эмиттер которого подключен к общему проводу, а база через ограничительный резистор 13 — к выходу элемента

2ИЛИ-НЕ 4.

Б качестве элемента 2ИЛИ-НЕ 4, триггера 6, счетчика 8, генератора

S могут быть использованы логические элементы интегральных микросхем, например, 564 серии. Электронный ключ 3 легко реализуется на ключах той же серии, например 5641(T3. В качестве таймера 7 может использоваться интегральный таймер КР1006ВИ1 или он может быть реализован с использованием дискретных элементов и компаратора напряжения, например, 52!СЛЗ.

У"тройство работает следующим образом.

При частоте обращения, удовлетворяющей условию регенерации, т.е. пе25

При остановке процессора или в случаях, когда частота поступления сигналов обращения меньше„ чем необходимо дпя регенерации, кочденсатор таймера 7 успевает зарядиться до порогового напряжения, и при превышении порогОвоГО напряжения КОмпаратор таймера вырабатывает сигнал, устанавливающий триггер 6 в состояние, соответствующее прохождению импульсов

35 с генератора 5 через ключ 3 на ДЗУ I и счетный вход с:етчика 8, который в этом случае начинает счет, так как сигнал с инверсного выхода триггера

6 ра= решает счет. При поступлении

4П на вхоц счетчика 8 необходимого числа импульсов (число импульсов равно ислу строк накопителя ДЗУ 1 с максимальным числом строк) сигнал с выхода счетчика 8 сбрасывает триггер 6

45 и .проходя через элемент 2ИПИ-Н".". 4, a таймер 7„ переводит его в ис; одsac состояние, разряжая через резистор !2 конденсатор 11. Ключ 3 перекгпочается и разрешает прохождение на

50 дЗ . c"òíaëoa обращения, а инверсI 5 ныи сигнал с выхода триггера 6 запрещает счет счетчику 8.

Таким образом, контроллер регенерации обеспечивает регенерацию ДЗУ в режимах осталова в случаях, когда частота обращений ниже допустимой, что повышает надежность устройства.

1233213

Формула изобретения

1, Динамическое оперативное запоминающее устройство по авт.св °

9 1019493, о т л и ч а ю щ е е с я 5 тем, что, с целью повьппения надежности, оно содержит контроллер регенерации, состоящий из элемента

2ИЛИ"НК, генератора импульсов, триггера, счетчика, таймера и ключа, 10 первый вход которого является входом обращения устройства и соединен с первым входом элемента 2ИЛИ-НЕ, второй вход ключа подключен к выходу ге- . нератора импульсов, а управляющий 15 ,вход ключа подключен к прямому выходу триггера, вход установки которого соединен с выходом таймера, вход которого соединен с выходом элемента

2ИЛИ-НЕ, второй вход которого соеди- 20 нен с входом сброса триггера и выходом счетчика, счетный вход которого подключен к выходу ключа и является выходом контроллера регенерации, вход сброса счетчика подключен к инверсному выходу триггера.

2. Устроиство по п, 1, о т л ич а ю щ е е с я тем, что таймер содержит компаратор напряжения, выход которого является выходом таймера, источник порогового напряжения на резистивном делителе напряжения, к которому подключен инверсный вход компаратора напряжения, прямой вход которого подключен к средней точке дифференциальной цепочки, один из выходов которой подключен к источнику питания, а другой — к общей шине, средняя точка дифференциальной цепочки подключена к коллектору ключевого транзистора, эмиттер которого соединен с общей шиной, а база — с одним выходом ограничительного резистора другой выход которого является входом таймера.

f 2332! 3

Составитель В.Гордонова

Редактор О.Бугир Техред И.Гайдош Корректор N.Nàêñèìèøèíåö

Заказ 2777/54

Тираж 543 Подлисное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4