Многоканальный цифро-аналоговый преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и телемеханики и позволяет повысить надежность преобразования кода в аналоговый сигнал при большом количестве каналов за счет упрощения каждого из m канальных преобразователей 3, число га которых определяет надежность многоканального цифроаналогового преобразователя.. Все канальные преобразователи 3 работают одинаково. Сигнал с входных шин записывается последовательно в элемент 6 памяти, а затем поступает в виде последовательного кода на вход источника 7 тока. Время считывания каждого разряда на выходе элемента 6 памяти, определяемое формирователем 5 сигналов управления, пропорционально его относительной величине. С выхода источника 7 кода снимается аналоговьй сигнал, постоянная составляющая которого пропорциональна значению входного кода. При поступлении нового значения входного кода блок 2 управления разрешает запись входного кода в элементы 6 памяти в последовательности , которая задается сигналами с пульта 4 диспетчера. 3 з.п. ф-лы, 2 ил. (Л к t ьэ оо 00 ю 00 4 Н npu5ttfJij т

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

gg 4 Н 03 М 1/66

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H А ВТОРСКОЮУ СВИДЕТЕЛЬСТВУ (21) 3801095/24-24 (22) 16. 10.84 (46) 23.05.86 . Бюл . ¹ 19 (71) Специальное конструкторско-технологическое бюро "Промавтоматика" (72) М.Л.Портнов (53) 681.325(088.8) (56) Авторское свидетельство СССР

¹ 1046927, кл. Н 03 К 13/02, 1982.

Авторское свидетельство СССР № 84 1006, кл . G 08 С 19/28, 1979. (54) МНОГОКАНАЛЬНЫЙ ЦИФРО-АНАЛОГОВЫЙ

ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к области автоматики и телемеханики и позволяет повысить надежность преобразования кода в аналоговый сигнал при большом количестве каналов за счет упрощения каждого из m канальных преобразователей 3, число m которых определяет надежность многоканально„„SU„„1233284 д1 го цифроаналогового преобразователя.

Все канальные преобразователи 3 работают одинаково. Сигнал с входных шин записывается последовательно в элемент 6 памяти, а затем поступает в виде последовательного кода на вход источника 7 тока. Время считывания каждого разряда на выходе элемента 6 памяти, определяемое формирователем 5 сигналов управления, пропорционально его относительной величине.

С выхода источника 7 кода снимается аналоговьй сигнал, постоянная составляющая которого пропорциональна значению входного кода. При поступлении нового значения входного кода блок 2 управления разрешает запись входного кода в элементы 6 памяти в последовательности, которая задается сигналами с пульта 4 диспетчера. 3 з.п. ф-лы, 2 ил.

33284

5 !

20

55

1 12

Изобрете ние относится к области автоматики и телемеханики, в частности к таким системам телемеханики, в которых телеметрическая информация, принимаемая из линий связи в виде кодов, должна воспроизводиться аналоговыми приборами.

Цель изобретения — повышение надежности устройства за счет исключения регистра и элементов И и ИЛИ в каждом из канальных преобразователей, определяющих надежность многоканального цифро-аналогового преобразователя при большом количестве каналов.

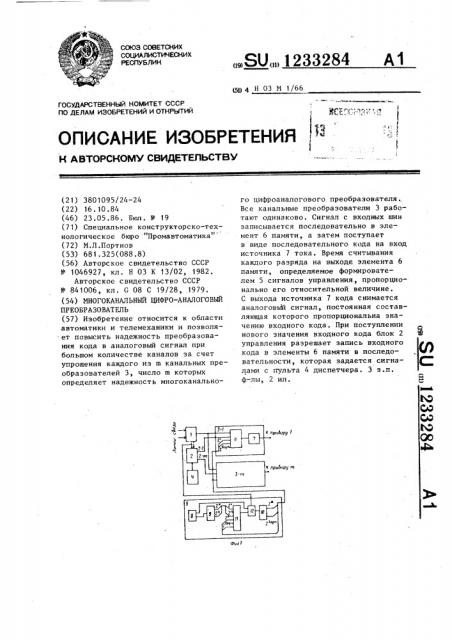

На фиг. 1 изображена функциональ ная схема предлагаемого устройства; на фиг. 2 — возможные схемы реализапии блоков приема и управления.

Устройство содержит блок 1 приема, блок 2 управления, канальные преобразователи 3-1,...,3-m для управления m приборами, пульт 4 диспетчера, формирователь 5 сигналов управления, входящие в состав канальных преобразователей 3 элементы памяти, выполненные на регистре 6 сдвига, и источ— ники 7 тока, а также входящие в состав формирователя 5 сигналов управ— ления генератор 8 тактовых импульсов, первый 9 и второй 10 счетчики, мультиплексор 11 и коммутатор 12.

Первый и второй входы блока 1 приема являются первой и второй входными шинами. Первый выход блока 1 приема соединен с первым входом блока 2 управления, вторые выходы которого подключены к выходам пульта 4 диспетчера. Каждый из выходов блока 2 управ ления соединен с соответствующим входом разрешения записи регистра 6 сдвига, информационный вход каждого из которых соединен с вторым вьгходом блока 1 приема. Выходы формирователя 5 сигналов управления соединены с адресными входами каждого регистра 6 сдвига, выход которого подключен к входу источника 7 тока, выход которого является выходной шиной.

Первый и второй выходы генерато— ра 8 тактовых импульсов соединены соответственно с первым входом коммутатора 12 и входом первого счетчика 9, выходы которого соединены с соответствунлцимтт информационными входами му.ттт.типлексора 11 . Выход мультиплексора 11 подключен к второму входу коммутатора 12, третий вход к< торое (1 л яляется входом (1)ор тттротта Гет«т

25 ся третьим выходом блока 1 приема.

Блок 2 управления содержит регистр 17 сдвига, m регистров 18 адресов и m компараторов !9. Вход регистра 17 сдвига является первым входом блока 2 управления. Выходы регистра 17 сдвига подключены к первым входам компараторов 19. Вторые входы блока ? управления через соответствующие регистры 18 адресов соединены с вторыми входами соответствующих компараторов 19. Третий вход каждого компаратора 19 объединены и являются третьим входом блока 2 управления.

Выход каждого компаратора 19 является соответствующим выходом блока 2 управления.

Устройство работает следуюпатм образом.

На входные шины блока 1 приема из линии связи поступает последова— тельный код, содержащий информационную и адресную части. Блок 1 разделяет принимаемые данные и наттравттяет последовательный информационный код на вход регистров 6 сдвига всех канаттьных преобразователей 3-1,...,3-m.

Адрес ная информация на пра вля етс я из блока 1 приема через первый выход на вход блока 2 управления, который в соответствии с данными, введенными н него с пульта 4, формирует сигнал "1" на одном На Bb!х.дсв 2 — 1,..., "— ш б.-тс ка 2 управления ., «г!!a.!!!

3 1233 с шин 2-1,...,2-m подаются на входы разрешения записи в регистры 6 сдвига.

Одновременно сигнал разрешения от блока 1 приема подается на коммутатор 12 формирователя 5 сигналов

5 упра вления . Зтим обеспечивается прохождение на второй счетчик 10 импульсов с первого выхода генератора 8.

Частота этих импульсов равна частоте

1О сигналов в линии связи. Выходы счетчика 10 соединены с адресными шинами регистров 6 сдвига и определяют адреса разрядов, куда последовательно заносятся принимаемые из линии связи

15 сигналы.

Пель установки нулевой позиции первого счетчика в начале выдачи информационного кода иэ блока 1 не показана.

После завершения приема информации в выбранный регистр 6 сдвига с выхода 2-1,...,2-m снимается сигнал " 1", чем восстанавливается режим считывания данных, хранимых во всех

25 регистрах 6 сдвига. Адресные сигналы, определяющие номер разряда, от которого информация подается на выход каждого регистра 6, как и в режиме записи, задаются вторым счетчиком 10.

Однако, в режиме считывания сигнал от блока 1 на коммутатор 12 не подается, и на выход коммутатора проходят сигналы, образуемые на выходе мультиплексора 11. Мультиплексор 11 пропускает на выход сигнал с входа, 35 адрес которого задан кодом на его входах управления, т.е. кодом состояния второго счетчика. На входы мультиплексора подаются сигналы с выхода первого счетчика 9, число разрядов которого (a следовательно, и число входов мультиплексора) равно п числу разрядов кода, преобразуемого канальными преобразователями 3 в аналоговые сигналы. Число входов управления,4 а следовательно, и число разрядов во втором счетчике 10 равно двоичному логарифму преобразуемого кода.

Соединения между выходами первого счетчика 9 и входами 11 сделаны так, что при нулевой комбинации сигналов на выходе второго счетчика 10 на выход 11 проходит сигнал с выхода разряда 2" первого счетчика 9. Переключение второго счетчика 10 в следующие позиции происходит при появлении сигнала "1" на. выходе 11. Следовательно, переход иэ нулевой позиции

284 4

B первую пр >исх цит при поступлении на вход перногс> счетчика 9 2" импульсов от генератора 8. После переключения счетчика 10 в первую позицию очередной сигнал "1" на выходе мультиплексора 11 образуется при поступленни от генератора 8 очередных 2":2 импульсов ° В этот момент второй счетчик переключается во вторую позицию.

Аналогичным образом счетчик 10 переключается на остальные позиции. Из описанного видно, что время удержания второго счетчика 10 на каждой позиции изменяется в точном соответствии с весами соответствующих раэрядов кода — на нулевой позиции (соответствует сканированию старшего разряда кода) счетчик 10 удерживается в течение половины периода заполне-, ния счетчика 9, на первой позиции в течение четверти периода и т.д. Так как код состояния второго счетчика 10 определяет и адрес выборки сигналов из регистра 6 сдвига, то на выходе регистра 6 сдвига образуется в режиме считывания данных последовательный код весовых импульсов, набор которых соответствует записанному коду, т.е. отношение суммарной длительности импульсов, образованных в регистрах 6, к периоду повторения сигналов на выходе счетчика 9 отображает принятый код. С помощью источника 7 тока, рассчитанного на номинальный ток отклонения стрелки выходного прибора, последовательный код преобразуется в ток, среднее значение которого соответствует принятому коду. Период повторения сигналов на выходе счетчиков 9 и 10 должен быть достаточно малым (т.е. достаточно высокой должна быть частота импульсов на втором выходе генератора 8), чтобы исключить колебания стрелки выходного прибора.

Следует отметить, что при записи новых данных в какой-либо канальный преобразователь на адресные шины всех регистров 6 сдвига подается вместо последовательности, изменяюtt щейся через неравные (весовые ) промежутки времени, последовательность с равномерно изменяющимися кодовыми комбинациями (с частотой, равной частоте сигналов на первом выходе генератора 8). В связи с тем, что время записи новой информации значительно меньше инерционности аналоговых приборов, ощутимых воздействий на отображаемую информацию смена последова1233?84 тельности адресных сигналов не оказывает.

Основу блока 1 составляют распре— делители 13 и 14. Распределитель 14 устанавливается в начальное состояние по сигналу синхронизации от распределителя 13. Распределителем 14 формируются тактовые сигналы, участвующие в приеме и обработке информа- 1р ции. Структура рабочего цикла определяется временной диаграммой конкретного телекомплекса. Выходные сигналы

Х и Y второго распределителя определяют начало и конец приема информационной части сообщения. С помощью триггера 15 образуется сигнал разрешения выдачи из блока 2 сигналов

2-1,...,2 †и подключения к счетчику 10 сигналов от генератора 8 (ра- 2О ботающего синхронно с распределителем). Сигнал "1" от триггера 15 поступает на первый выход блока 1 после завершения ввода адресной части сообщения. 25

Последовательный код — адресная часть сообщения — выделяется элементом И 1б, на который подается выходной код от распределителя 13, и сигнал от триггера 15 и подается с второго выхода на вход блока 2. Сигнал разрешения с первого выхода, кроме того, подается на блок 5.. !

Блок 2, например, содержит общий регистр 17 сдвига — преобразователь последовательного кода адреса в параллельный, индивидуальные для каждого канала регистры 18.1,...,18.m адресов, задаваемых органами управления (например, общими для всех ка- 40 налов ключами задания адреса и индивидуальными кнопками выбора адреса канала) пульта 4 диспетчера и индивидуальные компараторы 19.1,...,,19.m, сравнивающие параллельные коды, записанные в регистр 17 и регистры

18.1,...,18.m. Выходные сигналы

2-1,...,2-m формируются при подаче на все компараторы 19 параллельно сигнала разрешения от блока 1, т.е. после завершения ввода в регистр 17 всей адресной части. Разрядность регистров 17 и 18 одинакова и зависит от числа параметров, которые могу, быть приняты и выданы на отображение.55

Сигнал логической "1" формируется на одном или нескольких выходах 2.1,..., 2-тп, если записанные в реги тры

18. 1,... „18.m адреса совпадают с текущим адресом, записанным в регистр 17

Формула изобретения

1. Многоканальный цифроаналоговый преобразователь, содержащий пульт диспетчера, m канальных преобразователей, каждый из которых выполнен на элементе памяти и источнике тока, выход которого является выходной шиной, блок управления и блок приема, первый и второй выходы которого являются первой и второй входными шинами соответственно, первый выход соединен с первым входом блока управления, вторые входы которого подключены к выходам пульта диспетчера, каждый из выходов — к соответствующему входу разрешения записи элемента памяти, информационный вход каждого из которых соединен с вторым выходом блока приема, отличающийся тем, что, с целью повышения надежности, в него введен формирователь сигналов управления, а в каждом канальном преобразователе элемент памяти выполнен на регистре сдвига, выход которого соединен с входом источника тока, причем третий выход блока приема соединен с третьим входом блока управления и входом формирователя сигналов управления, выходы которого подключены к адресным входам регистров сдвига.

2. Преобразователь по п. 1, о тл и ч а ю шийся. тем, что формирователь сигналов управления выполнен на двух счетчиках, мультиплексоре, коммутаторе и генераторе тактовых импульсов, первый и второй выходы которого соединены соответственно с перBblM входом коммутатора и входом первого счетчика, выходы которого соединены с соответствующими информационными входами мультиплексора, выход которого подключен к второму входу коммутатора, третий вход которого является входом формирователя сигналов управления, а выход соединен с входом второго счетчика, выходы которогo подключены к адресным входам мультиплексора и являются выходами формирователя сигналов управления.

3. Преобразователь по п.1, о т л и ч а ю шийся тем, что блок приема выполнен на двух распределиФиг. 2

Составитель А.Симагин

Техред О.Сопко Корректор Е.Сирохман

Редактор А.Сабо

Заказ 2782/57 Тираж 816 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Óæãoðîö, ул.Проектная, 4. телях импульсов, триггеpt. и зле;н нте И, причем первый и втоp()A входы первого распределителя импульсов являются. первым и вторым входами блока

5 приема, информационный выход перво го распределителя импульсов соединен с первым входом элемента И и являет— ся выходом блока приема, выход синхронизации — с входом второго распре- 1О делителя, первый и второй выходы которого подключены соответственно к первому и второму входам триггера, прямой выход которого является третьим выходом блока приема, инверсный выход соединен с вторым входом элемента И, выход которого является первым выходом блока приема.

4. Преобразователь по и. 1, о тл и ч а ю шийся тем, что, блок управления выполнен на регистре ..дви— га, в регис.трах адресов и тп компараторах, при этом первым входом блока управления является вход регистра сдвига, выходы которого подключены к первым входам m компараторов, вторыми входами блока управления являются входы регистров адресов, выходы каждого из которых соединены с вторыми входами соответствующего компаратора, третьи входы компараторов объединены и являются третьим входом блока управления, а выходы являются соответствующими выходами блока управления.