Устройство для распределения заданий процессорам

Иллюстрации

Показать всеРеферат

Устройство для распределения заданий процессорам откосится к области вычислительной техники и может быть использовано при организации вычислительного процесса по обработке пакета информационно-связанных заданий в многопроцессорной (многомашинной ) вьтислительной системе. Цель изобретения - повышение быстродействия . Указанная цель достигается тем, что устройство содержит блок памяти (матрицу триггеров), шифратор, две группы элементов ИЛИ-НЕ, две группы триггеров, группу элементов И и группу элементов ИЛИ с соответствующими связями. Новым в .устройстве является то, что в него введена группа регистров. Устройство может функционировать в режиме, при котором обеспечивается реализация пакета информационно-связанных задач с минимальным средним временем ответа для заданий данного пакета. 1 ил. f СП

Г

> (Я) 4 G 06 F 9/46 у

ОПИСАНИЕ ИЗОБРЕТЕНИЯ / ,у +... ;А" с, l, ;» . Й СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ вЂ” РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСНОМУ СВИДЕТЕЛЬСТВУ (21) 3820902/24-24 (2?) 06.12.84 (46) 30.05,86. Бюл. М 20 (72) С.М.Баженов, С.Г.Баринов, В.Л.Гайдуков и С.Д.Прудских (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 664175, кл. G 06 F 15/20; 1976.

Авторское .свидетельство СССР

6 - 1001101, кл. С 06 F 9/46, 1983. (54) УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ

ЗАДАНИЙ ПРОЦЕССОРАМ (57) Устройство для распределения заданий процессорам относится к области вычислительной техники и может быть использовано при организации вычислительного процесса по обрабо1„„SU „„ 1234 ÝÀ 1 ке пакета информационно-связанных заданий в многопроцессорной (многомашинной) вычислительной системе.

Цель изобретения — повышение быстродействия. Указанная цель достигается тем, что устройство содержит блок памяти (матрицу триггеров), шифратор, две группы элементов ИЛИ-НЕ, две группы триггеров, группу элементов И и группу элементов ИЛИ с соответствующими связями. Новым в .устройстве является то, что в него введена группа регистров. Устройство может функционировать в режиме, при котором обеспечивается реализация пакета информационно-связанных задач с минимальным средним временем ответа для заданий данного пакета. 1 ил.

Устройство относится к вычислительной технике и может быть использовано при автоматизации выбора очередной программы, задания из информационно-связанного набора программ, заданий для решения в управляющей многопроцессорной вычислительной системе, Бель изобретения — повышение быстродействия устройства.

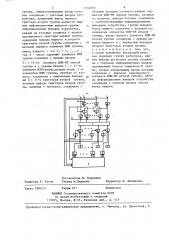

На чертеже изображена структурная схема устройства.

Устройство содержит группу информационных выходов 1 устройства, блок

2 памяти, группу элементов ИЛИ-НЕ 3, группу регистров 4, группу триггеров

5, группу блоков элементов И 6, шифратор 7, группу триггеров 8, группу элементов ИЛИ 9, группу элементов

ИЛИ-НЕ 10, тактовый вход 11 устройства.

Устройство работает следующим образом.

Первоначально в блок 2 заносится информация о топологии моделируемого графа, информационно-связанного пакета заданий (матрица смежности графа), триггеры 5 и 8, регистры 4 находятся в нулевом состоянии. На регистры 4 заносятся веса соответствующих вершин, заданий. Число выходов шифратора и устройства соответствует числу столбцов матрицы смежности, т.е. числу вершин, заданий. Число групп выходов блока 2 памяти соответствует числу строк матрицы смежности, т.е. также числу вершин, задании. Число выходов блока 2 памяти в группе также соответствует числу вершин, заданий.

После занесения исходной информации на выходе хотя бы одного из элементов ИЛИ-НЕ 3 будет высокий потенциал. Это объясняется тем, что в однонаправленном графе без циклов и петель первые вершины не содержат входящих ветвей, т.е. в графе обязательно существуют вершины (задания), готовые к работе.

Одновременно высокий потенциал с выхода устройства поступает на одноименный вход блока 2 памяти, которым обнуляется соответствующий столбец матрицы смежности, и устройство автоматически подключает на шифратор внось появившиеся готовые вершины, задания.

Время работы устройства значительно меньше времени решения задания и поэтому после окончания его выполнения тактовым сигналом 11 практи4 чески будет зафиксирован на выходе устройства код следующего задания.

Ф ор мула из об ре те ния

Устройство для распределения заданий процессорам, содержащее блок памяти, шифратор, группу блоков элементов И, первую и вторую группы элементов ИЛИ-НЕ, первую и вторую группы триггеров и группу элементов ИЛИ, причем нулевые выходы триггеров первой группы соединены с первыми управляющими входами одноименных блоков элементов И группы, выходы которых соединены с соответствующими входами группы входов шифратора, информационные выходы которого соединены с единичными входами одноименных триггеров второй

Таким образом, первоначально в устройстве происходит выявление заданий, готовых к работе, элементами

ИЛИ-НЕ 3. Коды весов этих заданий с регистров 4 через элементы Й 6 по сигналам с выходов элементов ИЛИ-НЕ

3 передаются на соответствующие входы информатора 7, где выбирается из них задание с мен..шим весом, и на

234839 2 соответствующем ему выходе шифратора появляется высокий потенциал, который обеспечивает по тактовому сигналу 11 устройства перевод одноименного триггера 8 в единичное состояние.

В результате на триггерах устанавливается код, содержащий набор нулей и одну или несколько единиц. После

10 этого тактовый сигнал должен быть снят, Наличие элементов ИЛИ 9 и ИЛИ-НЕ

10 обеспечивает появление высокого потенциала только на одном из выходов !

5 устройства, что необходимо при появлении единичного сигнала одновременно на нескольких триггерах 8. Высокий потенциал соответствует позиционному номеру очередного задания информаци20 онно-связанного пакета, которое должно затем решаться процессором ВС. Преимущественное право выбора имеет задание с меньшим позиционным номером.

-Одновременно в единичное состояние

25 перебрасывается одноименный триггер

5, и перекрывается тем самьпч проход соответствующего веса на шифратор.

4839

Составитель M. Кудряшев

Техред М.Ходанич Корректор Л. Пилипенко

Редактор E. Копча

Заказ 2986/51.

Тираж 671

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 123 группы, синхронизирующие входы которых соединены с тактовым входом устройства, единичный выход первого триггера второй группы является первым информационным выходом группы информационных выходов устройства, каждый из которых соединен с входом одноименного триггера первой группы, единичные выходы первого и второго триггеров второй группы соединены с 10 входами первого элемента ИЛИ группы, Bbfxop каждого 1 - о (i = 1 ° ..., и где h — число заданий) элемента ИЛИ группы соединен с первым входом

1 15 (1 + 1)-го элемента ИЛИ-HE первой группы и с первым входом (i + 1)-го элемента ИЛИ группы,вторые входы i -х элементов ИЛИ группы, начиная со второго, соединены с единичными выходами (i + 1)-х триггеров второй группы,, нулевые выходы триггеров второй группы, начиная с третьего, соединены с вторыми входами соответствующих эле.— ментов ИЛИ-HE первой группы, начиная . со второго, выходы которых соединены . с соответствующими информационными выходами устройства, группы выходов блока памяти соединены с входами одноименных элементов ИЛИ-HE второй группы, входы первого элемента ИЛИ-НЕ второй группы соединены с прямым выходом первого и с инверсным выходом второго триггеров второй группы, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия, оно содержит группу регистров, причем выходы регистров группы соединены с группами .информационных входов одноименных блоков элементов И группы, вторые управляющие входы которых соединены с выходом одноименного элемента ИЛИ-НE второй группы, группа информационных выходов устройства соединена с группой входов сброса блока памяти.