Ячейка памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и является усовершенствованием ячейки памяти по авт. св. № 1095243. Цель изобретения состоит в повышении вероятности правильного воспроизведения информации при перерьшах питания. Ячейка памяти содержит триггер и накопительные элементы на конденсаторе и трансформаторе . Введение ключевого элемента в состав ячейки памяти позволило стабилизировать процесс переключения накопительного элемента на трансформаторе при включении напряжения питания . 1 ил. tsD СО 4 00 00 оо ISO

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (51) 4 G 11 С 19/14

ОПИСАНИЕ ИЗОБРЕТЕНИЯ "3 с

"ч

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

H АВТОРСИОМУ СВИДЕТЕЛЬСТВУ (61) 1095243 (21} 3724697/24-24 (22) 13.04 ° 84 (46) 30.05.86. Бюл. У 20 (72) А.М.Пужай (53) 681.327.66 (088.8) (56) Авторское свидетельство СССР

У 1095243, кл. С 11 С 19/14, 1983. (54) ЯЧЕЙКА ПАМЯТИ (57) Изобретение относится к вычислительной технике и является усовершенствованием ячейки памяти по авт.

ÄÄSUÄÄ 1234883 А 2 св. 11 1095243. Цель изобретения состоит в повышении вероятности правильного воспроизведения информации при перерывах питания. Ячейка памяти содержит триггер и накопительные элементы на конденсаторе и трансформаторе. Введение ключевого элемента в состав ячейки памяти позволило стабилизировать процесс переключения накопительного элемента на трансформаторе при включении напряжения питания. 1 ил.

1334883

Изобретение относится к вычислительной технике и может быть исполь1 зовацо при построении регистров и счетчиков, сохраняющих информацию при перерывах питания, и является дополнительным к основному авт. св.

9 1095243.

Цель изобретения — повьппение надежности ячейки памяти, а именно повышение вероятности .правильного Вос произведения информации при перерывах питания.

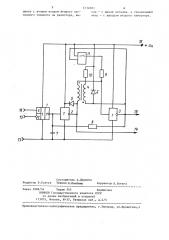

На чертеже приведена электрическая схема ячейки памяти.

Ячейка памяти содержит элемент запрета 1, инверторы 2 и 3, накопительный элемент на трансформаторе 4, два шунтирующих элемента на диодах

5 и 6, накопительный элемент íà конденсаторе 7, три пассивных элемента. на резистрах 8, 9, 10, ключевой элемент 11, управляющий вход 12, вход запрета 13, первый и второй выходы

14 и 15, шину 16 питания и шину 17 нулевого потенциала. Элемент запрета

1 является элементом с тремя состояниями, Устройство работает в двух режимах: в режиме записи информа.ции и в режиме хранения записанной информации.

В режиме записи логическая " 1" с входа 12 элемента запрета 1 при разрешающем сигнале на входе 13 поступает на вход первого инвертора 2. С выхода первого инвертора 2 логический

"0" поступает на вход второго инвертора 3, который инвертирует его в логическую "1", поступающую через резистор 8 на вход первого инвертора

2, замыкая тем самым обратную связь триггера, выполненного на инверторах

2 и 3. При этом ключевой элемент 11 открыт по управляющему входу уровнем логической "1" и через первичную обмотку трансформатора 4 протекает ток логического "0", величина которого определяется номиналом второго резистора 9 и выбирается из условия насыщения сердечника трансформатора

4. Происходит запись логического "0" в ячейку памяти.

Запись логической " 1" в ячейку памяти производится аналогично. При этом ключевой элемент i1 закрыт по управляющему входу уровнем логическо

ro "0", а в сердечнике трансформато5

ЗО

50 ра 4 происходит запись и хранение логической

После записи информации в ячейку элемент запрета 1 блокируется ло входу 13, переходя в третье состояние, и ячейка автоматически переходит в режим хранения информации, которая снимается с выходов 14 и 15.

При перерывах питания, после подачи его, восстановление записанной в ячейке информации происходит следую.Цим образом.

В начальный момент времени после подачи питания триггер, выполненный на инверторах 2 и 3 устанавливается благодаря накопительному элементу на конденсаторе 7, который разряжен в исходное 1единичное" состояние, при котором на выходе первого инвертора

2 устанавливается логическая "1", а на выходе второго инвертора 3 — логический "0". При этом ключевой элемент 11 закрыт по управляющему входу уровнем логического "0". После этого по вторичной обмотке трансформатора

4 протекает ток„ который при хранении в сердечнике логического "0" наводит напряжение в первичной обмотке трансформатора 4. Так как ключевой элемент 11 закрыт, то исключается шунтирующее действие резистора 9 на первичную обмотку трансформатора и амплитуда наведенного напряжения в ней максимальна, Наведенное напряжение переключает инвертор 3 в состояние логической " 1", при этом открывается ключевой элемент 11, а триггер, выполненный на инверторах 2 и 3, устанавливается в "нулевое" состояние, что и соответствует записанной в сердечнике информации до выключения питания.

При хранении в ячейке памяти логической "1" после включения пита11 ния и установки триггера в единичное" состояние напряжение в первичной обмотк,е трансформатора 4 не наводится 1л триггер остается в крайнем состоянии. Ключевой элемент 11 при этом закрыт. формула изобретения

Ячейка памяти по авт. св.

Р 1095243, о г л и ч а ю щ а я с я тем, что, с целью повышения надежности ячейки памяти, в нее введен ключевой элемент,, вход которого сое1234883 ход — с шиной питания, а управляющий вход — с выходом второго инвертора. динен с вторым входом второго пассивного элемента на резисторе, вы—

Сос т авит ель А. Дерюгин

Редактор В.Ковтун Техред П.Олейник Корректор В.Бутяга

Заказ 2988/54 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, r,Óæãîðîä, ул.Проектная,4