Устройство для контроля блоков памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при контроле блоков памяти, для ускорения определения границ области устойчивой работы запоминающих устройств. Цель изобретения - повышение быстродействия устройства. Устройство содержит блок управления, блок сравнения, первый блок местного управления, генератор ступенчатых напряжений , блок печати результатов контроля. Повьшение быстродействия устройства достигается введением вто рого блока местного управления, служащего для управления работой генератора ступенчатых напряжений. 1 зп. ф-лы, 6 ил. (Л tc 00 00 00 4;

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„1234884 А1 (ю 4 С 11 С 29 00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, „„у

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3701489/24-24 (22) 30. 12. 83 (46) 30. 05.86. Бюл. ¹- 20 (71) Московский ордена Ленина и ордена Октябрьской Революции знергетический институт (72) Ю.В.Сычев и А.П.Шарапов (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 242969, кл. С 11 С 29/00, 1969..

Авторское свидетельство СССР

¹ 356696, кл. С 11 С 29/00, 1972. (54) УСТРОЙСТВО ДЛЯ. КОНТРОЛЯ БЛОКОВ

ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано при контроле блоков памяти, для ускорения определения границ области устойчивой работы запоминающих устройств. Цель изобретения — повышение быстродействия устройства. Устройство содержит блок управления, блок сравнения, первый блок местного управления, генератор ступенчатых напряжений, блок печати результатов контроля. Повьппение быстродействия устройства достигается введением второго блока местного управления, служащего для управления работой генератора ступенчатых напряжений. 1 зп. ф-лы, б ил.

1234884

Изобретение относится к вычислительной технике и может быть использовано при контроле блоков памяти, для ускорения определения границ области устойчивой работы (ОУР) запоминающих устройств.

Цель изобретения — повьоиение быстродействия устройства.

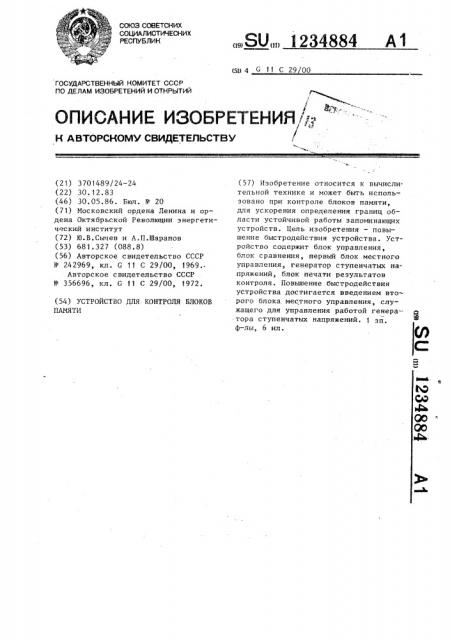

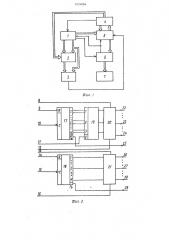

На фиг. 1 представлена структурная схема устройства для контроля блоков памяти; на фиг. 2 — функциональная схема генератора ступенчатых напряжений; на фиг. 3 — функциональная схема второго блока местного управления; на фиг. 4 — функциональная схема блока управления; на фиг. 5 функциональная схема первого блока местного управления; на фиг. 6 — результаты матричных испытаний (фиг.б,о) и результаты испытаний при использовании предлагаемого устройства (фиг. 6,6). На фиг. 6 приняты следующие обозначения: Х,lj — параметры, в которых строится ОУР; в,х соответственно максимальные и минимальные н „„„,, („„„„значения параметров х и

Устройство для контроля блоков памяти содержит (фиг.1) блок 1 управления и подключается к контролируемому блоку 2 памяти. Устройство также содержит блок 3 сравнения, генератор 4 ступенчатых напряжений, первый 5 и второй 6 блоки местного управления, служащие соответственно для управления блоком 7 печати результатов контроля и генератором 4.

Генератор 4 ступенчатых напряжений (фиг.2) имеет входы 8-16, содержит первый 17 и второй 18 счетчики, мультиплексор 19, первый 20 и второй 21 цифроаналоговые преобразователи и имеет выходы 22-29.

Второй блок 6 местного управления (фиг.3) имеет входы 30-32 и содержит элемент И-HE 33, элемент ИЛИ 34,элементы И 35-37, триггер 38, элемент

ИЛИ-НЕ 39, триггер 40, формирователь

41 одиночного импульса, элемент И 42, элемент ИЛИ 43. Блок 6 имеет выходы

44 и 45.

Блок,1 управления (фиг.4) имеет вход 46 и содержит генератор 47 тактовых импульсов, триггер 48, элемент

ИЛИ-HF. 49, элемент ИЛИ 50, элементы

И 51 и 52, счетчики 53 и 54, триггеры 55 и 56, элемент И 57, блок 58 сравнения, элементы И-НЕ 59-61,триг5

WO

L5

7„$

AD)5

55 геры 62 и 63, элемент И-НГ 64, формирователь 65 одиночного импульса.

Блок i имеет выходы 66-69, Первый блок 5 местного управления содержит (фиг.5) триггер 70, элементы И-НЕ 71 и 72, триггер 73, элемент ИЛИ 74, элементы И 75 и 7б,элемент 77 задержки, элементы ИЛИ-НЕ 78 и 79, формирователь 80 одиночного импульса, стробируемые дешифраторы

81 и 82, элемент "àäåðæêè 83, согласующие усилители 84 и 85, элемент

И-НЕ 86. Блок 5 имеет выходы 87-90.

Введем некоторые допущения, без которых использование предложенного устройства может привести к неправильному нахождению границ ОУГ: ОУР является единственной H. выпуклой функциеи.

Устройство для контроля блоков памяти работает следуюпHM образом.

Перед началом работы устройства с помощью опорных напряжений, подаваемых на входы 8 и 13, и напряжений смещений, подаваемых на. входы 12 и

16 (фиг.2) цифроаналоговых преобразователей 20 и 21, устанавливаются нижняя и верхняя граница напряжений питания блока 2 памяти. С помощью счетчиков 17 и 18 устанавливается необходимое количество квантов в матрице йспытаний.

По сигналу "Сброс" отрицательной полярности все триггеры, счетчики устройс.тва устанавливаются в исходное состояние и устройство готово к работе. По импульсу отрицательной полярности триггер 48 устанавливается в единичное состояние, разрешая работу устройства. Начинается процесс нахождения границ ОУР. Для выставленного значения питающих напряжений оценивается работоспособность блока 2 памяти с помощью функционального теста "Бегающие 0 и (фиг.4). Блок 3 (фиг. 1) сравнивает информацию, считываемую из блока 2 памяти, с эталонной, поступающей из блока 1 управления. В случае несравнения считанной и записанной информации блок 3 сравнения вырабатывает сигнал "Сбой"„ поступающий в блок б на вход 32. По этому сигналу триггер

38 устанавливается в единичное состояние,. срабатывает формирователь

41 и прекращается проверка блока 2 памяти при данных сочетаниях питающих напряжений. По сигналу, выраба84 з 12348 тываемому на выходе 44 формирователя 4 1, блок 5 вырабатывает необходимую временную диаграмму для печати символа, соответствующего области неработоспособности блока 2 памяти.

По импульсу "Конец печат э на выходе элемента И-НЕ 86 осуществляется установка счетчиков, триггеров блока 1 управления в исходное состояние и функциональный тест запускает- 10 ся вновь. Если в процессе прохождения функционального теста не было зафиксировано сбоев, т.е. триггер 38 не переключился в единичное состояние, то по сигналу "Конец теста" на выхо- 15 де формирователя 65 триггер 40 устанавливается в единичное состояние, фиксируя то, что первая граница ОУР найдена. По сигналу отрицательной полярности счетчика 17 устанавлива- 20 ется в.исходное состояние, а на вы— ход мультиплексора 19 коммутируются инверсные выходы счетчика 17. Триггер

40 устанавливается в исходное состояние (нулевое состояние), когда будет 25 найдена вторая граница ОУР. В этот момент времени вырабатывается импульс, который запоминается на триггерах 70 и 72 блока 3. Зто необходимо для печати символа в данной точке Зр матрицы испытаний и перехода блока. 7 к печати на следующей строке. В качестве блока 7 может использоваться печатающая машинка типа "Консул".

Блок 5 в этом случае вырабатывает

35 временную диаграмму для печати символа и возврата каретки с переходом на следующую строку.

После того, как будут найдены все точки границы ОУР блока 2 памя- 40 ти, устройство заканчивает свою работу.

Таким образом, при ОУР, изображенной на фиг. 6,а, печать осуществляется способом, показанным на 4 фиг. 6, 6. Восстановление же истинной

ОУР (фиг.б,а) по фиг.6,8, полученной по этому способу, требует небольших затрат неквалифицированного труда.

Формула изобретения

1. Устройство для контроля блоков памяти, содержащее генератор ступенчатых напряжений, блок сравнения, блок управления, первый блок мест— ного управления и блок печати результатов .контроля, входы которого подключены к выходам группы первого бло-ка местного управления, первый выход генератора ступенчатых напряжений соединен с первым входом блока уп— равления, выходы первой группы которого являются адресным выходом устройства, выходы второй группы — информационным выходом устройства и соединены с одними.из входов блока сравнения, другие входы которого являются информационным входом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия устройства, в него введен второй блок местного управления, выходы которого подключены соответственно к входам генератора ступенчатых напряжений и входам группы первого блока местного управления, входы второго блока местного управления соединены соответственно с выходами первой группы генератора ступенчатых напряжений, выходом блока сравнения, выходом первого блока местного управления и выходами третьей группы блока управления, второй вход и выход которого подключены соответственно к выходу и входу первого блока местного управления, выходы второй группы генератора ступенчатыхнапряжений являются выходом питания устройства.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что генератор ступенчатых напряжений содержит счетчики, коммутатор и цифроаналоговые преобразователи, причем прямые и инверсные информационные выходы первого счетчика подключены к информационным входам коммутатора, выходы которого соединены с одним из входов первого цифроаналогового преобразователя, прямые информационные выходы второго счетчика подключены к одним из входов второго цифроаналоговогопреобразователя,входы счетчиков, управляющий вход коммутатора идругие входыцифроаналоговых преобразователей являются входами генератора ступенчатых напряжений, выходами которого являются выходы цифроаналоговых преобразователей и выходы переполнения счетчиков

l234884

1 2 Зч c>8 рие, д

put. Ф

"нип

Х х,а„ клока а, алемана катпицог иепытакий -аптааки, бпок понята пабатаспааабек 3 -етопбй6 бпак памяти неяаботопоообеп — ап — ад. клип

Составитель В.Рудаков

Редактор В.Ковтун Техред Л.Олейник

<орректор В. Бутяга

Заказ 2988/54 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно- полиграфическое предприятие, г.ужгород, ул.Проектная,4