Делитель частоты

Иллюстрации

Показать всеРеферат

Изобретение относится к радиотехнике и м.б. использовано в синтезаторах частоты. Цель изобретения - уменьшение уровня паразитных составляющих в спектре выходного сигнала. Устройство содержит четыре транзистора (Т) 1-4 одной структуры , два конденсатора 5 и 6 обратной связи, параллельный LC-контур (ПК) 7 и формирователь синхронизирующих сигналов (ФСС) 8. Входной сигнал через ФСС 8 воздействует на эмиттеры Т 1-4, изменяя противофазно токи в Т 1 и 2 относительно токов в Т 3 и 4. Противофазно будут изменяться напряжения на коллекторах Т 1 и 2 и Т 3 и 4. На выходе каждого из Т 1-4 образуется спектр частот, воздействующих на ПК 7. Т.к. схема устр-ва является двойной балансной, то в ней возбуждаются и поддерживаются колебания поделенной в два раза входной частоты, а в спектре выходного сигнала отсутствуют паразитные составляющие , влияющие на флуктуацию фазы поделенной частоты. Цель достигается введением Т 3 и 4 и ПК 7. 1 ил. 1C (Л i Выход го СА:) 4:: ( 4 Вход Т

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

Р.

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, К А BTOPCHOMY СВИДЕТЕЛЬСТВУ иод

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3645059/24-09 (22) 26.09.83 (46) 30.05.86. Бюл. № 20 (72) Г. E. Мовкаленко и И. П. Демченко (53) 621.374.42 (088.8) (56) Авторское свидетельство СССР № 828367, кл. Н 03 В 19/12, 1979.

Беленький Я. E. Многофазные релаксационные схемы на транзисторах. М.: Связь, 1972, с. 87 — 89. (54) ДЕЛИТЕЛЬ ЧАСТОТЫ (57) Изобретение относится к радиотехнике и м.б. использовано в синтезаторах частоты. Цель изобретения — уменьшение уровня паразитных составляющих в спектре выходного сигнала. Устройство содержит четыре транзистора (Т) 1 — 4 одной структуÄÄSUÄÄ 1234947 А1 ры, два конденсатора 5 и 6 обратной связи, параллельный LC-контур (ПК) 7 и формирователь синхронизирующих сигналов (ФСС) 8. Входной сигнал через ФСС 8 воздействует на эмиттеры Т 1 — 4, изменяя противофазно токи в Т 1 и 2 относительно токов в Т 3 и 4. Противофазно будут изменяться напряжения на коллекторах Т 1 и 2 и Т 3 и 4. На выходе каждого из Т 1 — 4 образуется спектр частот, воздействующих на

ПК 7. Т.к. схема устр-ва является двойной балансной, то в ней возбуждаются и поддерживаются колебания поделенной в два раза входной частоты, а в спектре выходного сигнала отсутствуют паразитные составляющие, влияющие на флуктуацию фазы поделенной частоты. Цель достигается введением

ТЗи4и ПК7.1 ил.

1234947

Формула изобретения

35 рсо +- с("п

Состав)лель Н. Матвиенко

Тсхред И. Верес Корректор Е. Рошко

Тираж 8!6 !!одписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий ! 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор Л.,г!ежнина

Заказ 2705!57

Изобретение относится к радиотехнике и может быть использовано, например, в синтезаторах частоты.

Цель изобретения — уменьшение уровня паразитных составляющих в спектре выходного сигнала.

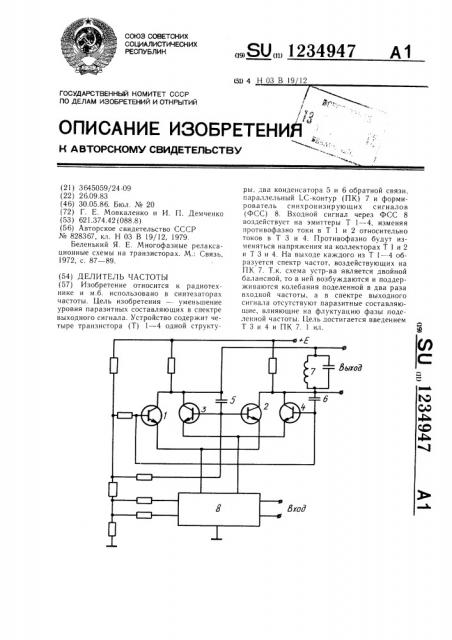

На чертеже представлена принципиальная электрическая схема делителя частоты.

Делитель частоты содержит первый 1, второй 2, третий 3 и четвертый 4 транзисторы одной структуры, первый 5 и второй 6 10 конденсаторы, параллельный 1 С-контур 7 и формирователь 8 синхронизирующих сигналов.

Делитель частоты работает следующим образом.

Входной сигнал через формирователь 8 синхронизирую!цих сигналов, в качестве которого может быть использован, например, дифференциальный усилитель, воздействует на эмиттеры транзисторов 1 — 4, изменяя противофазно токи в транзисторах 1 и 2 относительно токов в транзисторах 3 и 4, при этом противофазно изменяются напряжения на коллекторах транзисторов 1, 2 и 3, 4.

При появлении коллекторного тока возникшие в начальный момент небольшие колебания в параллельном 1 С-контуре 7, настроенном на поделенную входную частоту, через конденсаторы 5 и 6 обратной связи передаются на базы соответствующих транзисторов 2, 3 и 1, 4. На промежуток база:- миттер каждого транзистора действует сигнал входной частоты и поделенной. В результате на выходе каждого из транзисторов 1 — 4 образуется спектр частот, но поскольку схема делителя частоты является двойной балансной то подавляются все частоты, кроме частот вида дерид.=!, 3, 5, ...,; и -- коэффициент деления делителя частоты; со -- входная частота.

При квадратичной апроксимации харак- 45 теристик транзисторов р и g равны единице. Таким образом, спектр частот, воздействующих на параллельный 1 С-контур 7, Содержит суммарную и разностную частоты.

Полезная компонента образуется за счет разностной! частоты оз/и = оз — оз/п, т.е. при делении на целое число получаем и равным 2. Эта частота (со/2) усиливается параллельным 1 С-контуром 7 и через конденсаторы 5 и 6 обратной связи попадает на базы соответствующих транзисторов 2, 3 и 1, 4, усиливается в них, вновь воздействует на параллельный LC-контур 7, усиливаясь им, и т.д.

Таким образом, в делителе частоты возбуждаются и поддерживаются колебания частоты со/2. В спектре делителя частоты содержится полезная составляющая и подавленная фильтром единственная паразитная составляю!цая — суммарная компонента (ш+со/2), которая не оказывает влияния на фазу поделенной частоты.

В предлагаемом делителе частоты отсутствуют паразитные составляющие, влияющие на флуктуацию фазы поделенной частоты.

Делитель частоты, содержащий первый и второй транзисторы одной структуры, при этом коллектор первого транзистора через первый конденсатор подключен к базе второго транзистора, коллектор второго транзистора через второй конденсатор подключен к базе первого транзистора, а эмиттеры первого и второго транзисторов объединены и подключены к выходу формирователя синхронизирующих сигналов, вход которого является входом делителя частоты, отличаюи1ийся тем, что, с целью уменьшения уровня паразитных составляющих в спектре выходного сигнала, между коллекторами первого и второго транзисторов включен параллельный LC-контур, а также введены третий и четвертый транзисторы одной структуры, при этом коллекторы третьего и четвертого транзисторов подключены к коллекторам соответственно первого и второго транзисторов, а базы третьего и четвертого транзисторов подключены к базам соответственно второго и первого транзисторов, эмиттеры третьего и четвертого транзисторов объединены и подключ Hbl к противофазному выходу формирователя синхронизирующих сигналов.