Устройство дискретной задержки

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в области приборостроения, в частности в измерительной те.хнике. Цель изобретения - повышение бь стродействня устройства. Устройство содержит управляющий триггер I, элемент И 2, управляющий счетчик 3, генератор 5 переписывающего импульса и элемепт 7 задержкп. Введение в устройство п-1 счетчиков 6, формирователя 4 многофазного паиряжепия и коммутатора 8 каналов позволило меньи пть дискретность задержки . В огпюаиии приведены временные диаграммы работы устройства. 2 ил. ю со со ел 05

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК дц4 НОЗ К5 153

ОПИСАНИЕ ИЗОБРЕТЕНИЯ/"

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3796126/24-21 (22) 13.07.84 (46) 30.05.86. Бюл. № 20 (72) Е. Д. Петин и Л. А. Чмихун (53) 621.374 (088.8) (56) Авторское свидетельство СССP № 792560, кл. Н ОЗ К 3/017, 1981.

Важенина 3. П., Волкова Н. Н., Чадович И. И. Методы и схемы временной задержки импульсных сигналов. M.: Советское радио, !971, с. 184 — 186, рис. 326. (54) УСТРОЙСТВО ДИСКРЕТНОЙ ЗАДЕРЖКИ

„„SU„„1234956 А1 (571 Изобретение может быть использовано в onласти приборостроения, в частности в измерительной технике. Цель изобретения— повышение быстродействия устройства. Устройство содержит управляющий триггер 1, >лемент И 2, управляющий счетчик 3, генератор 5 переписывающего импульса и элемент 7 задержки. Введение в устройство и-1 счетчиков 6, формирователя 4 многофазпого напряжения и коммутатора 8 кана loB позволило уменьшить дискретность задержки. В описании приведены временные диаграммы работы устройства. 2 ил.

1234956

1О

Формула изобретения

Изобретение относится к приборостроению и может быть использовано, в частности, в измерительной технике.

Целью изобретения является повышение быстродействия за счет уменьшения дискретности задержки.

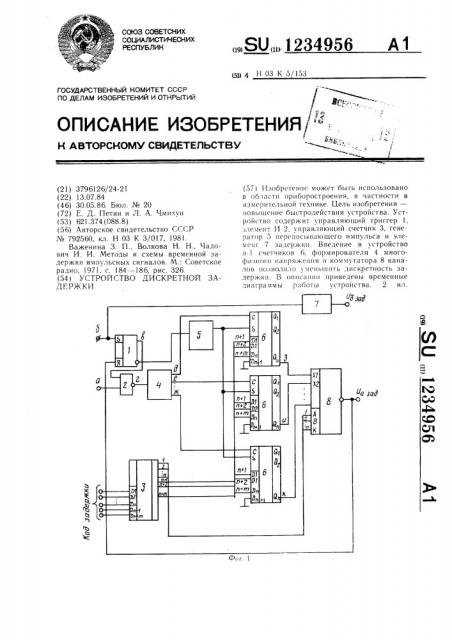

На фиг.1 приведена схема устройства дискретной задержки; на фиг.2 — временные диаграммы работы устройства.

Устройство дискретной задержки содержит управляющий триггер 1, элемент И 2, управляющий счетчик 3, формирователь 4 многофазного напряжения, генератор 5 переписывающего импульса, счетчика 6, элемент

7 задержки и коммутатор 8 каналов.

Прямой выход управляющего триггера 1 соединен с входом элемента И 2, выход которого соединен с входом формирователя 4 многофазного напряжения. Инверсный выход управляющего триггера 1 соединен с входом генератора 5 переписывающего импульса. Информационные входы счетчиков 6 соединены с выходами управляющего счетчика 3 импульсов, а счетные входы — с выходами формирователя 4 многофазного напряжения. К другому входу управляющего триггера 1 подсоединен вход элемента 7 задержки, выход которого соединен с дополнительным выходом устройства. Выходы переполнения счетчиков 6 соединены с информационными входами коммутатора 8 каналов, управляющие входы которого соединены с младшими разрядами управляющего счетчика 3, старшие разряды которого соединены с информационными входами п-1 счетчиков 6. Выход коммутатора 8 каналов соединен с R-входом управляк>щего триггера 1. Выход генератора 5 переписывающего импульса соединен с управляющими входами и-1 счетчиков.

Устройство дискретной задержки работает следующим образом.

Код задержки записывается в управляющий счетчик 3, старшие разряды которого переписываются в счетчики 6 импульсов. Импульс запуска (фиг.26) опрокидывает управляющий триггер 1, выходной импульс (фиг.2в2 которого отпирает элемент И 2. Счетные импульсы (фиг.2г) начинают поступать на формирователь 4 многофазного напряжения.

С выходов формирователя сдвинутые по фазе напряжения (фиг.2 д,е,ж) подаются на счетные входы счетчиков 6. Одновременно с подачей разрешающего импульса на элемент

И 2 (фиг.2 а) на управляющие входы счетчиков подается разрен аюшее напряжение счета с выхода генератора 5 переписывающего импульса, так как на его вход поступает разрешающий потенциал с управляющего триггера !. Счетчики начинают ра25

3()

50 ботать. Импульсы переполнения (фиг.2 з,и,к) счетчиков 6 поступают на информационные входы коммутатора 8 каналов, который управляется младшими разрядами управляющего счетчика. С выхода коммутатора 8 каналов один из импульсов переполнения поступает на вход управляющего триггера 1 и устанавливает его в исходное состояние.

Запрещающий потенциал с выхода управляющего триггера 1 поступает на вход элемента И 2 и запрещает прохождение счетных импульсов, а инверсный выход управляющего триггера переводит счетчики 6 в режим параллельной записи. Устройство переходит в исходное состояние до прихода очередного импульса запуска.

Таким образом, на выходе коммутатора 8 каналов в течение одного периода следования импульсов запуска образуется прямоугольный импульс (фиг. 2 л), который является заде ржа нным относительно импульса запуска.

Устройство дискретной задержки, содержащее счетчик, информационные входы которого соединены с соответствующими старшими разрядами управляющего счетчика, управляющий триггер, выход которого соединен с входом генератора переписывающего импульса, выход которого соединен с управляющим входом счетчика, элемент И, соединенный одним из входов с выходом управляющего триггера, другой вход которого является входом устройства, S-вход управляющего триггера соединен с шиной запуска, входы управляющего счетчика соединены с соответствующими шинами кода задержки, отличающееся тем, что, с целью повышения быстродействия, в него дополнительно введены и-1. счетчиков, формирователь многофазного напряжения и коммутатор каналов, причем вход формирователя многофазного напряжения соединен с выходом элемента И, а соответствующие выходы — со счетными входами соответствующих счетчиков, выходы переполнения которых соединены с соответствующими информационными входами коммутатора каналов, управляющие входы коммутатора каналов соединены с соответствующими младшими разрядами управляющего счетчика, старшие разряды которого соединены с информационными входами и-1 счетчиков, выход коммутатора каналов соединен с R-входом управляющего триггера, а выход генератора переписывающего импульса соединен дополнительно с управляющими входами и-1 счетчиков, выход коммутатора каналов является выходом устройства.

1234956

Составитель Г. Крапива

Редактор А. Лежнина Техред И. Верес Корректор E. Рошко

Заказ 2705/57 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и от крытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4!5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4