Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и м.б.использовано в многоканальных системах передачи данных. Повьшается быстродействие. Устройство содержит три коммутатора 1, 9 и 13, пять блоков памяти (БП) 2, 6, 7, 10 и 11, блок зшравления 3, генератор тактовых импульсов 4, два сумматора 5 и 16, блок сравнения по модулю два (БСМД) 8, три ключа 12, 14 и 17, накопительный сумматор 15, ЦАП 18 и ФНЧ 19. Работа устройства функционально делится на три этапа. На первом этапе производится определение и запись начальных адресов в БП 7 при ;помощи коммутаторов I и 9, БП 2, 6 и 11, блока управления 3, генератора тактовых импульсов 4, сумматора 5, БСМД 8 и ключей 12 и 14. На втором этапе производится вычисление отсчета выходного сигнала на накопительном сумматоре 13 при помощи генератора тактовых импульсов 4, БП7 и 10, коммутаторов 9 и 13, ключей 12 и 14 и сумматора 16. На третьем этапе проS (Л to со со ;о iNd

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

{5D4H 04 Ь 27 12

OflHCAHHE ИЗОБ КТКНИЯ/"

Н А ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

fl0 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3822967/24-09 (22) 12.12.84 (46) 30.05.86. Бвл. Ф 20 (72) В. В. Светличный (53) 62!.394.61(088.8) (56) Патент Великобритании Ф 1268327, кл. НЗР, 1972.

Авторское свидетельство СССР .

1{ 919147, кл. Н 04 L 27/12, 1980. (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

ЧАСТОТНО-МАНИПУЛИРОВАННОГО СИГНАЛА В ,МНОГОКАНАЛЬНЫХ СИСТЕМАХ СВЯЗИ (57) Изобретение относится к электросвязи и м.б. использовано в многоканальных системах передачи данных.

Повьппается быстродействие. Устройство содержит три коммутатора 1, 9 и 13, пять блоков памяти (БП) 2, 6, 7, 10

„„Я0„„1 234992 А 1 и l! блок управления 3, генератор тактовых импульсов 4, два сумматора

5 и 16, блок сравнения по модулю два (БСМД) 8, три ключа 12, 14 и !7, накопительный сумматор 15, ЦАП 18 и

ФНЧ 19. Работа устройства функционально делится на три этапа. На первом этапе производится определение и запись начальных адресов в БП 7 при помощи коммутаторов 1 и 9, БП 2, 6 и

ll, блока управления 3, генератора тактовых импульсов 4, сумматора 5, БСМД 8 и ключей !2 и 14. На втором этапе производится вычисление отсчета выходного сигнала на накопительном сумматоре 15 при помощи генератора тактовых импульсов 4, БП7 и 10, коммутаторов 9 и 13, ключей 12 и 14 и сумматора 16. На третьем этапе про

1234992 изводится преобразование полученных помощи ЦАП 18 и ФНЧ 19. Цель достицифровых отсчетов выходного частотно- гается введением БП 7, 10 и 11, SC манипулированного сигнала с ограничен 8, коммутаторов 9 и 13, ключей 12 и ным спектром в аналоговый сигнал при 14, сумматора 16. 2 ил, 5

10 !

Изобретение относится к электросвязи и может быть использовано в многоканальных системах передачи данных.

Целью изобретения является повышение быстродействия.

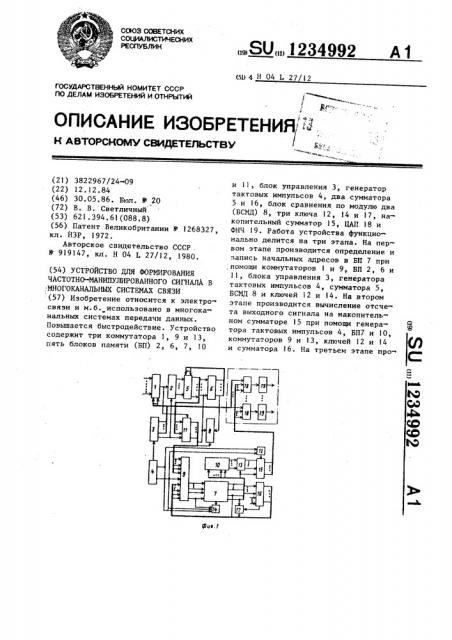

На фиг. 1 изображена структурная электрическая схема предложенного устройства; на фиг. 2 - временные диаграммы.

Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи содержит первый коммутатор 1, первый блок

2 памяти, блок 3 управления, генератор 4 тактовых импульсов, первый сумматор 5, второй и третий блоки 6

1 и 7 памяти, блок 8 сравнения по модулю два, второй коммутатор 9, четвертый и пя1ый блоки 10 и 11 памяти, первый ключ 12, .третий коммутатор 13, второй ключ 14, накопительный сумма«, тор 15, второй сумматор 16, третий ключ 17, цифроаналоговые преобразователи 18, фильтры 19 нижних частот.

Устройство работает следующим образом.

Двоичные сигналы (от N источников информации, не указанных на фиг. 1) поступают на соответствующие информационные входы первого коммутатора

1 Тактовые импульсы с первого выхода генератора 4 тактовых импульсов (фиг. 2 а ), имеющие частоту F, поступают на вход блока 3 управления, имеющего столько адресов, сколько каналов обслуживается устройством.

Поэтому каждый из источников информации опрашивается с частотой F!.

F /N 1/Т (фиг. 2 6 ), где N— число каналов связи, Т - интервал между отсчетами выходного частотноманипулированного (ЧИ) сигнала с ограниченным спектром.

Поскольку процессы в устройстве для формирования ЧМ сигнала в много20

45 канальных системах связи повторяются через интервал времени ;. = t, — t

"с и н< (фиг. 2 а, Я ), то, следовательно, достаточно рассмотреть работу устройства на интервале = t о

Для удобства описания работы устройства формирования ЧМ сигнала рассмотрим интервал c = t — t в увеличенном масштабе (фиг. 2 ) .

Работу устройства можно функционально разделить на определение и запись начальных адресов в блок 7 памяти; вычисление отсчета выходного сигнала; преобразование цифровых отсчетов iN сигнала в аналоговый сигнал.

Определение и запись начальных адресов производится следующим образом.

В течение времени = 1/Г г. выборка двоичного сигнала от ot!-! ределенного источника информации под воздействием сигналов с первого выхода блока 3 управления, поступающих на адресные входы первого коммутатора l (фиг. 2 3,,6, з ), поступает на первый вход блока 2 памяти, на второй вход которого синхронно с выборкой поступает информация о скорости пере" дачи информации в данном направлении с второго выхода блока 3 управления.

С выходов блока 2 памяти сформирован. ное под воздействием входных сигнапо!! rn-разрядное число поступает на вход первого слагаемого сумматора 5.

Одновременно с выхода блока 6 памяти на вход второго слагаемого сумматора

5 поступает m-разрядное число, соответствующее этому же направлению. В первом сумматоре 5 происходит суммирование т-разрядных чисел первого и второго слагаемых,.полученная ш-разрядная сумма поступает на входы блока 6 памяти. Сигналы старших m b!x разрядов сумматора 5 и блока памяти

6 поступают на соответствующие входы

1234992

55 блока 8 сравнения по модулю два. В случае различия полярностей сигналов от выходов сумматора 5 и блока 6 памяти (наличие фронта импульсного ЧМ сигнала) на выходе блока 8 сравнения по модулю два формируется сигнал лонической единицы. Одновременно с этим блок 11 памяти под управлением сигналов с выхода блока 3 управления и первого коммутатора 1 производит преобразование фазы ЧМ сигнала с выхода сумматора 5 в соответствующий код.

На втором выходе генератора 4 тактовых импульсов формируются тактовые импульсы с частотой Р, (фиг. 2ж ), поступающие на соответствующие входы ключей 12 и 14. На третьем выходе генератора 4 тактовых импульсов через (М + 1) такт частоты Р формируется импульс (фиг. 2 е ) длительностью О

1/Г», совпадающий по времени с началом импульсов с выхода блока 3 управления в моменты времени

, ...,,»... Под управлением этого импульса второй коммутатор 9 подключает m выходов блока 1! памяти, старший ш-ый разряд сумматора 5 и выход блока 8 сравнения по модулю два к соответствующим входам блока 7 памяти.

При наличии фронта импульсного ЧМ сигнала, о чем свидетельствует сигнал логической единицы на (ш+ 2)-и входе блока 7 памяти, ключ 14 пропускает на сдвиговый вход блока 7 памяти тактовый импульс (импульс 1, фиг. 2 ж ), под воздействием которого происходит запись (ш+ 2)-разрядного слова в блок

7 памяти. При этом в m ячеек записывается начальный адрес (относящийся к данному фронту) отсчета. R (m+1)-ю ячейку записывается вид перехода импульсного ЧМ сигнала (положительный или отрицательный фронты), причем логическая единица соответствует отри- цательному фронту, логический нольположительному. В (m+ 2)-ю ячейку записывается логическая единица.

На этом запись начальных адресов в блок 7 заканчивается.

Вычисление выходного отсчета происходит на интервале (t» + » )— Второй коммутатор 9 под управлением сигнала нулевой полярности (фиг. 2 е ), поступающего íà его второй вход с третьего выхода генератора 4 тактовых импульсов через третью группу входов, подключает выходы блока 7 памяти на его информацион5

35 ные входы через второй сумматор 16.

Этим обеспечивается круговой сдвиг информации в блоке 7 памяти пад тактами частоты F, (импульсы 2...(М+1), фиг. 2ж ), поступающими с третьего выхода генератора 4 тактовых импульсов на сдвиговый вход блока 7 памяти через третий вход ключа 14.

Под каждым тактом частоты F» из блока 7 памяти выводится (m+2)-разрядное число, первые m разрядов которого подключены к адресным входам блока

10 памяти. По этому адресу из второго блока 10 памяти выводится К-разрядное число, характеризующее .отсчет реакции цифрового фильтра в момент времени пТ на соответствующий фронт импульсного ЧМ сигнала. Эти K-разрядные числа поступают на первую группу входов третьего коммутатора 13, который управляется поступающим на его второй вход сигналом с (m+1)-ro разряда блока 7 памяти. Если сигнал представ" .ляет собой логический ноль (т.е. адрес соответствует положительному фронту), то число с выхода блока 10 памяти поступает на первую группу входов накопительного сумматора 15 без изменения. Если сигнал - логическая единица (т.е. адрес относится к отрицательному франту), то число с выхода блока 10 памяти инвертируется и с помощью логической единицы (m+1)-ro разряда блока 7 памяти, поступающей на третий вход накопи тельного сумматора 15, преобразуется в дополнительный код. Этим обеспечивается вычитание данного отсчета.

Сложение чисел в накопительном сумматоре 15 происходит нод воздействием М тактов частоты F поступающих на ега вход с третьего выхода генератора 4 тактовых импульсов (фиг. 2 Ж ) через второй вход ключа ,12. Прохождение первого импульса (фиг. 2ж ) через ключ 12 запрещается пад воздействием импульса (фиг. 2e ) с второго выхода генератора 4 тактовых импульсов (фиг. 2 ) .

Одновременно m-разрядный адрес с выхода блока 7. памяти поступает на первую группу входов второго сумматора 16, где суммируется с числом К (где К - число тактов частоты Р на интервале Т), поступающим на вторую группу его входов. На выходе второгс

В сумматора 16 образуется m-разрядное

123499? число, соответствующее адресу последу. ющего для данного фронта отсчета.

В случае превышения адресом числа

2 (где 2 " максимальный адрес, по

Щ Ph которому хранится отсчет в блоке 10 памяти), что свидетельствует об окончании реакции на соответствующий фронт, на втором выходе второго сумматора lб формируется сигнал. По этому сигналу закрывается третий ключ 17 и в (ш+2)-ю ячейку (ш+2)-разрядного слова в блок 7 памяти записывается логический ноль.

При выводе этого слова из блока 7

".памяти по нулевому сигналу его (ш+2)го разряда на выходе блока 10 памяти формируется нулевое число, чем достигается исключение этого (m+ 2)-разрядного слова иэ обработки. 20

Через М тактов частоты Р; (где Ммаксимально возможное число фронтов импульсного ЧМ сигнала) на выходе накопительного сумматора 15 формируется отсчет выходного ЧМ сигнала с ограни- 2 ченным спектром. Полученная и-разрядная сумма поступает на информационные входы цифроаналоговых преобразователей 18.

Под воздействием сигнала с соответствующего адресного выхода блока 3 управления„ поступающего на адресный вход одного иэ цифроаналоговых преобразователей 18, и-разрядная сумма, присутствующая на его входе, преобра35 зуется им в аналоговый сигнал, который поступает затем на вход соответствукицего фильтра 19 нижних частот для ограничения высокочастотных составляющих. Выходы фильтров !9 нижних частот являются выходами устройства.

Вычисление отсчета выходного сигнала для следующего направления на интервале „ tz- t> производится аналогичным образом. формула и з о б р е т е н и я

Устройство для формирования частотно-манипулированного сигнала в многоканальных системах связи, содер" кащее генератор тактовых импульсов, первый выход которого соединен с входом блока управления, адресные выходы которого соединены с адресными входами цифроаналоговых преобразователей и с адресными входами первого коммутатора, выход которого подключен к первому входу первого блока памяти, выходы которого соединены с первыми входами первого сумматора, выходы которого соединены с входами второго блока памяти, выходы которого подключены к вторым входам первого сумма-. тора, накопительный сумматор, выходы которого соединены с информационными входами цифроаналоговых преобразователей, выходы которых подключены к входам соответствующих фильтров нижних частот, при зт;., информационные входы первого комму атара являются информационными входам-« :;-...çýéñòâа, от,личающе еся тем, что, с целью пювьииения быстроцейстиия него введены третий, четвертый и пятый блоки памяти, второй и третий коммутаторы, три ключа, блок сравнения по модулю два и второй сумматор, первые выходы которого соединены с первыми входами второго коммутатора, выходы которого подключены к адресным входам третьего блока памяти, выходы которого соединены с адресными входами второго сумматора и с адрес» ными входами четвертого блока памяти, выходы которого подключены к адресным входам третьего коммутатора, выходы которого соединены с первыми входами накопительного сумматора, второй вход которого соединен с выходом первого ключа, первый вход которого соединен с первым входом второго ключа и с вторым выходом генератора тактовых импульсов, третий выход которого соединен с вторым входом первого ключа, с вторым входом второго ключа и с вторым входом второго коммутатора, третьи входы которого подключены к выходам пятого блока памяти, первый вход которого соединен с управляющим выходом блока уп" равления и с вторым входом первого блока памяти, первый вход которого подключен к второму входу пятого блока памяти, третьи входы которого подключены к выходам первого сумматора, выход старшего разряда которого соединен с первым входом знакового разряда второго коммутатора и с первым входом блока сравнения по модулю два, второй вход которого подключен к выходу старшего разряда второго блока памяти, выход блока сравнения по модулю два соединен с первым входом служебного разряда второго коммутато ра, второй вход знаковог< разряда

1234992 фиг,2

Составитель О. Геллер

Редактор К. Волощук Техред И.Попович Корректор Л. Пилипенко

Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, .Раушская наб., д. 4/5

Заказ 2991/59

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 которого соединен с выходом знакового разряда третьего блока памяти, с входом третьего коммутатора и с вторым входом накопительного сумматора, второй вход служебного разряда второго коммутатора соединен с выходом третьего ключа, первый вход которого подключен к входу служебного разряда четвертого блока памяти и к выходу служебного разряда третьего блока памяти, сдвиговый вход которого соединен с выходом второго ключа, третий вход которого подключен к выходу служебного разряда второго коммутатора, второй выход второго сумматора соединен с вторым входом третьего ключа, причем тактовые входы второго сумматора являются тактовыми входами устройства.