Четырехуровневый однозарядный сумматор

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении интегральных схем обработки цифровой информации при многоуроневом представлении информации. Данный сумматор имеет более широкую область применения благодаря возможности суммирования пяти одноразрядных операндов. Цель изобретения достигается введением в известный сумматор на п-р-п-транзисторах с инжекционным питанием дополнительно двух токовых отражателей и трех пороговых детекторов, выполненных на составлных п-р-п-транзисторах, .а также новых связей. I ил. с S N СО о 4 о: со

ОБОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„;SU„, 1236463 А i (51) 4 G 06 Р 7 50

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ASTOPQHOMV СВИДЕТЕЛЬСТВУ (57) Изобретение относится к вычислительной технике и может быть использовано при построении интегральных схем обработки цифровой информации при многоуроневом представлении информации. Данный сумматор имеет более широкую область применения благодаря возможности суммирования пяти одноразрядных операндов. Цель изобретения достигается введением в известный сумматор на и-р-и-транзисторах с инжекционным питанием дополнительно двух токовых отражателей и трех пороговых детекторов, выполненных на составлных и-р-и-транзисторах, .а также новых связей..1 ил. (21 ) 3743844/24-24 (22) 21.05.84 (46) 07.06.86. Бюл. В 21 (71 ) Ленинградский институт инженеров железнодорожного транспорта им. акад. В.Н. Образцова (72) А.Е. Бобров (53) 681.325.5 (088.8) (56 ) Авторское свидетельство СССР

111 1095174, кл. G 06 F 7/50, 1982.

Proc. of tke 12 International Symposium on Multi Valued Logic.- IEEE, 1982, р.64, fig.9. (54) ЧЕТЫРЕХУРОВНЕВЫЙ ОДНОРАЗРЯДНЫЙ

СУММАТОР

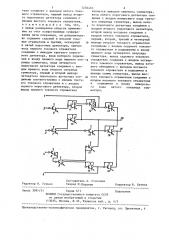

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 7, 236463 1 вые отражатели ll-!8, выход 19 суммы и выход 20 переноса. Пороговые детекторы и токовые отражатели представляют собой составные и-р-и-транзис5 торы, где коллектор первого транзистора соединен с шиной питания, а эмиттер второго транзистора — с шиной нулевого потенциала.

Характеристики

6 7 8 9 II 14 I.O 15 17 18 14 13 !6

4 8 4 i 1 1 1 1 4 7 1 7 3

Д Д Д О О Д Д 0 0 О О 0 О

Номер вентиля в схеме

Вес инжектора

Схема включения

Работа четырехуровневого одноразрядного сумматора описывается с помощью последовательностей возможных значений токов, упорядоченных относительно входной последовательности токов, за которую принята 16-элементная последовательность:

0.1.2.3.4.5.6 ° 7.8,9.10.11.12.13,14.15.

Это входная последовательность однозначно задает значения токов на всех

1024 возможных различных комбинациях пяти взвешенных слагаемых в

4Q прямом коде. Считая, что на вход 1 подается именно входная 16.-элементная последовательность, можно соответствующими последовательностями описать работу сумматора в любой

45 точке схемы. При этом на выходах переноса 20 и суммы 19 сумматора должны получиться последовательности: выход 20 О.О.Q.Î.I.1.1.1.2.2.2.2.3.3.

3.3; выход 19:0.1.2.3.0.1.2. .3.0.1.2.

3.0.1.2.3.

При этом следует учесть, что на выходе 20 переноса последовательность значении токов получается сумЯ мированием последовательностей, сформированных на соответствующих выходах:

1 1

Изобретение относится к вычислительной технике и может быть использовано при построении интегральных схем обработки цифровой информации, например, и уиножителях и функциональных преобразователях.

Целью изобретения является расширение области применения эа счет осуществления суммирования пяти операндов.

На чертеже представлена принципиальная схема четь|рехуровневого одноразрядного сумматора.

Четырехуровневый одноразрядный сумматор содержит входы 1-5 операндов, пороговые детекторы 6-10, токоНа входы 1, 2 и 3 подаются прямые коды операндов, а на входы 4 и 5 инверсные коды.

Веса инжекторов многозначных И Лz вентилей из составных транзисторов и схемы включения вентилей приведены в таблице (Д вЂ” включение И Л-вентиля по схеме порогового детектора;

Π— включение по схеме токового отражателя). выход lli0.0.0.0.1.1.1.1. 1.1.1.1.

1.1.1

+ выход 14:0.0.0.0.0.0.0.0.1.1.1.1.1 ! 1.1 выход 15:0.0.0.0.0.0.0.0.0.0.0.0.1.

1.1.1 выход 20:0.0.0.0.1.1 I.!.2.2.2.2.

3.3.3.3

Аналогично на выходе 19 суммы происходит сложение последовательностей:, выход 16:0.1.2.3.0.1.2.3.0.0.0.0.0.

0.0.0

+ выход 18:0.0.0.0.0.0.0.0.0.1.2.3.

0.1.2.3 выход 19:0.1.2.3.0.1.2.3.0.1.2.3.

О.!.2.3 что соответствует правильной работе четырехуровневого одноразрядного сумма тора.

Формулаизобретения

Четырехуровневый одноразрядный сумматор, содержащий шесть токовых отражателей и два пороговых детектора„ причем первый выход первого токового отражателя соединен с входом второго токового отражателя, второй выход первого токового отражателя соединен с вьгходом. третьего токового отражателя, выход первого порогового детектора подключен к входу четвертого токового отражателя, второй выход первого токового отража12364 его токового отражателя и с входом первого порогового детектора, второй выход первого токового отражателя

Составитель А. Степанов

Техред M.Õoäàíè÷

Корректор В. Бутяга

Редактор Н. Гунько

Заказ 3091/51

Тираж 671

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 теля соединен с выходом пятого токового отражателя, первый выход второго порогового детектора соединен с входом шестого токового отражателя, отличающийся тем, что, с целью расширения области применения за счет осуществления суммирования пяти операндов, он дополнительно содержит седьмой и восьмой токовые отражатели и третий, четвертый 1О и пятый пороговые детекторы, причем вход первого токового отражателя соединен с выходом третьего порогового детектора, вход которого подключен к входу прямого кода первого опе- 15 ранда сумматора, вход четвертого порогового детектора соединен с входом прямого кода второго операнда сумматора, первый и второй выходы четвертого порогового детектора сое- ga динены соответственно с входом треть63 4 является выходом переноса сумматора, вход пятого порогового детектора соединен с входом инверсного кода третьего операнда сумматора, выход пятога порогового детектора соединен с входом второго порогового детектора, второй выход которого соединен с входом пятого токового отражателя, первый, второй, третий и четвертый выходы второго токового отражателя соединены с входом седьмого токового отражателя и подключены к входу прямого кода четвертого операнда сумматора, выход седьмого токового отражателя соединен с входом четвертого токового отражателя, выход которого объединен с выходом восьмого токового отражателя и подключен к выходу суммы сумматора, выход шестого токового отражателя соединен с. входом восьмого токового отражателя и подключен к входу инверсного кода пятого операнда сумматора.