Устройство микропрограммного управления

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении программируемых контроллеров, в частности, реализующих булевские функции. Цель изобретения - упрощение устройства. Цель достигается за счет введения в устройство группы триггеров с соответствующими функциональными связями между ними и известными блоками устройства. Устройство позволяет циклически анализировать логические условия, поступающие на его вход. Значения функций вычисляются в виде кода микрооперации. 3 ил. I табл. Фиг.1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (g1) 4 G 06 F 9/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТНЕНИЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2l) 3796536/24-24 (22) 01.10.84 (46) 07.06,86. Бюл. У 2l (7l) Московский автомобильный завод им. И.А.Лихачева (72) А.И.Андерсон и В.И.Хохлов (53) 68!.32(088.8) (56) Авторское свидетельство СССР

809!84, кл. G 06 F 9/22, 1979.

Memory design handbook. Intel

Corporation, 1977, с. 7-32, рис. 52. (54) УСТРОЙСТВО ИИКРОПРОГРАМШОГО

УПРАВЛЕНИЯ

„„SU„, 1236476 А 1 (57) Изобретение относится к вычислительной технике и может быть использовано при построении программируемых контроллерон, в частности, реализующих булевские функции. Цель изобретения — упрощение устройства.

Цель достигается за счет введения н устройство группы триггеров с соответствующими функциональными связями между ними и известными блока- ми устройства. Устройство позволяет циклически анализировать логические условия, поступающие на его вход.

Значения функций вычисляются в ниде . кода микрооперации. 3 ил. табл.

t 12364

Изобретение относится к вычислительной технике и может быть испольэовано при построении программируемых контроллеров, в частнос.ти, реализующих булевские функции, Целью изобретения является упрощение устройства.

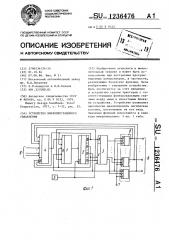

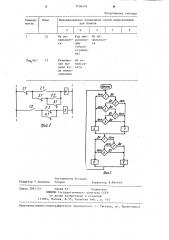

На фиг. 1 изображена функциональная схема устройства, на фиг. 2 переключательная схема в виде лесничной диаграммы; на фиг. 3 — блоксхема алгоритма работы устройства.

Устройство содержит блок 1 памяти, регистр 2 микрокоманд, дешифратор 3, мультиплексор 4, генератор 5 импульсов, группу 6 триггеров, вход

7 начальной установки устройства, вход 8 логических условий устройства, информационный выход 9 устрой— ства, выходы номера 10 модифициру рб емого разряда кода микрооперации, номера 11 анализируемого логического условия, кода 12 микрооперации и признака 13 разрешения выдачи кода микрооперации регистра микрокоманд. д

Устройство (фиг. 1) работает следующим образом.

Значения логических условий поступают через вход 8 устройства и циклически анализируются. Вычисленные в виде кода микрооперации значения функций запоминаются в триггерах 6 и поступают на выход 9 устройства. В каждом такте микрокоманда из блока памяти загружается в регистр 2 микрокоманд. Адрес следующей микрокоманды

35 формируется в соответствии со значением (О или 1) анализируемого аргумента — логического условия или промежуточного результата вычисления (функции), подаваемого через мульти40 плексор 4 на первый адресный вход блока I памяти и содержимого регистðà 2 микрокоманд, поступающего на остальные адресные входы блока 1 памяти. Если анализируемый аргумент входит в вычисляемую булевую функцию с инверсией и равен "1" или вхоцит без инверсии и равен "0", иэ блока

1 памяти выбирается следующая микрокоманда, соответствующая аргументу, входящему в диэъюнкцию к анализируемой части функции. Если такая диэъюнкция отсутствует, выбирается следующая .микрокоманда, инициализирующая через дешифратор 3 сброс в "0" ооответствующего триггера группы 6.

Если анализируется аргумент, входящий в вычисляемую булевую функдию

76 Л с инверсией и равный "0" или входящий беэ инверсии и равный "I", из блока 1 памяти выбирается следующая микрокоманда, соответствующая аргуМенту, входящему в конъюкцию к анализируемой части функции. Если таковая конъюкция отсутствует, выбирается следующая микрокоманда, инициализирующая через дешифратор 3 установку в состояние 1 соответствующего триггера группы 6.

Если выполняется микрокоманда, инициализирующая сброс или установку триггера группы 6, то независимо от состояния первого входа блока I памяти выбирается следующая микрокоманда, соответствующая проверке аргумента для вычисления очередного кода микрооперации.

Выбранная микрокоманда в следующем такте загружается в регистр 2 микрокоманд и указанный выше процесс возобновляется.

Запись в регистр микрокоманд может инициализироваться по положительному фронту импульсов с генератора 5, а запись кода микрооперации в триггеры группы 6 — по отрицательному фронту.

Перед началом работы устройства через вход 7 начальной установки на входы сброса триггеров группы

6 подается импульс, длительность которого превышает максимально возможное время, необходимое для вычисления кода микрооперации.

В таблице представлено назначение полей регистра 2.

Количество А информационных каналов мультиплексора 4, разрядность

В входов блока 1 памяти и длина С микрокоманды (таблица) связаны соотношениями

А:=Х+ У;

С-Rog. A М;

В:=С+ 1, где Х вЂ” разрядность входа 8 устройства;

У вЂ” разрядность выхода 9 устройства;

И вЂ” максимальная входимость аргумента с одним идентификационным номером в ветви микропрограммы.

Проиллюстрируем работу устройства при реализации булевых функций, представленных в виде лесничной диаграммы (фиг. 2). Идентификационный но476

1236 з мер контактов (аргументов) и катушек реле (функций) указан на диаграмме цифрой, стоящей перед точкой.

Этот номер занимает поля 10 и 11 микрокоманды. Пусть в процессе вычислений аргумент анализируется на более 8 раз, тогда разрядность полей

12 и 13 микрокоманды равна трем.

Очередность проверки аргумента с одним идентификационным номером в процессе отработки микропрограммы указаны на диаграмме (фиг. 3) цифрами, стоящими после точки. Наличие единиц в поле 13 микрокоманды может являться признаком разрешения выдачи кода микрооперации. При реализации переключательной схемы (фиг. 2) устройство будет работать по алгоритму (фиг. 3), логические блоки которого выполняют следующие действия. проверить логическое условие на равенство 0"; проверить логическое условие 2 на равенство "0"; проверить логическое условие 3 на равенство "0"; проверить значение.функции 2

4 на равенство "0"; проверить значение функции 5 на равенство "0"; установить значение функции 4 равным

"0" установить значение функции 4 равным "1", установить значение функ-З ции 5 равным "0"; установить значение функции 5 равным "1".

Устройство микропрограммного уп35 равления, содержащее блок памяти, регистр микрокоманд, дешифратор, генератор импульсов и мультиплексор, причем выход блока памяти подключен

40 к информационному входу регистра микПоле

Разрядыость

Функциональное назначение полей микрокоманды для блоков

6 4 1 2

Часть ад- Иикрокореса сле- манда дующей

Идентификационный

Не ис- Идентипользует- фикаци ся онный

Eog А

z номер функции номер микрокоаргумен- манды та

Признак инициализации функции

Формула изобретения рокоманд, синхровход которого подключен к выходу генератора импульсов, выход регистра микрокоманд подключен к адресному входу блока памяти, вход

К-ro логического условия устройства подключен к К-му информационному входу мультиплексора К-1, М, где М количество логических условий устройства, выход мультиплексора подключен к входу младшего разряда адреса блока памяти, о т л и ч а ющ е е с я тем, что, с целью упрощения, в него введена группа триггеров, причем выход К-го триггера группы подключен к И+К-му информационному входу мультиплексора, выход номе-. ра модифицируемого разряда кода микрооперации регистра микрокоманд подключен к информационному входу дешифратора и к первому управляющему входу мультиплексора, выход номера анализируемого логического условия регистра микрокоманд подключен к первому стробирующему входу дешифратора и к второму управляющему входу мультиплексора, выход кода микроопеиации регистра микрокоманд подключен к информационным входам триггеров группы, выход признака разрешения выдачи кода микроопераций регистра микрокоманд подключен к второму стро" бирующему входу дешифратора, третий стробирующий вход которого подключен к выходу генератора импульсов, К вЂ” и выход дешифратора подключен к синхровходу К-го триггера группы, выход которого подключен к К-му информационному выходу устройства, входы установки в 0" триггеров группы подключены к входу начальной установки устройства, 1236476

Продолжение таблицы

Функциональное назначение полей микрокоманды для блоков

Поле

Разрядность

3 6 4 l 2

Не используетКод микрооперации (сброс/ установка) Не использует12 ся ся

Разреше- Не используется ние выдачи кода микрооперации

Составитель M. Силин

Редактор Г.Волкова Техред

Корректор В. Бутяга

Заказ 3091/51

Тираж 67I Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4