Устройство для сопряжения процессора с многоблочной памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к вьгчислительной технике и может быть использовано для увеличения объема оперативной памяти при построении вычислительных систем на базе минии микро- ЭВМ. Целью изобретения является расширение области применения устройства за счет обеспечения работы процессора с памятью, адресное пространство которой существенно превышает возможности , предоставляемые форматом адресного слова процессора. Устройство содержит дешифратор сегмента, дешифратор адреса, регистр номера массива, узлы канальных передатчиков и приемников , коммутатор шин данных и младших разрядов шины адреса. 2 ил. с Q 1C 00 О) iJ У Со

СОЮЗ СОжТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51)4 G 06 F 13/16 (21) 3816868/24-24 (22) 27. 11.84 (46) 07.06.86. Бюл. М 21 (71) Омский политехнический институт (72) С.N.Åãîðîâ, В.И.Потапов, M.Ô.ØàKèðîâ и Б.М.Егоров (53) 68 1.327.6(088.8) (56) Авторское свидетельство СССР

Р 643878, кл. G 06 F 13/06, !978.

Авторское свидетельство СССР

И - 951315, кл. G 06 F 13/06, 1981. (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПРОЦЕССОРА С 16!ОГОБЛОЧНОЙ ПАМЯТЬЮ (57) Изобретение относится к вычислительной технике и может быть исполь—

„„SU,„, 1236493 А 1 зовано для увеличения объема оперативной памяти при построении вычислительных систем на базе мини- и микро3ВМ. Целью изобретения является расширение области применения устройства за счет обеспечения работы процессора с памятью, адресное пространство которой существенно превышает возможности, предоставляемые форматом адресного слова процессора. Устройство содержит дешифратор сегмента, дешифратор адреса, регистр номера массива, узлы канальных передатчиков и приемников, коммутатор шин данных и млад- ших разрядов шины адреса. 2 ил, 1 12

Изобретение относится к вычислительной технике и может бьггь использовано для увеличения объема оперативной памяти при построении вычислительных систем на базе мини- и микро. ЭВИ.

Целью изобретения является расширение области применения устройства за счет обеспечения работы процессора с памятью, адресное пространство которой существенно превышает возможности, предоставляемые форматом адресного слова процессора, а также повышение живучести системы, включающей предлагаемое устройство и многоблочную память.

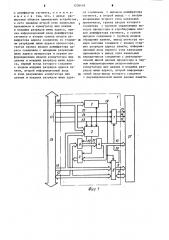

На фиг. 1 представлена блок-схеМа устройства, на фиг. 2 — пример структуры системы, включающей устройство и многоблочную память.

Устройство 1 (фиг. 1) содержит дешифратор 2 сегмента, дешифратор 3 адреса, регистр 4 номера массива, узел 5 канальных передатчиков, узлы 6 и 7 канальных приемников, коммутатор 8 шин данных и младших разрядов шины адреса, шины 9 и 10 выхода младших и старших разрядов адреса памяти устройства, шины 11 и 12 второго и первого информационных входов-выходов устройства, линии 13-15 группы выхо дов сигналов обращения к памяти устройства, шины 16 младн их разрядов адреса, группа управляющих входов 17 устройства, шины 18 старших разрядов адреса, выход 19 дешифратора 2, второй выход 20 коммутатора 8, выходы 21 и 22 дешифратора 3, линия 23 сигнала "Запись" (ЗП), линия 24 сигнала

"Чтение" (ЧТ) и линия 25 сигнала

"Синхронизация адреса" (СИА) группы управляющих входов 17, канал 26 процессора и блок 27 памяти.

Устройство предназначено для организации многоблочной памяти (фиг.2) и содержит устройство 1 сопряжения, блоки 27 памяти, банки 28 памяти„ причем все входы-выходы 29 устройства сопряжения эапараллелены и соединены с каналом 26 процессора, а входы-выходы 30 устройства соединены с входами-выходами блоков 27 памяти.

Устройство работает следующим образом, Вся область памяти, доступная процессору, разбивается на сегменты, каждому сегменту ставится в соответствии блок 27 памяти необходимого

36493

5 !

0 !

45 объема, В каждом конкретном случае сегменты имеют переменный размер °

Блок 27 памяти в свою очередь состоит иэ стандартных модулей памяти, входывыходы которых запараллелены и соединены с входами-выходами 30 устройства 1. Объем каждого блока 27 разбит на равные части — банки 28 памяти, причем объем банка 28 памяти равен объему сегмента памяти. Сегмент памяти, таким образом, является пространством„ через которое процессор имеет доступ к любому банку 28 блока 27.

Процессор соединен с блоками 27 памяти через устройства 1 сопряжения, функцией которых является коммутация канала 26 процессора с блоками 27 в момент обращения процессора к памяти и преобразование адреса, поступающего из процессора.

Таким образом, устройство 1 заменяет старшие разряды адреса памяти, выдаваемого процессором, на содержимое своего, регистра 4 номера массива, значение которого устанавливается процессором программно. 3а счет введения сопряжения между процессором и памятью устройства 1 происходит развязка между адресом, поступающим из процессора, и адресом, поступающим в блок 27. В результате этого появляется воэможность увеличить количество адресных разрядов, а следовательно, и объем блоков памяти. В определенных моментах времени содержимое регистров 4 в каждом устройстве 1 может быть различным, и процессор получает доступ к определенному набору банков 28 памяти, причем по одному банку 28 из каждого блока 27 памяти. В момент включения устройства 1 регистр 4 номера массива устанавливается в нулевое состояние и процессор имеет доступ к нулевым банкам 28 каждого блока 27 памяти. Кроме многоблочной памяти процессор может иметь память с обычной органиэацией, но в таком случае дешифратор 2 сегмента должен настраиваться на адреса, незадействованные обычной памятью.

Перед началом обмена процессора с многоблочной памятью процессору необходимо во всех устройствах установить на регистрах 4 номера мас— сива номера требуемых банков 28. Для этого процессор выставляет адрес регистра 4 на шину адреса. Старшие раз1236493 ряды адреса поступают по шинам 18 на дешифратор 3 адреса. Ипадшие разряды адреса поступают по шинам 16 на дешифратор 3. После этого процессор выдает сигнал СИА на линию 25, па которому дешифратор 3- дешифрирует адрес, установленный на шинах 16 и 18 и после приема управляющих сигналов

ЗП или ЧТ соответственно с линий 23 и 24 выдает единичный сигнал на один 10 из выходов 21 или 22; Если на дешифратор 3 поступил сигнал ЧТ, то с выхода 21 единичный сигнал поступает на разрешающий вход узла 5, разрешая прохождение информации, записанной >S на регистре 4, на шину 12 (данных процессора) . Если на дешифратор 3 поступил от процессора сигнал ЗП, то дешифратор 3 выдает с выхода 22 единичный сигнал на разрешающий вход 20 узла 6. После этого процессор устанавливает необходимый номер банка памяти на шину 12 и эта информация записывается на регистр 4. После установки номеров банков памяти на ре- 25 гистрах 4 всех устройств 1 процессор может обратиться к любой ячейке установленных банков памяти. При этом процессор не ощущает разницы между работой с многоблочной памятью и памятью с обычной организацией, так как задержка на устройстве 1 определяется задержкой на дешифраторе 2, коммутаторе 8 и на узле 7, которая является незначительной и не нарушает канального цикла обращения процессора к памяти.

Обращение процессора к ячейке блока 27 памяти происходит следующим образом. Процессор подает на шины 16 и 18 адреса адрес необходимой ячейки памяти и сигнал СИА. Старшие разряды адреса поступают на информационные входы дешифраторов 2 всех устройств 1.

Сигнал СИА с линии 25 поступает Hà 4S управляющий вход дешифратора 2 всех устройств 1 ° С приходом сигнала СИА дешифраторы 2 дешифрируют старшие раз. ряды адреса. Дешифратор 2, которому соответствует установленный на шинах 18 адрес, выдает управляющий сигнал на разрешающий вход коммутатора 8, коммутируя тем самым шины 12 и 16 на выбранный блок 27 памяти. После срабатывания коммутатора 8 сигнал с выхода 20 поступает на разрешающий вход узла 7, разрешая прохождение управляющих сигналов ЗП, ЧТ, СИА соответственно с линий 23, 24 и 25 на одноименные линии 13, 14 и 15 и далее на управляющие входы блока 27.

В остальных устройствах 1 прохождени управляющих сигналов на соответствующие блоки 27 памяти и коммутация шин 12 (данных) и шин 16 младших разрядов адреса процессора и блоков 27 памяти запрещены. После этого процессор устанавливает необходимую информацию на шину 12 (данных) и подает сигнал ЗП на линию 23. При этом информация, установленная на шине 12 (данных) и шине 16 младших разрядов адреса, поступает на шины 11 и 9.

Сигнал ЗП поступает через узел 7 на линию 23 ЗП и далее на входы управления блока 27 памяти. По сигналу -ЗП информация, установленная на шине 11 (данных), записывается в ячейку блока 27 памяти, адрес которой установлен на шинах 9 и 10.

Таким образом, информация, записанная на регистре 4, указывает на номер банка 28 памяти в блоке 27 памяти, а адрес, поступающий из процессора на младшие разряды шины адреса, указывает на адрес ячейки памяти внутри банка 28 памяти. Аналогично происходит чтение процессором информации из блока 27 памяти, но при этом процессор выдает сигнал ЧТ на линию 24 и через узел 7 на линию 24 ЧТ и вход управления блока 27 памяти. После этого блок 27 памяти устанавливает на шину 11 информацию, которую процессор считывает со своей шины 12 (данных).

Таким образом, устройство обеспечивает расширение области применения за счет существенного увеличения адресного пространства вычислительной системы.

Формула изобретения

Устройство для сопряжения процессора с многоблочной памятью, содержащее регистр номера массива, выход и вход которого соединены соответСтвенно с информационным входом узла канальных передатчиков и выходом первого узла канальных приемников, разрешающие входы которых подключены со-. ответственно к первому и второму выходам дешифратора адреса, первая группа входов которого соединена с группой управляющих выходов процессора, 1236493 и дешифратор сегмента, о т л и ч аю щ е е с я тем, что, с целью расширения области применения устройства, в него введены второй узел канальных приемников и коммутатор шин данных и младших разрядов шины адреса, причем информационный вход дешифратора сегмента и вторая группа входов дешифратора адреса соединены со старши- ig ми разрядами шины адреса процессора, третья группа входов дешифратора адреса соединена с младшими разрядами шины адреса процессора и первым информационным входом коммутатора шин 15 данных и младших разрядов шины адреса, первый выход которого соединен с входом младших разрядов адреса па— мяти, второй информационный вход и вход разрешения коммутатора шин 2р данных и младших разрядов шины адреса соединены с выходом дешифратора сегмента, а второй выход — с входом разрешения второго узла канальных приемников, группа входов которого соединена с группой управляющих выходов процессора и стробирующим входом дешифратора сегмента, а группа выходов соединена с группой входов обращения памяти, выход регистра номера массива соединен с входом старших разрядов адреса памяти, информационный вход первого узла канальных приемников и выход узла канальных передатчиков соединены с двунаправленной шиной данных процессора и первым информационным входом-выходом коммутатора шин данных и младших разрядов шины адреса, второй информационный вход-выход которого соединен с двунаправленной шиной данных памяти.

1236493

° °

Составитель В. Вертлиб

Техред М. Ходанич Корректор М.Демчик

Редактор P.Öèöèêà

Заказ 3092/52

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открьггий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Óæãîðoä, ул.Проектная, 4