Вероятностное устройство для решения конечно-разностных уравнений

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в системах для решения дифференциальных уравнений в частных производных итерационным методом. Цель изобретения - повышение быстродействия устройства за счет снижения затрат времени на повторное формирование массива исходных данных при повторных решениях со сдвигом моделируемой сеточной области. Цель изобретения -достигается за счет введения в устройство регистра, сумматора, блока памяти и триггера с соответствующими функциональными связями меягду ними и известными блоками устройства . Устройство позволяет при одной загрузке памяти осуществить обход сеточной области по заданному закону при занесении данных и съеме решений во всех итерациях и при ползгчении частных решений на сдвинутых моделируемых сеточных областях. 1 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) (51) 4 G 06 F 15/32

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3814021/24-24 (22) 20.11,84 (46) 07.06 ° 86. Бюл. М 21 (71) Рижский ордена Трудового Красного Знамени политехнический институт им. А. Я. Пельше (72) Ф. П, Звиргздиньш Я. Ю. Шлихте, П. И. Новиков и Л. Л. Котович (53) 681.333(088,8) (56) Авторское свидетельство СССР

))2 477418, кл. G 06 F 15/32, 1973.

Авторское свидетельство СССР

И 1168965, кл. С 06 F 15/32, 1984. (54) ВЕРОЯТНОСТНОЕ УСТРОЙСТВО 1ЛЯ

РЕШЕНИЯ КОНЕЧНО РАЗНОСТНЫХ УРАВНЕНИЙ (57) Изобретение относится к области вычислительной техники и может быть использовано в системах для решения дифференциальных уравнений в частных производных итерационным методом.

Цель изобретения - повышение быстродействия устройства за счет снижения затрат времени на повторное формирование массива исходных данных при повторных решениях со сдвигом моделируемой сеточной области. Цель изоб ретения "достигается за счет введения в устройство регистра, сумматора, блока памяти и триггера с соогветствующими функциональными связями между ними и известными блоками устройства. Устройство позволяет при одной загрузке памяти осуществить обход се точной области по заданному закону

C при занесении данных и съеме решений щ во всех итерациях и при получении частных решений на сдвинутых модели руемых сеточных областях. 1 ил. С:

1 1

Изобретение относится к вычислительной технике и может быть испольэонано в системах для решения дифференциальных уравнений в частных производных итерационным методом.

Целью изобретения является повы шение быстродействия устройства за счет снижения затрат времени на повторное формирование массива исходных данных при повторных решениях со сдвигом моделируемой сеточной области.

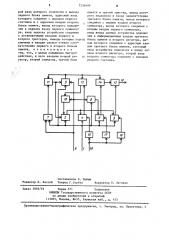

На чертеже изображена схема устройства.

Устройство содержит вход 1 ввода данных, первый счетчик 2, второй счетчик 3, первый 4, второй 5, третий 6 блоки памяти, первый 7 и:второй 8 регистры, тактовый вход 9 устройства, элемент ИЛИ 10, первый ll, второй 12 блоки сравнения, первый 13 второй 14 сумматоры, первый 15, второй 16, третий 17 триггеры, вход 18 запуска устройства, выход 19 устрой ства.

Устройство работает следующим образом.

По сигналу записи, поступающего с тактового входа 9 на вход записи первого регистра 7, код длины массива с нхода 1 ввода данных записывают н первый регистр 7. С входа 18 запуска на входы первого 15, второго

16 и третьего 17 триггеров поступает сигнал, устанавливающий первый триггер 15 и соответственно первый блок

4 памяти в режим записи, а второй

16, третий 17 триггеры и второй 5, третий 6 блоки памяти в режим чтения. По нулевому адресу, поступающему с выхода первого счетчика 2 на адресный вход первого блока памяти

4, в него записывают с входа 1 ввода данных адрес первой зоны. Затем по счетному входу с тактового входа

9 через схему ИПИ !О содержимое первого счетчика 2 увеличивают на единицу и нЯбирают следующую ячейку первого блока 4 памяти. В ныбранную ячейку записывают адрес следующей зоны и процесс повторяется до полной записи адресов всех зон сеточной модели. После записи адресов зон в первый блок 4 памяти первый счетчик

2 устанавливают в нулевое состояние, первый триггер 15 в режим чтения, а второй триггер 16 - н режим записи и осуществляют запись информации во

35 рого блока 5 памяти. Затем второй триггер 16 устанавливают н режим чтения, первый счетчик 2 и второй регистр 8 в нулевое состояние, а третий триггер 17 и соответственно третий блок 6 памяти — в режим записи.

По нулевому адресу, поступающему с выхода второго регистра 8 на адресный вход третьего блока 6 памяти, с входа 1 ввода данных записывают в выбранную ячейку памяти третьего блока 6 памяти код первой константы сдвига адресов начальных точек отсче та координат моделируемой области узловых процессоров. Затем содержи мое второго регистра увеличивают на единицу н с входа 1 ввода данных в очередную выбранную ячейку третьего блока 6 памяти записывают коп следунг» щей к:онстанты. Процесс циклически гонторяется до полной загрузки всех кодов констант н ячейки третьего бло ка 6 памяти. Затем третий триггер 17 устанавливают в режим чтения, а вто рой триггер 8 — в нулевое состояние, после чего устройство настроено и готово к обходу сеточной области.

По входу записи второго счетчика

3 записывают код начального адреса.

С выхода второго счетчика 3 код начального адреса поступает на йторые входы первого 11, второго 12 блоков сравнения и второго сумматора 14.

По коду начального адреса с выхода второго регистра 8 код первой константы из первой ячейки третьего бло ка 6 памяти поступает на первый вход второго сумматора 14, на выходе ко торого формируется код частного адреса первого узлового процессора: первой сеточной области, поступающий на второй вход первого сумматора !3.

С выхода первого счетчика 2 код нулевого адреса поступает на адресные входи первого 4 и второго 5 блоков памяти. По этому адресу первый блок

236499 второй блок 5 памяти. По нулевому адресу, поступающему с выхода первого счетчика 2,, на адресный вход второго блока памяти 5 с входа 1 ввода данных .в выбранную ячейку второго блока памяти 5 записывают код шага обхода первой зоны. Затем содержимое первого счетчика 2 увеличивают на единицу и в следующую ячейку второго блока 5 памяти записывают код шага следующей зоны. Процесс циклически повторяется до полной загрузки вто в котдрой хранится код константы, определяющей величину сдвига начала координат следующего частного решения. С выхода второго регистра 8 код адреса следующей ячейки поступает на адресный вход третьего блока 6 памяти и по этому адресу из выбранной ячейки код следующей константы сдвига начала координат моделируемой сеточной области, сдвинутой относительно предыдущей сеточной области, поступает на первый вход второго сумматора 14. На выходе 19 первого сумматора 13 формируются коды адресов узловых процессоров новой сеточной области с учетом сдвига начала отсчета координат. Процесс циклически повторяется при обходе всех запрограммированных сеточных областей для получения частных решений, из ко торых формируется окончательное реше» ние задачи. Таким образом, устройство позволяет при одной загрузке памяти осуществить обход сеточной, области по заданному закону при занесении данных и съеме решения во всех итерациях и при получении частных решений на сдвинутых моделируемых сеточных областях.

Формула и з обретения г

Вероятностное устройство для решения конечно-разностных уравнений, содержащее элемент ИЛИ, первый и второй счетчики, первый и второй блоки памяти, первый регистр, вход записи которого является тактовым входом устройства и подключен к первому входу элемента ИЛИ, выход которого сое» динен с счетным входом первого счет» чика, установочный вход которого под ключен к выходу первого блока сравне ния и к установочному входу второго счетчика, вход записи которого соеди нен с первым входом элемента ИЛИ, второй вход которого подключен к вы» ходу второго блока сравнения, первый и второй триггеры и первый сумматор, выход которого является выходом уст» ройства, вход ввода данных которого соединен с информационными входами первого и второго блоков памяти, пер вого и второго счетчиков и первого регистра, выход которого подключен к первому входу первого блока сравне иия, второй вход которого соединен с выходом второго счетчика и с первым входом второго блока сравнения, втоз 1236499, 4

4 памяти выдает содержимое первой выбранной ячейки на первый вход второго блока 12 сравнения, а второй блок памяти 5 выдает код шага на первый вход первого сумматора 13. Последний суммирует коды, действующие йа его входах, и выдает на выход 19 устройства код начального адреса узлового процессора, к которому происходит обращение, в виде суммы кода !О шага первой эоны и кода частного адреса с выхода второго сумматора 14.

Первый блоком ll сравнения сравнивают код начального адреса с выхода второго счетчика 3 с кодом длины массива (5 с выхода первого регистра 7. При совпадении кодов с выхода первого блока

ll сравнения на установочные входы первого и второго счетчиков 2 и 3 поступает сигнал, устанавливающий их 20 в нулевое состояние. Это означает, что длина массива одно слово. Если коды не совпадают, на выходе первого блока сравнения сигнал не появляется и устройство продолжает обход сеточ- 25 ной области. Во втором блоке 12 сравнения сравнивают код начального адреса, действующего на втором входе, с кодом адреса первой зоны, поступающим на первый вход с выхода первого блока 4 памяти. Если эти коды равны происходит смена зоны), то по сигналу с выхода второго блока 12 сравнения через элемент ИЛИ 10 содержимое первого счетчика 2 увеличивают на единицу, выбирая новую зону с новым шагом обхода. Если концы не совпадают, то к текущему адресу в первом сумматоре 13 добавляют тот же код шага. Содержимое второго счетчика 3 40 увеличивают на единицу, устройство продолжает обход той же зоны сеточной области с прежним шагом. В каж дом цикле работы при задании оче редного адреса первый блок 11 срав нения сравнивает код текущего адреса с кодом конца массива для опреде ления конца массива, второй блок 12 сравнения сравнивает код текущего адреса с кодом границы зоны для оп 50 ределения смены зоны, после чего счетчики 2 и 3 устанавливаются в и tt

0 . Затем либо по сигналу с тактового входа 9 содержимое второго регист ра 8 увеличивают на единицу, либо с 55 входа 1 ввода данных во второй регистр 8 записывают код адреса необхо.. димой ячейки третьего блока 6 адреса, 123б499

Составитель В, Рыбин

Редактор П. Коссей Техред Г.Гербер Корректор О. Луговая

Заказ 3093/53

Тираж б71 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 рой вход которого подключен к выходу первого блока памяти, адресный вход которого соединен с выходом первого счетчика и с адресным входом второго блока памяти, выход которого подключен к первому входу первого сумматора, вход запуска устройства соединен с установочными входами первого и второго триггеров, выходы которых под"10 ключены к входам записи чтения соответственно первого и второго блоков памяти, о т л и ч а ю щ е е с я тем, что с целью повышения быстродействия, в него введены второй регистр, второй сумматор, третий блок

I памяти и третий триггер, выход кото рого подключен к входу записи-чтения третьего блока памяти, выход которого соединен с первым входом второго сумматора, выход которого соединен с вторым входом первого сумматора, вход ввода данных устройства подключен к информационным входам третьего блока памяти и второго регистра, выход которого соединен с адресным входом третьего блока памяти, тактовый вход устройства подключен к входу записи второго регистра, второй вход второго сумматора соединен с выходом второго счетчика.