Оперативное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к запоминающим устройствам и может быть использовано в двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти. Сущность изобретения заключается в расширении области применения устройства. Устройство содержит накопитель , формирователи сигналов, усилители считывания, коммутаторы, регистры слов, распределители сигналов, регистры адреса, блок сравнения, дешифратор адреса, коммутатор адреса, элементы задержки и элементы НЕ. Введение в известное устройство новых элементов, а именно коммутатора адреса , элементов НЕ и элементов задержки, позволяет обеспечить одновременное считывание информации для двух потребителей при совпадении адресов обращения. I ил. ьо со ot ел СП

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ÄÄSUÄÄ 1236551 дц 4 G ll С 11 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1y j

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

М А ВТОРСМОМУ СВИДЕТЕЛЬСТВУ (21) 3789526/24-24 (22) 12.09.84 (46) 07.06.86. Бюл. № 21 (72) В. П. Невский (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 647742, кл. G 11 С 11/00, 1976.

Авторское свидетельство СССР № 938317, кл. G ll С ll/00, !982.

Электронные цифровые вычислительные машины. Под ред. К. Г. Самофалова, Ки ев: Вища школа, 1976, с. 480. (54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ

УСТРОЙСТВО (57) Изобретение относится к запоминающим устройствам и может быть использовано в двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти. Сущность изобретения заключается в расширении области применения устройства. Устройство содержит накопитель, формирователи сигналов, усилители считывания, коммутаторы, регистры слов, распределители сигналов, регистры адреса, блок сравнения, дешифратор адреса, коммутатор адреса, элементы задержки и элементы НЕ. Введение в известное устройство новых элементов, а именно коммутатора адреса, элементов НЕ и элементов задержки, позволяет обеспечить одновременное считывание информации для двух потребителей при совпадении адресов обращения. 1 ил.

1236551

Изобретение относится к запоминающим устройствам и может быть использьовано вв двухпроцессорных и двухмашинных вычислительных системах в качестве общей оперативной памяти.

Цель изобретения — расширение области применения устройства за счет обеспечения одновременного считывания информации для двух потребителей при совпадении адресов обращения.

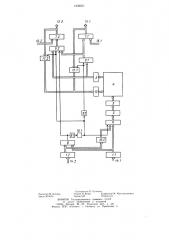

На чертеже изображена функциональная схема устройства.

Устройство содержит первый 1.1 и второй 1.2 регистры адреса, дешифратор 2 адреса, формирователь 3 адресных сигналов, накопитель 4, усилитель 5 считывания, первый 6.1 и второй 6.2 коммутаторы, первый 7.! и второй 7.2 регистры слов, блок 8 сравнения, первый 9.1 и второй 9.2 элементы

НЕ, первый 10.1 и второй 10.2 элементы задержки, коммутатор 11 адреса, первый 12.1 и второй12.2 распределители сигналов, формирователь 13 информационных сигналов, первый 14.! и второй 14.2 адресные входы, первый 5.1 и второй 15.2 информационные выходы, первый 16.1 и второй 16.2 информационные входы.

Устройство работает следующим образом.

На адресные входы 14.1 и 14.2 устройства подаются адреса двух слов, подлежащих обработке (считыванию и/или записи) . При этом возможны два случая: несовпадение и совпадение адресов.

Код первого адреса с выхода регистра 1.1 через коммутатор 11 адреса поступает на вход дешифратора 2 и на один из входов блока 8 сравнения. С выхода дешифратора 2 сигналы поступают на входы формирователя 3 адресных сигналов для возбуждения координатных обмоток накопителя 4. В результате на соответствующих координатных обмотках накопителя 4 выбраны запоминающие элементы и на входы усилителя 5 считывания поступит первое слово, считанное в соответствии с адресом, принятым на вход 14.1. Первое слово с усилителя 5 считывания поступает на первый коммутатор 6.1, а с его выхода — на первый регистр 7! слова и далее на первый 15.1 информационный выход устройства.

Код второго адреса с выхода регистра 1.2 поступает на вход второго элемента 10.2 задержки и второй вход блока 8 сравнения.

При несовпадении адресов сигнал низкого уровня с выхода блока 8 сравнения поступает на четвертый вход второго 6.2 коммутатора и запрещает передачу информации, поступающей на второй вход с выхода первого коммутатора 6.1. Через первый 9.1 элемент НЕ и первый элемент 10.! задержки, обеспечивающий задержку сигнала на время, необходимое для считывания слова в соответствии с первым адресом, он поступаS

ЗО

3s

55 ет на третий вход коммутатора 11 адреса, где разрешает передачу кода второго адреса на дешифратор 2 и запрещает прием информации с первого регистра 1.1 адреса, на третий вход второго коммутатора 6.2, где разрешает передачу информации, поступающей на первый вход с выхода усилителя 5 считывания, на второй вход второго распределителя 12.2, где разрешает передачу информации, а также через второй элемент

НЕ 9.2 — на вторые входы первого . коммутатора 6.1 и первого распределителя 12.1, где запрещает передачу информации.

Код второго адреса с выхода второго элемента 10.2 задержки, время задержки которого равно времени задержки первого элемента 10.1 задержки, поступает на второй вход коммутатора 11 адреса. С выхода последнего код второго адреса поступает на вход деш ифратора 2. С выхода дешифратора 2 сигналы, соответствующие второму адресу, поступают на входы формирователя 3 адресных сигналов для возбуждения координатных обмоток накопителя 4. В результате на соответствующих координатных обмотках накопителя 4 выбраны запоминающие элементы, и на входы усилителя 5 считывания поступает второе слово, считанное в соответствии с адресом, пришедшим на вход !4.2. Второе слово с усилителя 5 считывания поступает на первый вход второго коммутатора 6.2, а с его выхода на второй регистр 7.2 слова, с выхода которого второе слово, считанное из накопителя 4, поступает на второй информационный выход

15.2 устройства.

Установка исходного состояния регистров 1.1 и 1.2 осуществляется в начале каждого такта.

При совпадении адресов (это соответствует и исходному состоянию, когда в регистрах 1.1 и 1.2 нулевые коды) сигнал высокого уровня с выхода блока 8 сравнения поступает на четвертый вход второго коммутатора 6.2, где разрешает передачу информации, поступающей на второй вход второго коммутатора 6.2 с выхода первого коммутатора 6.1, на вход первого элемента HE 9.1, с выхода которого сигнал низкого уровня поступает на вход первого элемента 10.1 задержки, с выхода которого сигнал поступает на коммутатор 11 адреса, где запрещает прием кода второго адреса и разрешает прием адреса с первого регистра 1.1 адреса, на третий вход второго коммутатора 6.2, где запрещает прием информации, поступающей на первый вход с выходов усилителя 5 считывания, на второй вход второго распределителя 12.2, где запрещает прием информации по первому входу, и на вход второго элемента НЕ 9.2, с выхода которого сигнал высокого уровня поступает на вторые входы первого коммутатора 6.1 и первого распределителя 12.1, где разрешает передачу. информации.

123655!

Код первого адреса с выхода регистра 1.1 через коммутатор 11 адреса поступает на вход дешифратора 2, с выходов которого сигналы поступают на входы формирователя 3 адресных сигналов для возбуждения координатных обмоток накопителя 4.

В результате на соответствующих обмотках накопителя 4 выбраны запоминающие элементы и на входы усилителя 5 считывания поступает слово, считанное в соответствии с адресом обращения. Слово с выходов усили- 10 теля 5 считывания поступает на первь и вход первого коммутатора 6.1, с выхода которого слово поступает на вход первого регистра

7.1 слова и на второй вход второго коммутатора 6.2, с выхода которого слово поступает на вход второго регистра 7.2 слова.

С выходов первого 7.1 и второго 7.2 регистров слов информация поступает на первый 15.1 и второй 15.2 информационные выходы устройства соответственно.

Формула изобретения

Оперативное запоминающее устройство, содержащее накопитель, формирователь адресных сигналов, усилитель считывания, ком- 25 мутаторы, регистры слов, формирователь информационных сигналов, распределители сигналов, дешифратор адреса, блок сравнения и регистры адреса, входы которых являются адресными входами устройства, выходы первого регистра адреса подключены к одним из входов блока сравнения, к другим входам которого подключены выходы второго регистра адреса, выходы дешифратора адреса подключены к входам формирователя адресных сигналов, выходы которого подключены к адресным входам накопителя, информационные выходы которого соединены с входами усилителя считывания, выходы которого подключены к первым входам коммутаторов, выходы которых соединены с одними входами регистров слов, другие входы и выходы которых являются соответственно информационными входами и выходами устройства, выходы первого и второго регистров слов подключены к одним входам распределителей сигналов, выходы которых соединены с входами формирователя информационных сигналов, выходы которого подключены к информационным входам накопителя, отличающееся тем, что, с целью расширения области применения устройства за счет одновременного считывания информации для двух потребителей при совпадении адресов обращения, оно содержит коммутатор адреса, элементы задержки, элементы

НЕ, причем выход первого коммутатора соединен с вторым входом второго коммутатора, выход блока сравнения соединен с четвертым входом второго коммутатора и входом первого элемента НЕ, выход которого подключен к входу первого элемента задержки, выход которого соединен с третьим входом второго коммутатора, другим входом второго распределителя сигналов, входом второго элемента

НЕ и третьим входом коммутатора адреса, второй и первый входы которого соединены соответственно с выходом второго элемента задержки и выходом первого регистра адреса, а выход коммутатора адреса соединен с входом дешифратора адреса, вход второго элемента задержки подключен к выходу второго регистра адреса, выход второго элемента HE соединен с вторым входом первого коммутатора и другим входом первого распределителя сигналов.

1236551

Редактор М. Бла нар

Заказ 3014/55

Составитель О. Кулаков

Техред И. Верес Корректор М. Макснмишинен

Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4)5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4