Запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе специализированных цифровых вычислительных машин или систем обработки и нередачи цифровых данных. Целью изобретения является иовышение надежности устройства. Информация, считанная из блоков памяти анализируется в блоках контроля и сравнивается в блоке сравнения. С выходов этих блоков сигналы поступают на входы элемента И-НЕ, который вырабатывает импульс, запрещающий считывание информации из устройства. I ил. ND СО Oi ел О5

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„ЯО„„1236560 51) 4 G ll С 29/00,)3

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ @ И0Щ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3830808/24-24 (22) 12.11.84 (46) 07.06.86. Бюл. № 21 (72) А. Г. Головачев (53) 681.327(088.8) (56) Авторское свидетельство СССР № 1001099, кл. G 06 F 9/06, 1981.

Авторское свидетельство СССР № 1049982, кл. G 11 С 29/00, 1982. (54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в составе специализированных цифровых вычислительных машин или систем обработки и передачи цифровых данных.

Целью изобретения является повышение надежности устройства. Информация, считанная из блоков памяти анализируется в блоках контроля и сравнивается в блоке сравнения. С выходов этих блоков сигналы поступают на входы элемента И вЂ” НЕ, который вырабатывает импульс, запрешаюгций считывание информации из устройства. 1 ил.

1236560

Формула изобретения

Изобретение относится к цифровой вычислительной технике и может быть использовано в составе специализированных цифровых вычислительных машин (СЦВМ) или систем обработки и передачи цифровых данных.

Цель изобретения — повышение надежности устройства.

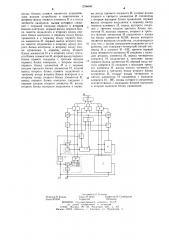

На чертеже представлена блок-схема устройства.

Устройство содержит первый 1 и второй

2 блоки памяти, первый 3 и второй 4 блоки контроля, первый 5, второй 6 и третий 7 элементы И, первый 8, второй 9 и третий

10 блоки элементов И, блок 11 сравнения, элемент 12 задержки, блок 13 элементов

ИЛИ.

Каждый из блоков 1 и 2 памяти содержит регистр 14 адреса, дешифратор 15 кода адреса, накопитель 16, информационное поле 17 накопителя, поле 18 контрольных разрядов накопителя, выходной регистр 19.

Каждый из блоков 3 и 4 контроля содержит блок 20 свертки по модулю два, блок 21 сравнения.

Устройство содержит также адресный вход 22, управляющий вход 23, выходную шину 24, являющуюся выходом устройства, четвертый 25 и пятый 26 элементы И, элемент И вЂ” НЕ 27.

Запоминающее устройство работает следующим образом.

На вход 22 устройства поступает код адреса, а. на вход 23 — сигнал опроса. В каждом блоке 1 и 2 памяти код адреса подается на вход регистра 14, а сигнал опроса— на второй вход дешифратора 15, управляющего регистром 14. При наличии сигнала опроса на входе дешифратора 15, на одном из выходов появляется сигнал, с помощью которого выбирается информация из соответствующей ячейки накопителя 16.

С выхода информационного поля 17 и поля

18 контрольных разрядов, накопителя 16 считанная информация п уупает на вход регистра 19. С выхода ш%леднего информация поступает на выходы блоков 1 и 2 памяти. Информационная ее часть с первого выхода блоков 1 и 2 памяти подается соответственно на первый и второй входы блока 11, где осуществляется поразрядное сравнение. В случае равенства сравниваемой информации на первом выходе блока

11 формируется разрешающий потенциал для элемента 5.

При наличии на втором входе элемента

5 сигнала опроса, этот сигнал, пройдя элемент 5, поступает на третий вход блока

10 элементов И. На первый вход блока 10 элементов И подаются контрольные признаки информации считываемые из блока памяти, а на второй вход блока 10 — — информационная часть, считанная из блока 2 памяти. При наличии на третьем входе блока

10 сигнала опроса, поступившая на его первый и второй входы информация переда15

40 15

50 на через блок 13 на выходную шину 24. В случае неравенства информации, поступающей на вход блока 11, на его первом выходе появляется сигнал запрета для элемента 5, а на втором выходе — - сигнал разрешения для элементов 6 и 7. Информация с выходов блоков 1 и 2 памяти поступает соответственно на входы блоков 3 и 4 контроля, где ее информационная часть свертывается с помощью блока 20 по заложенным контрольным признакам. Результаты свертки сравниваются в каждом блоке 3 и 4 с контрольным признаком (признаками) блоком

21 сравнения.

Сигнал опроса подается на первые входы блоков 8 и 4 контроля с выхода элемента 12 задержки (для синхронизации работы устройства). В случае равенства результата свертки информационной части и контрольного признака (признаков) в блоке 3, а также наличия сигнала опроса на входе этого блока, блок 21 блока 3 формирует сигнал, который поступает на вход элемента 6.

При наличии на втором входе элемента 6 разрешения на его выходе появляется сигнал, который поступает на первый вход элемента 25, где при наличии сигнала разрешения на втором входе, на выходе элемента 25 формируется сигнал, который поступает на третий вход блока 8, по этому сигналу информация, поступающая на вход блока 8, передается через блок 13 элементов

ИЛИ на выходную шину 24 устройства.

B случае неравенства результатов свертки информационной части и контрольного призHBKB (признаков) в блоке 3, этот блок не вырабатывает сигнал опроса. В работу включаются цепи, обеспечивающие считывание информации из блока 2 памяти через блок 9. Работа блока 4 и формирование им сигнала опроса для элемента 7 происходит аналогично. При наличии разрешающего сигнала на втором входе элемента 7 и на втором входе элемента 26, с выхода последнего снят сигнал, переписывак>щий информацию из блока 2 памяти через блок 9 и элементы ИЛИ 13 на выходную шину 24 устройства.

Сигнал, сформированный в случае равенства результата свертки информационной части и контрольного признака (признаков) блока 3 и 4, поступает на первый и третий входы элемента 27 соответственно, на второй вход которого подается сигнал неравенства считываемой информации с второго выхода блока 11. B случае одновременного появления сигналов на входах элемента 27, он вырабатывает запрещающий сигнал, поступающий на вторые входы .элементов

25 и 26 и тем самым, прекращак щий считывание информации из устройства.

Запоминающее устройство, содержащее блоки памяти, первые входы которых являются адресным входом устройства, вторые

1236560

Составитель О. Кулаков

Редактор М. Б.чанар Техред И. Верес Корректор М. Самборская

Заказ 3015/56 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и оч крытий

113035, Москва, Ж вЂ” 35. Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4 входы блоков памяти являются управляющим входом устройства и подключены к второму входу первого элемента И и к входу элемента задержки, выход которого соединен с первыми входами первого и второге блоков контроля, первый выход первого блока памяти подключен к второму входу первого блока контроля, к первому входу блока сравнения и к первому входу первого блока элементов И, первый выход второго блока памяти подключен к второму входу второго блока контроля, к второму входу блока сравнения, к первому входу второго блока элементов И и к второму входу третьего блока элементов И, второй выход первого блока памяти соединен с третьим входом первого блока контроля, с вторым входом первого блока элементов И и с первым входом третьего блока элементов И, второй выход второго блока памяти подключен к третьему входу второго блока контроля и к второму входу второго блока элементов И, выход первого блока контроля соединен с первым входом второго элемента И, выход второго блока контроля подключен к первому входу третьего элемента И, вторые входы второго и третьего элементов И соединены с вторым выходом блока сравнения, первый выход которого подключен к первому входу первого элемента И, выход которого соединен с третьим входом третьего блока элементов И, выходы первого, второго и третьего блоков элементов И соединены .с входами блока элементов ИЛИ, выход которого является выходом устройства, отличающееся

10 тем, что, с целью повышения надежности устройства, оно содержит четвертый. пятый элементы И и элемент И вЂ” НЕ, причем первый вход четвертого элемента И соединен с выходом второго элемента И, выход четвертого элемента И подключен к третьему входу первого блока элементов И, первый вход пятого элемента И соединен с выходом третьего элемента И, выход пятого элемента И подключен к третьему входу второго блока элементов И, вторые входы четвертого и пятого элементов И соединены с выходом элемента И вЂ” HE, входы которого соединены соответственно с выходами блоков контроля и вторым выходом блока сравнения.