Декодер

Иллюстрации

Показать всеРеферат

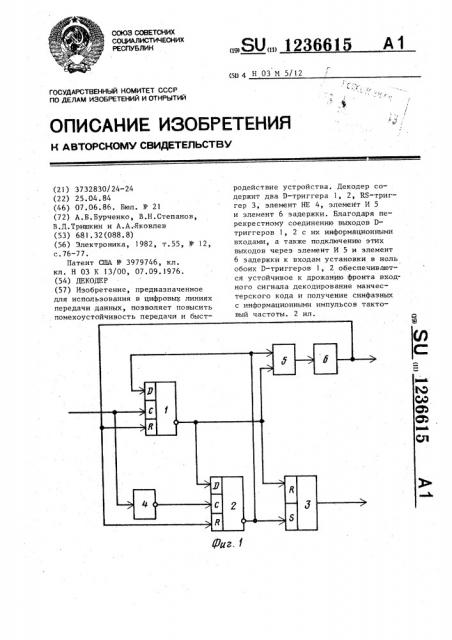

Изобретение, предназначенное для использования в цифровьцс линиях передачи данных, позволяет повысить помехоустойчивость передачи и быстродействие устройства. Декодер содержит два D-триггера 1, 2, RS-триггер 3, элемент НЕ 4, элемент И 5 и элемент 6 задержки. Благодаря перекрестному соединению выходов D- триггеров 1, 2с их информационными входами, а также подключению этих выходов через элемент И 5 и элемент 6 задержки к входам установки в ноль обоих D-триггеров 1, 2 обеспечиваются устойчивое к дрожанию фронта входного сигнала декодирование манчестерского кода и получение синфазных с информационными импульсов тактовый частоты. 2 ил. (Л V и S tsD оо о О5 ел Г Фиг. 1

союз советсних

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (д11 4 Н 03 N 5/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Фиг. 1

ГОсудАРстВенный номитет сссР по делАм изОБРетений и отнРытий

Н А8ТОРСНОМУ СВИДЕТЕЯЬСТВУ (21) 3732830/24-24 (22) 25.04.84 (46) 07.06 ° 86. Бюл. Р 21 (72) А.Б.Бурчеико, В.Н.Степанов, В.Д.Тришкин и А.А.Яковлев (53) 681,32(088 ° 8) (56) Электроника, 1982, т.55, И - 12, с.76-77.

Патент CUIA 9 3979746, кл. кл. Н 03 К 13/00, 07.09.1976. (54) ДЕКОДЕР (57) Изобретение, предназначенное для использования в цифровых линиях передачи данных, позволяет повысить помехоустойчивость передачи и быст„„SU„„1236615 А 1 родействие устройства. Декодер содержит два D-триггера 1, 2, RS-триггер 3; элемент НЕ 4, элемеит И S и элемент 6 задержки. Благодаря перекрестному соединению выходов Dтриггеров 1, 2 с их информационными входами, а также подключению этих выходов через элемент И 5 и элемент

6 задержки к входам установки в ноль обоих D-триггеров 1, 2 обеспечиваются устойчивое к дрожанию фронта входного сигнала декодирование манчестерского кода и получение синфазных с информационными импульсов тактовый частоты. 2 ил.

1236615 этом

З0 Ф о р м у л а и з о б р е т е н и я

Изобретение относится к автоматике и вычислительной технике и может быть использовано в цифровых системах передачи данных.

Цель изобретения — повьппение поме- 5 хоустойчивости и быстродействия.

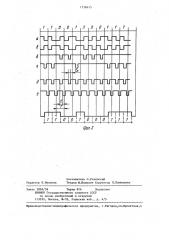

На фиг.! приведена функциональная схема декодера; на фиг.2 — временные диаграммы его работы.

Декодер содержит первый и второй

D-триггеры и 2, RS-триггер 3, элемент НЕ 4, элемент И 5 и элемент 6 задержки. Вход декодера подключен к входу синхронизации первого D-триггера 1 и через элемент НЕ 4 — к вхо,,у синхронизации второго D-триггера, Инверсные выходы первого и второго

D-триггеров 1 и 2 подключены к информационным входам соответственно второго и первого В-триггеров 2 и 1, к соответствующим входам RS-триггера

3 и к входам элемента И 5, выход последнего через элемент 6 задержки подключен к входам установки в ноль

D-триггеров 1 и 2. Выходы RS-триггеpà 3 и элемента 6 задержки являются соответственно информационным выходом и выходом синхронизации устройства.

Принцип работы декодера поясняется временными диаграммами (фиг.2) и заключаегся в следующем. тельность синхроимпульсов тактовой частоты (фиг,2 ), задние фронты которых расположены в центре тактового интервала Т. Элемент 6 задержки осуществляет сдвиг импульсов тактовой частоты на величину задержки ., при где ).„- длительность импульсов низкого уровня на выходе элемента И 5.

В результате при декодировании ведется анализ только фазовых переходов сигнала в центре битового интервала независимо от логического уровня сигнала на входе с возможностью варьирования параметров на любой тактовой частоте. Одновременно декодер обеспечивает выдачу синфазных с информационными импульсов тактовой частоты, благодаря перекрытию зон начала и конца тактового интервала. Все это позволяет уменьщить воздействие помехи типа дрожания фронта входного сигнала и увеличить скорость передачи информации на входе декодера.

Последовательность импульсов в коде "Манчестер" (фиг. 2а) поступает с входа декодера на С-вход первого

D-триггера 1 и через элемент НЕ 4 — 35 на С-вход второго D — триггера 2 (фиг.28). Работа D-триггеров 1 и 2 иллюстрируется диаграммами (фиг.2Ь,L) и проходит под управлением выходных сигналов D-триггеров 2 и 1 и импульсов обнуления с выхода элемента 6 задержки (фиг. 2 e) . Изменение исходного состояния D-триггеров 1 и 2 происходит в середине битового интервала. Импульсы низкого уровня с инверсных выходов D-триггеров 1 и 2 поступают соответственно на R u S входы RS-триггера 3 и на входы элемента И 5. Сигнал на выходе RS-триггера

3 представляет собой восстановленный 50 сигнал исходного двоичного кода (фиг.2 ) . Элемент И 5 осуществляет логическое сложение последовательностей импульсов низкого уровня с выходов П-триггеров 1 и 2 и выдает íà 55 вход элемента 6 задержки последоваДекодер, содержащий первый и второй D-триггеры,, элемент задержки и элемент НЕ, выход которого соединен с входом синхронизации второго Dтриггера, вход установки в нуль которого подключен к выходу элемента задержки, о т. л и ч а ю шийся тем, что, с целью повышения помехоустойчивости и быстродействия, в него введены RS-триггер и элемент И, выход которого подключен к входу элемента задержки, выход которого является выходом синхронизации устройства и соединен с входом установки в нуль первого D-триггера, ьход синхронизации которого объединен с входом элемента НЕ и является входом устройства, инверсный выход каждого D-триггера подключен к информационному входу другого D-триггера, к соответствующему входу элемента И и к соответствующему входу

RS-триггера, выход которого является информационным выходом устройства.

1236615

Составитель Q.Ревинский

Техред И.Попович Корректор Л.Пилипенко

Редактор В.Иванова

Заказ 3098/58 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.ужгород,ул.Проектная,4