Преобразователь кода системы остаточных классов в позиционный код

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при построении систем передачи информации, устройств модулярной арифметики, специализированных многопроце ссорных магистрально-модульных информационно-управляющих систет. Целью изобретения является расширение функциональных возможностей за счет работы в произвольной системе модулей. Поставленная цель достигается тем, что в преобразователь кода системы остаточных классов в позиционный код, содержащий сумматоры по модулю, накапливающий сумматор, триггеры и элементы И, элемент ИЛИ, введены схемы сравнения, регистры, умножители, блоки памяти, дифференцирующие элемеН1Ы дешифратор, коммутатор, одновибратор, 1 ил. с to (Л с го со 05 О)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„SU„„1236617 у 4 Н 03 N 7/18

ГОСУДАРСТВЕННЫЙ HOMHTET СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ (21) 3813600/24-24 (22) II.I 1.84 (46) 07.06.86. Бюл. ¹ 21 (72) К. N. Сагдеев и Н. И. Швецов (53) 681.3(088.8) (56) Авторское свидетельство СССР № 1008729, кл. G 06 F 5/02, 1981.

Авторское свидетельство СССР № 1133669з кл. G 06 F 5/02ь 1983 ° (54) ПРЕОБРАЗОВАТЕЛЬ КОДА СИСТЕИЫ

ОСТАТОЧНЫХ КЛАССОВ В ПОЗИЦИОННЫЙ КОД (57) Изобретение относится к вычислительной технике и может быть использовано при построении систем передачи информации, устройств модуляр" ной арифметики, специализированных многопроцессорных магистрально-модульных информационно-управляющих систем .

Целью изобретения является расширение функциональных возможностей за счет работы в произвольной системе модулей

Поставленная цель достигается тем, . что в преобразователь кода системы остаточных классов в позиционный код, содержащий сумматоры по модулю, накапливающий сумматор, триггеры и элементы И, элемент ИЛИ, введены схемы сравнения, регистры, умножители, бло" ки памяти, дифференцирующие элемен"ы, дешифратор, коммутатор, одновибратор.

1 ил.

12366)7 оды шифраг

100...0

О О ... 0

0l0...0

0 ... О

1 1 ... О

001...0

000...0

) l ... ) Изобретение относится к вычислительной технике и может быть использовано при построении систем передачи информации, устройств модулярной ариф. метики, специализированных многопроцессорных магистрально-модупьных информационноуправЛяющих систем.

Целью изобретения является расширение функциональных возможностей за счет работы н произвольной системе момодулей.

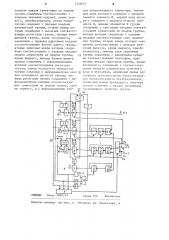

На чертеже представлена схема преобразователя кода системы остаточных классов в позиционный код.

Преобразователь кода системы остаточных классов в позиционный код ссдержит группу схем сравнения 1.1-).п1 .(n — число модулей), группу триггеров 2.1-2 .n-l, группу элементов

И 3,1 3. n"1; группу сумматоров по модулю 4.1-4. п-l, накапливающий сум» матор 5, элемент И 6, одновибратор 7, дешифратор 8 двоичного кода в унитарный, группу дифференцирующих элементов 9.1-9. п-2, элемент ИЛИ 10, группу регистров 11.)-ll. n-l, группу блоков 12.1 12.п-2 памяти, группу умножителей 13.1-.13. тгl,, коммутатор 14, элемент И 15, тактовый вход 16 преобразователя, входы 17 ° 1-17.п значений модулей преобразователя, входы 18.118.п-) значений вычетов преобразователя, выходы 19 и 20 соответственно результата и окончания работы преобразователя.

Дифференциальные элементы 9.1.9 п-2 преобразуют скачок напряжения на их входах B одиночный импульс.

Одновибратор 7 с приходом на, его вход одиночного импульса формирует нуленой импульс требуемой длительности, Дешифратор 8 может быть реализован н соответствии с таблицей истинности.

Из блока 12. j памяти по величинам

В и Р, поступающим на его первый и

) „) второй адресные входы, выбирается веФ личина В

).

В работе преобразователя кода системы остаточных классов н позиционный код используется следующий алгоритм, Любое число А натурального ряда может быть выражено н обобщенной по

)О зиционной системе (ОПС} как п-1

А = а +а Р +...+а П P

1 n где а, - коэффициенты ОПС;

)5 Р— основания ОПС.

В то же время, число А н системе вычетов с основаниями аналогичными

ОПС, записывается н виде

А = (Ф1 в Ыг ... юсуп} (2} где ; вычет от числа по модулю P- .

Если выражение (1} преобразователь

rro модулям Р;, то мы получим систему уравнений, описывающую преобразование!

А! = oc = а, )А! = М7 = tà "7P I ð

ЗО г (3}

° ° ° А = о = )а, +агР + ° ..а П Р! и

Pn °

Преобразователь кода системы остаточных классов в позиционный код работает следующим образом.

В исходном состоянии на выходы

18 ° 1-18. и поступают значения с - д на выходы 17.1-17.r). — значения P -P п в накапливающий сумматор 5 и суммато ры 4.)-4.п-l по модулю записана не

40 личина кода млацшего вычета Ы,, триг. геры обнулены, на выходе одновибратора 7 присутствует потенциал логичес кой ециницы, в регистры !),l-ll, n-!

45 записан код младшего модуля Р<, пер» ный вход коммутатора 14 скоммутирован на его выход и величина кода Р поступит на первые нходы умножителей

13.1-13.п-l, на вторые входы которых с выходов регистров 11,1-11, n-I поступает код модуля P н результате на выходах умножителей )3.1- 13, п-1 появится код величины P„ P» которая поступает на информационный вход ре гистра 11. и-1 и на первые входы 8 блоков 12.1-.12.п-2 памяти, на втором входе «)-го блока памяти будет присутствовать код Р.. . на входах ре12366

3 гистров 11,1-11.п-2 будет присутст1Ф вовать код величины!Р, Р2! ., т,е. ! константа ОПС,. где j = 3,...,n, а на входе регистра ll.n-l — код величины Р, Р, но в регистры не запишутся, поскольку для этого необходимо наличие импульса "записи" на их управляющих входах. Таким образом, на входы сумматоров 4.1-4.п-l накапли вающего сумматора 5 подается код P . !О

Первый тактовый импульС по входу

16, пройдя через элемент И 6, посколь. ку на других его входах присутствуют потенциалы логических единиц, разрешит подсуммирование кода Р! в сум- !5 маторах 4.1-4.п-l и накапливающий сумматор 5 К 1,, С дальнейшим поступлением тактовых импульсов к содержимому сумматоров будет добавляться в каждом такте код P до тех пор, 20 пока не будет выполнено равенство и= а, +а,„ Рlð и на выходе схемы 1. 1 сравнения появится единичный потенциал, который переведет триггер 2.1 в единичное состояние. На инверсном выходе триггера 2,1 будет логический "0", кото рый исключит поступление дальнейших

30 тактовых импульсов на тактовый вход сумматора 4.1. С целью исключения лишнего суммирования кода Р, в другие сумматоры по модулю и накапливающий сумматор 5 на выходе суммирующего дифференцирующего элемента 9.1, З5 подключенному к ппямому выходу триггера 2.1, появится импульс положительной полярности, который, пройдя через элемент ИЛИ 10, вызовет появление на выходе одновибратора 7 нуле" 40 вого импульса с требуемой длительностью. Этот импульс запретит прохождение тактового импульса через элемент И 6. Импульс с выхода дифференцирующего элемента 9.1 разрешит также запись в регистры 11,1-11,п-2

+ кода константы Р,Р lp, а в регистр

11 и-1 кода Р! Р2 В тоже время с появлением логической "1" на прямом выходе триггера 2.1 изменит свое зна- 0 чение информация на входе дешифратора 8, на выходе которого появится код, который скоммутирует второй вход коммутатора 14 на его выход, т.е. подает на первые входы всех умножителей

13,1 13.п-l ксд P2 .

Процесс нахождения коэффициентов а,..... .,а ОПС протекает аналогично

l7 4 .нахождению а, При срабатывании схемы l.п-! срабатывает триггер 2.п-l, прямой вь!ход которого является выходом окончания работы, а инверсный через элементы.И З.n-l и И 15 запрещает дальнейшее изменение содержимого сумматоров 4.п-l и 5, при этом в накапливающем сумматоре 5 будет содержаться код числа А, а через элемент

И 6 запретит прохождение тактовых импульсов.

Формула изобретения

Преобразователь кода системы остаточных классов в позиционный код, содержащий накапливающий сумматор, элемент ИЛИ, группу триггеров, первый элемент И, группу сумматоров по модулю, группу элементов И, причем выход накапливающего сумматора является выходом результата преобразователя, нулевые выходы триггеров группы соединены с первыми входами соответствующих элементов И группы, первый вход первого элемента И соединен с вторыми входами элементов И группы, о тл и ч а ю шийся тем, что, с целью расширения функциональных возможностей за счет работы в произвольной системе модулей, -в него введены группа схем сравнения, группа умножителей, группа дифференцирующих элементов, дешифратор двоичного кода в унитарный, коммутатор, второй эле» мент И, одновибратор, группа регистров, группа блоков памяти, причем нулевой выход последнего триггера группы соединен с вторым входом первого элемента И и с первым входом второго элемента И, второй и третий входы которого соединены соответственно с тактовым входом преобразователя и с выходом одновибратора, вход которого соединен с входами записи регистров группы и с выходом элемента ИЛИ, входы которого через соответ ствующие дифференцирующие элементы группы соединены с входами дешифрато ра двоичного кода в унитарный, выходы которого соединены соответственно с управляющими входами коммутатора, информационные входы которого соединены соответственно с входами значе ний модулей, кроме первого и последнего, преобразователя, вход значения первого модуля преобразователя соединен с информационным входом первого сумматора по модулю группы, входы

1236(17

БНИИПИ Заказ 3099/59 Тираж 816 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная„ задания модуля сумматоров по модулю группы соединены соответственно с входами значений модулей, кроме первого, преобразователя, выход коммутатора соединен с первыми входами умножнтелей группы, вторые входы которых соединены с выходами соответствующих регистров группы, выходы умножителей группы, кроме последнего, 10 соединены с первыми адресными входами соответствующих блоков памяти группы, вторые адресные входы которых соединены соотвЕтственно с входами задания модуля сумматоров по модулю группы, 15 кроме первого, выходы блоков памяти группы соединены с информационными входами соответствующих регистров группы, выход последнего умножителя группы соединен с информационным вхо- 20 дом последнего регистра группы, вьгходы регистров группы соединены с информационными входами соответствующих сумматоров по модулю группы, кроме первого, и с информационным вхо- 25

1 дом накапливающего сумматора, тактовый вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом второго элемента И, выходы элементов И группъ| соединены с тактовыми входами соответствующих сумматоров по модулю группы, выходы которых соединены с первыми входами соответствующих схем сравнения группы, вторые входы которых соединены соответственно с входами значений вычетов, кроме первого, преобразователя, выходы схем сравнения группы соединены с единичными входами соответствующих триггеров, единичные выходы триггеров группы, кроме последнего, соединены с соответствующими входами дешифратора двоичного кода в унитарный, единичный выход последнего триггерагруппы являетсявыходом окончанпяработы преобразователя, единичный выход предыдущсго триггера группы соединен с входом разрежения последующего триггера группы.

ТУ