Устройство для извлечения квадратного корня

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой вычислительной технике и может быть использовано в специализированных вычислителях, радиотехнических устройствах и аппаратуре передачи дан-, ных, когда предъявляются требования к быстродействию вычислений при простоте реализации. Целью изобретения является повьппение быстродействия и точности за счет параллельной процедуры выполнения всех операций и введения нормирования входных чисел. В результате этого устраняется зависимость времени вычисления от разрядности входных чисел. Входное число поступает на дешифратор старшей единицы кода аргумента, который управляет процедурой нормирования аргумента в первом блоке сдвига. Блоки памяти нормированной функции, коэффициентов аппроксимации служат для получения величин, необходимых для вычисления умножителя и сумматора аппроксимирующей функции. Значение результата нормируется в обратную сторону во втором блоке сдвига и записывается в регистр результата с помощью распределителя импульсов 1 ил. I (П IN9 оо 00 о 2

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ .

К ASTOPCKOMY СВИДЕТЕЛЬСТВУ .Ц (21) 3814862/24-24 (22) 19,11-.84 (46) 15.06.86. Бюл.В 22 (72) Ь.С.Скляр (53) 681.325(088.8) (56) Авторское свидетельство СССР

М 1101818, кл. С 06 Р 7/552, 1982.

Авторское свидетельство СССР

11 857982, кл. G 06 F 7/552, 1980. (54) УСТРОЙСТВО ДНЯ ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ (57) Изобретение относится к цифровой вычислительной технике и может быть использовано в специализированных вычислителях, радиотехнических устройствах и аппаратуре передачи дан-, ных, когда предъявляются требования. к быстродействию вычислений при простоте реализации. Целью изобретения является повышение быстродействия

„„Я0„„1238064 А1 и точности эа счет параллельной процедуры выполнения всех операций и введения нормирования входных чисел.

В результате этого устраняется зависимость времени вычисления от разрядности входных чисел. Входное число поступает на дешифратор старшей единицы кода аргумента, который управляет процедурой нормирования аргумента в первом блоке сдвига.

Блоки памяти нормированной функции, коэффициентов аппроксимации служат для получения величин, необходимых для вычисления умножителя и сумматора аппроксимирующей функции. Значение результата нормируется в обратную сторону во втором блоке сдвига и записывается в регистр результата с помощью распределителя импульсов

1 ил, Изобретение относится к вычислительной технике и может быть использовано в быстродействующих специализированных вычислителях.

Цель изобретения — повышение быстродействия вычислений за счет устранения влияния количества значащих разрядов аргумента на время вычисления и повьппение точности за счет нормирования аргументов.

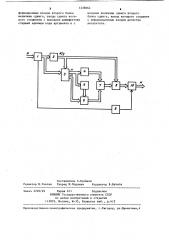

На чертеже представлена функциональная схема устройства.

Устройство содержит входной регистр 1, дешифратор 2 старшей единицы кода аргумента, первый блок 3 сдвига, блок 4 памяти нормированной функции, блок 5 памяти коэффициентов аппроксимации, умножитель 6, сумматор 7, второй блок 8 сдвига, распределитель 9 импульсов, регистр

10 результата.

Устройство работает следующим образом.

Входное N-разрядное число записывается во входной регистр 1 по тактовому импульсу, вырабатываемому распределителем 9 импульсов.

С выхода входного регистра 1 аргумент поступает на информационный вход первого блока 3 сдвига. Выходы дешифратора 2 старшей единицы кода аргумента определяют величину сдвига в сторону старших разрядов первого блока 3 сдвига.

С выхода первого блока 3 сдвига старшие и разрядов (определяющее число Х) поступают на блок 4 памяти нормированной функции, где выбирается значение в узловой точке Y, =

=АГХ, где А — постоянный коэффиции ент (2 — число узловых точек нормированной функции). Одновременно эти и разрядов поступают на адресные входы блока 5 памяти коэффициентов аппроксимации и выбирается коэффициент наклона аппроксимирующих прямых. Младшие (N-h) разрядов с выхода первого блока 3 сдвига (Н— разрядность аргумента) поступают на вход первого сомножителя умножителя 6, на другой вход которого поступает значение К .

Для получения функций Y--Y+KX используется сумматор 7. С выхода сумматора результат поступает на второй блок 8 сдвига, где осуществляется сдвиг в сторону младших разрядов, причем если блок 3 сдвш а

238064 сдвигает на 2L разрядов (L=l,..., N/2) в сторону старших разрядов, то блок 8 сдвига осуществляет сдвиг на L разрядов в сторону младших разрядов.

Значение с выхода блока 8 сдвига по сигналу от распределителя 9 импульсов записывается в регистр 10 результата.

Формула изобретения

t5

Устройство для извлечения квадратного корня, содержащее входной регистр, регистр результата, распределитель импульсов, дешифратор старmeA единицы кода аргумента и блок памяти нормированной функции, причем вход аргумента .устройства является информационным входом входного регистра, выходы которого соединены с входами дешифратора старшей единицы кода аргумента, выход регистра результата является выходом значения квадратного корня устройства, синхронизирующие входы входного регистра и регистра результата соединены с первым и вторым выходами распределителя импульсов соответственно, о т л и ч а— ю щ е е с я тем, что, с целью повы" щения быстродействия за счет устранения влияния количества значащих разрядов аргумента на время вычисления, в него дополнительно введены два блока сдвига, блок памяти коэффициентов аппроксимации, умножитель и сумматор, причем выходы разрядов входного регистра соединены с информационными входами первого блока сдвига, выходы старших разрядов h которого (где 2 — число узловых точек аппроксимации нормированной функции) соединены с адресными входами блока памяти нормированной функции, выходы N- и младших разрядов первого блока сдвига (где N — - разрядность аргумента) соединены с входом первого сомножителя умножителя, вход второго сомножителя которого соединен с выходами блока памяти коэффициентов аппроксимации, адресные входы которого соединены с выходами ь старших разрядов первого блока сдвига, выход умножителя соединен с первым информационным входом сумматора, второй информационный вход которого соединен с выходом блока памяти нормированной функ-. ции, выход сумматора соединен с ин1238064

Составитель С.Куликов

Редактор М.Товтин Техред Х.Ходанич Корректор В.Бутяга

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Заказ 3292/49

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная,4 формационным входом второго блока величины сдвига, входы сдвига которого соединены с выходами дешифратора старшей единицы кода аргумента и с входами величины сдвига второго блока сдвига, выход которого соединен с информационным входом регистра результата.