Устройство для вывода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники. Целью изобретения является повьппение быстродействия за счет записи массива изображения в блок памяти путем одновременной записи нескольких точек изображения , расположенных по разным адресам. Цель достигается введением в устройство группы блоков памяти и коммутатор ов. 3 ил.

СОЮЗ СОВЕтСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

091 А1 (!9) (11) (504 С 06 F 13 00 (21) 3810772/24-24 (22) 10. 11.84 (46) 15.06.86. Бюл. 11 22 (71) Московский ардена Трудового

Красного Знамени инженерно-физический институт (72) О.Н.Цапко и В.Б.Шувалов (53) 681. 327. 21 (088.8) (56) Авторское свидетельство СССР

М - 543960, кл. G 06 F 13/00, 1977..

Авторское свидетельство СССР

К - 930335, кл. G 06 F 13/00, 1982, (54) УСТРОЙСТВО ДЛЯ ВЫВОДА ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники. Целью изобретения является повышение быстродействия за счет записи массива изображения в блок памяти путем одновременной записи нескольких точек изображения, расположенных по разным адресам.

Цель достигается введением в устройство группы блоков памяти и коммутаторов. 3 ил.

38091

Изобретение относится к вычислительной технике, предназначено для вывода информации из ЭВИ и может использоваться в системах автоматизации проектирования и конструирования, при автоматизированной обработке данных, в диалоговых системах.

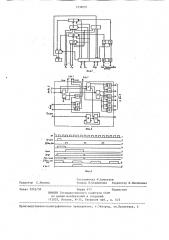

Цель изобретения — повышение быстродействия устройства, На фиг. 1 представлена схема предлагаемого устройства, на фиг. 2 схема блока управления, на фиг. 3— временная диаграмма..

На фигурах приняты следующие обозначения: блок 1 памяти, телевизионный индикатор 2; преобразователь 3 кода, блок 4 управления; блок 5 синхронизации коммутатор б, первая группа элементов И 7; первый регистр 8; второй регистр 9; дешифратор 10;первый триггер 11, первый и второй элементы И 12 и 13, вторая и третья группы элементов И 14 и 15, второй и третий триггеры 16 и 17, четвертая группа элементов И 18; третий элемент

И 19, группа блоков 20 памяти, группа коммутаторов 21.

Устройство работает следующим образом.

Блок 5 синхронизации вырабатывает импульсы, соответствующие требуемой дискретизации растра экрана телевизионного индикатора 2, и управляет разверткой последнего. Импульсы поступают на блок 4 управления, осущест вляя его временную привязку к телевизионному синхросигналу.

Блок 1 памяти и группа блоков 20 памяти образуют И одноразрядных линеек. Коммутатор 6 и группа коммутаторов 21 состоят из h коммутаторов и обеспечивают подключение своего независимого адреса А, с входов устройства к соответствующему блоку памяти. Блок 4 управления под действием информационных сигналов D;, поступающи . с входов устройства, и управляющих сигналов с входов устройства формирует необходимую последовательность импульсов для работы блоков 1 и 20 памяти, коммутаторов 6 и 21 и преобразователя 3 кодов. В режиме считывания информации сигналы с выходов блока 5 синхронизации через коммутатор 6 и группу коммутаторов 21 подключаются к блоку 1 памяти и группе блоков 20 памяти, причем считывание бит из них производится одновременно из каждого блока по одному адресу А,„1,Считанное из блоков памяти

11-разрядное слово поступает в преобразователь 3, где преобразуется в телевизионный видеосигнал, который совместно с синхроимпульсами из блока 5 синхронизации поступает на телевизионный индикатор 2.

При записи информации на входы устройства подаются соответственно и адресов А ., и разрядов информационных признаков и управляющие сигналы, под воздействием которых блок 4 управления переключает коммутаторы таким образом, что на входы соответствуюпртх блоков 1 и 20 памяти поступают соответствующие адреса A, а на информационные входы — соответствующие информационные признаки D;. Одновременно формируется временная диаграмма цикла записи, по которой осуществляется запись информационных признаков D (О или 1) в соответст1 вующие i-e блоки памяти по адресам А ° (1 = 1,q). Выбор линеек блоков памяти, в которые необходимо произвести запись, осуществляется по П -разрядному коду, записанному из ЭВМ в регистр 8 по входным шинам первого регистра 8. Для выделения разрешенных линеек служит группа 7 элементов И, на первые входы которых поступают сигналы с выходов. регистра 8, а на вторые входы, объединенные между собой, — сигнал записи из блока 4 управления.

Распределитель импульсов 4 работает следующим образом. В режиме считывания информации из блоков памяти он формирует временную диаграмму цикла считывания и управляет работой преобразователя 3. Сигналы временной диа-. граммы цикла считывания формируются на выходах разрядов второго регистра 9„ который в течение цикла считывания выцвигает поразрядную логическую " 1", а в конце цикла сбрасывает— ся в нулевое состояние сигналов с выхода дешифратора 10, который вырабатывает временную последовательность импульсов на протяжении цикла считывания. Этим же сигналом окончания цикла перебрасывается первый триггер 11, который определяет на какой регистр и мультиплексор преобразователя 3 поступают сигналы записи с выходов первого 12 и второго 13 элементов И и сигналы управления мульти091 з 1238 плексорами с выходов второй 14 и третьей 15 групп элементов И.

Временная диаграмма режима записи информации приведена на фиг. 3. По сигналу требования записи (диагр.2) второй триггер 16 устанавливается в состояние логической " 1" (диагр.4).

Третий триггер 17 под управлением сигнала с дешифратора 10 (диагр.3) выделяет ближайший цикл обращения к 1Г группе блоков 1 памяти (диагр.5) и сбрасывает второй триггер 16. Сигнал выделения цикла разрешает прохождение информации (диагр.6) через четвертую группу элементов И 18 на информа- 15 ционные входы группы блоков 1 памяти (диагр.7) и прохождение строба записи (диагр .8) через третий элемент И 19 на входы группы элементов И 7 (диагр.9), осуществляя цикл записи . 20 информации в блоки памяти.

Таким образом; использование изобретения позволяет повысить быстродействие устройства путем независимой записи информации по каждой точке 25 растрового массива.

Формула изобретения

Устройство для вывода информации, содержащее блок памяти, коммутатор,. блок синхронизации, преобразователь кода, телевизионный индикатор, первый выход блока синхронизации соединен с синхровходом телевизионного индикатора, выход блока памяти под35 ключен к одному входу преобразователя кода, выход которого соединен с информационным входом телевизионного индикатора, второй и третий выходы

40 блока синхронизации подключены к управляющим входам коммутатора, информационные входы которого являютСя адресными входами устройства, а выход соединен с адресным входом блока па45 мяти, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия устройства, в него введены группа коммутаторов, группа блоков памяти, первый регистр, первая группа

50 элементов И и блок управления, содержащий второй регистр, дешифратор, с первого по третий триггеры, с первого . по третий элементы И, со второй по четвертую группы элементов И, четвер55 тый выход блока синхронизации соединен с синхровходом второго регистра и с первым входом дешифратора, пятый выход — с вторым входом дешифратора, с первыми входами элементов И второй и третьей групп, вторые входы которых подключены к выходам первого триггера, которые. соединены с первыми входами первого и второго элементов И, вторые входы которых подключены к первому выходу дешифратора, второй выход которого соединен с входом первого триггера и с входом сброса второго регистра, вход данных которого является шиной логической единицы устройства, третий выход дешифратора подключен к одному установочному входу третьего триггера, другой установочный вход которого соединен с выходом второго триггера, один вход установки которого подключен к инвертирующему выходу третьего триггера, неинвертирующий выход которого подключен к первым входам третьего элемента И, элементов И третьей группы и к стробирующим входам коммутатора и коммутаторов группы, другой вход установки второго триггера является управляющим входом устройства, вторые входы элементов И четвертой группы являются информационными входами устройства, а выходы подключены к информационным входам блока памяти и блоков памяти группы входы "Чтение-запись" которых подключены к первому выходу второго регистра, второй выход которого соединен с вторым входом третьего элемента И, выход которого подключен к первым входам элементов И первой группы, вторые входы которых соединены с выходами первого регистра, входы которого являются кодовыми входами устройства, а выходы подключены к:стробирующим входам блока памяти и блоков памяти группы соответственно, выходы первого и второго элементов И и выходы элементов И второй и третьей групп, подсоединены к управляющим входам преобразователя кода, информационные входы коммутаторов группы являются соответствующими адресными входами устройства, управляющие входы соединены с вторыми и третьим выходами блока синхронизации, а выходы подключены к адресным входам блоков памяти группы, выходы которых подключены к соответствующим входам преобразователя кодов.

1238091

toJ длма юАси

Кдл.7

fl ол.7

Редактор С.Лисина

Заказ 3293!50

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Ужгород, ул.Проектная, 4

7Ф

7р. ламп

Ш Acr.йы

Цыкл . Negr

E &.! инц7.

ЯЕых ранг

ФЕ

1 г я й

Составитель И.Алексеев

Техред Л. Сердюкова Корректор Л.Пилипенко