Формирователь сигналов считывания

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при создании полупроводниковых интегральных схем памяти. Цель изобретения - упрощение формирователя сигналов считывания и снижение потребляемой им мощности при сохранении высокого быстродействия при считывании информации с запоминающих ячеек. Формирователь содержит ключевые транзисторы, резисторы, стабилизирующий транзистор, усилительные транзисторы, разрядные щины. Снижение потребляемой мощности осуществляется за счет оптимизации уровня считываемого сигнала. 1 ил. оо ОС 01 ГчЭ

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1238152

Ai (21) 3779608/24-24 (22) 14.08.84 (46) 15.06.86. Бюл. № 22 (72) М. О. Ботвиник, М. П. Сахаров и А. С. Попель (53) 681.327(088.8) (56) Авторское свидетельство СССР

¹ 1113852, кл. G ll С 7/00, 28.11.84. (54) ФОРМИРОВАТЕЛЬ СИГНАЛОВ СЧИТЫВАНИЯ (57) Изобретение относится к области вычислительной техники и может быть использовано при создании полупроводниковых интегральных схем памяти. Цель изобретения — упрощение формирователя сигналов считывания и снижение потребляемой им мощности при сохранении высокого быстродействия при считывании информации с запоминающих ячеек. Формирователь содержит ключевые транзисторы, резисторы, стабилизирующий транзистор, усилительные транзисторы, разрядные шины. Снижение потребляемой мощности осуществляется за счет оптимизации уровня считываемого сигнала.

1 ил.

1238152

Изобр< тение относится к вычислительной технике и может быть испол?>зовано при создании полупроводниковых интегральных схем памяти. . Цельк) изобретения является упрогцение схемы и снижение потребляемой мощности при сохранении высокого быстродействия при считывании информации с запоминаю?цих ячеек.

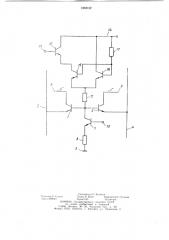

На чертеже представлена принципиальная схема формирователя сигналов считыва- 10 ния.

Формирователь содержит первый 1 и вто. рой 2 ключевые транзисторы, эмиттеры которых подключены к первой 3 и второй 4 разрядным шинам соответственно, а коллекторы являлися нулевым 5 и единичным 6 контрольными выходами формирователя, источник тока, состонп.ий из третьего кл)оченого транзистора 7 и I?cp!30I о резистора 8,, ин зынод ? о- рого подк ???Очен к общей

:I HHe 9, а >вто? ><??? — к эмиттеру третьего ключевого транзистора 7, база которого

»вляе? ся входом 10 для подключения исто«:? Нка опорного напряжения. Коллектор

H,.;!,>< >Io«eEl к перному выводу второго резисгорл I I, базы тран".èñòîðîâ I и 2 объе,.)Неllb! и подкл?о«е??и к коллектору. транзис- 25 тора 7, база стабилизирующего транзисто,>а 12 янляется управляющим входом 13 формирователя) коллектор его подключен к шине пчтания 14, а эмиттер соединен с коллектором первого усилительного транзистора

i,5".:-)ми т рь? и рното 15 и второго !6 усилительных транзисторов соединены и подключены к второму выводу резистора 11, кол leктор второго усилительного транзис. ора 16 подключен к шине питания 14, ре: !< тop 17 подключен одним выводом к шине

НI тания 14, а вторым -- к базам транзисторов !5 и 16.

Формирователь работает следующим образом.

При подаче»а управляющий вход 13 напряжения шины питания 14 транзистор 15 находит я на границе насыщения и его боль>и<>й ба:)оный ток вызы>)ает падение напряжения на резисторе 17, равное 11??»> =К., где И . - Ia! Ip«жение коллектор — эмиттер васыц>енного транзистора. Это происходит, так как контур база — эмиттер транзистора 4 ! 2, коллектор---:. м иттер транзистора 15 и контур база — эмиттер транзистора 16, резистор !7 включены параллельно, а падение

IIII;pHHм.

Таким образом, в точке соединения эмиттеров транзисторов 5 и !6 сформирован потенциал, равный Š— — Ȅ— И., где

F. -- Напряжение шины питания 15; Ȅ— напряжение на переходах база — -эмиттер транзисторов.

Для обеспечения оптимального уровня

Е: — 1,75И. на базах транзисторов и 2 недостающее падение потенциала, равное

0,75И„- И: «, формируется на резисторе 11 за счет протекания по нему гока источника тока на транзисторе 7 и резисторе 8 получающем опорное напряжение с гхода 10.

В результате один из транзисторов 1 или 2 открывается соответственно состоянию разрядных шин 3 и 4, и, таким опр"=,зом информация о состоянии разрядl)hl < шин 3 и 4 передаетсil Н3 контрольныс выходы 5 и 6.

Снижение напряжения на управляющем входе !3, моделирую?>?ем снижение потенциала строки за счет уменьшения коэффициента усиления транзисторов н диапазоне рабочих температур, изменения разброса коэффициента усиления в Texlloл>г???секо?)? и роцессе и изменения тока, прот<.каю?цего «ep,=з

cTpoH )) в ) и а вазоне ра>))о ??? х ? ем пеp 1Tvp, lleредается за счет изменения базового тока транзистора 15 на резистор !7 и изменяет потенциал точки соединения змиттеров трэн зисторов 15 и 16.

Уровень считывания пони>кается ?На такую же величину. что и управляю?ций вход

13 H ocTE> Tcsi оптима;?ь??ым с TO IHH эрен??я быстродействия при c«HTh!E)EIEI IH.

Формула изоб!>стен ш?

Формирователь сигналов с ?нтыв;)ния, содержа?!IHH первый, второй, третий кл?О)?е?3??< транзисторы, стабилизирук>ц;ий транзистор, первый и второй резисторы, приче"I змит теры первого и второго ключевы.х т?)Ннзисторов являются информ Iil<о?????.??? и >3ходами формирователя, ныходамн которого являотся коллекторы перного и второго к?.;o«

T p B 133 H C T0?? O B ) Од и Н !3 Ы ?3 од !? e?)?3 О Го p < 3?? от ора подключен к шинс .?улсвого ?От<«>IIHала, а другой вывод — - к эмиттеру третьего ключевого транзистора, база которого подключена к шине опорного напряжения, а коллектор — к одному выводу второго резистора, коллектор стабилизирую?цего транзистора соединен с шиной питания, а база является управляюгцим входом формирователя, <?тлича><?и<ийся тем, что, с цель?о упрощения формирователя и снижения потребляемой им мощности, в него введены первый и второй усилительные транзисторы и третий резистор, один вывод которого подключен к ц?ипе питания, а другой — — к базам усилительных транзисторов, эмиттеры которых соединены с другим выводом второго резистора, коллектор второго уси.пительного транзистора подключен к шине питания, коллектор первого усилительного транзистора соединен с al?HT!.ером стабилизирующего транзистора, базы первого и второго ключевых транзисторов подключены к коллектору третьего ключевого транзистора.

1238152

" Ъ

Редактор A. Гулько

Заказ 3298!53

Составите.1ь О. Кулаков

Техред И Берес Корректор О. II годная

Тираж 543 Подпис нос

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раугвская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проекзная, 4