Устройство для контроля блоков постоянной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано для контроля запоминающих устройств. Цель изобретения - повышение быстродействия устройства. Устройство содержит генератор импульсов, распределитель импульсов, блоки памяти, коммутатор данных, счетчики, блок сравнения, блок индикации, коммутатор адресов . Повышение быстродействия устройства достигается за счет последовательной работы блоков памяти, храняш,их эталонную информацию, и коммутации эталонных данных на блок сравнения, на который также поступает информация с блока контролируемой памяти. При этом количество блоков памяти равно отношению рабочей частоты контролируемого блока памяти к рабочей частоте каждого блока памяти, округленного до большего целого числа. I ил. ьэ со 00 О) ел

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„ЯЦ„„1238165 А1

ОПИСАНИЕ ИЗОБРЕ

К А BTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3807792/24-24 (22) 31.10.84 (46) 15.06.86. Бюл. № 22 (72) А. Я. Гладун, В. А. Исаенко, А. А. Самчинский и Б. Г. Шаров (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 607282, кл. G 11 С 29/00, 1976.

Авторское свидетельство СССР № 982097, кл. G 11 С 29/00, 1980. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ

БЛОКОВ ПОСТОЯННОЙ ПАМЯТИ (57) Изобретение относится к вычислительной технике и может быть использовано для контроля запоминающих устройств. Цель изобретения — повышение быстродействия устройства. Устройство содержит генератор импульсов, распределитель импульсов, блоки памяти, коммутатор данных, счетчики, блок сравнения, блок индикации, коммутатор адресов. Повышение быстродействия устройства достигается за счет последовательной работы блоков памяти, хранящих эталонную информацию, и коммутации эталонных данных на блок сравнения, на который также поступает информация с блока контролируемой памяти. При этом количество блоков памяти равно отношению рабочей частоты контролируемого блока памяти к рабочей частоте каждого блока памяти, округленного до большего целого числа. 1 ил.

1238165

Изобретение относится к вычислительной технике и может быть использовано для контроля запоминающих устройств.

Цель изобретения — повышение быстродействия устройства.

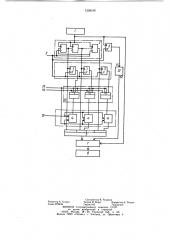

На чертеже представлена структурная схема предложенного устройства.

Устройство содержит генератор 1 импульсов, распределитель 2 импульсов, группу счетчиков 3, блоки 4 памяти, коммутатор 5 данных, счетчик 6, блок 7 сравнения, блок 8 индикации, первый управляющий вход 9 устройства, коммутатор 10 адресов, К выходу

11 и входу 12 устройства подключается блок 13 контролируемой памяти. К адресному 14, второму управляющему 15 и информационному входу 16 подключается управляющая ЭВМ (не показана).

Генератор 1 импульсов предназначен для формирования последовательности синхроимпульсов, частота следования которых равна предельной рабочей частоте блока 13.

Распределитель 2 импульсов, блок 4 предназначены для хранения информации, соответствующей блоку 13.

Коммутатор 10 предназначен для селекции адресов, поступающих на вход блоков 4 в зависимости от сигналов на входу 15, либо из счетчиков 3, либо по адресному входу 14.

Устройство работает следующим образом.

Перед началом контроля блока 13 производится запись информации, соответствующей блоку 13 в блоки 4, причем по нулевому адресу первого блока 4 записана информация, соответствующая информации по нулевому адресу блока 13, по нулевому адресу второго блока 4 записана информация, соответствующая информации по первому адресу блока 13 и т. д., по нулевому адресу К-го блока 4 записана информация по

К-ому адресу блока 13, по первому адресу первого блока 4 записана информация, соответствующая информации по (К + 1) -му адресу блока 13 и т. д. (К вЂ” число блоков 4).

Количество К блоков 4 равно отношению рабочей частоты блока 13 памяти к рабочей частоте каждого блока 4, округленного до большего целого.

Запись информации в блоки 4 производится с помощью управляющей ЭВМ, при этом на вход 15 поступает сигнал, переводящий блоки 4 в режим записи и подключающий вход 14 к адресным входам блоков 4, а на входе 16 устройства появляется информация, записываемая в блоки 4.

После окончания записи по входу 9 происходит сигнал, устанавливающий счетчики

3 и 6, а также триггер 14 распределителя 2 за исключением первого в нулевое состояние. Первый триггер при этом устанавливается в единичное состояние.

На входах блоков 4 устанавливаются нулевые адреса.

С выхода коммутатора 5 на вход блока 7 сравнения поступает информация, считанная по нулевому адресу из первого блока 4. На другой вход блока 7 поступает информация, считанная по нулевому адресу контролируемого блока 13.

При поступлении импульса из генератора

1 на разрешающий вход блока 7 происходит сравнение информации с выдачей результата сравнения в блок 8 индикации.

По заднему фронту этого импульса происходит модификация счетчика 6, сдвиг импульса в распределитель 2. По заднему фронту импульсов, формируемых с помощью распределителя 2, происходит модификация одного из счетчиков 3.

Таким образом, к моменту прихода следующего импульса из генератора 1 с выхода коммутатора 5 на вход блока 7 поступает информация, считанная по йулевому адресу из второго блока 4. На другой вход блока 7

20 поступает информация, считанная по первому адресу контролируемого блока памяти.

При поступлении импульса из генератора 1 на разрешающий вход блока 7 происходит сравнение с выдачей результата в блок 8.

Аналогично происходит сравнение информа ции по всем остальным адресам контрол и руе мого блока 13.

Формула изобретения

Устройство для контроля блоков постоянной памяти, содержащее генератор импульсов, счетчик, блок памяти, коммутатор ад30 ресов, блок сравнения и блок индикации, причем выход генератора импульсов подключен к разрешающему входу блока сравнения и счетному входу счетчика, выход которого является адресным выходом устройства, один из информационных входов блока сравнения является первым информационным входом устройства, выход блока сравнения подключен к входу блока индикации, один из адресных входов коммутатора адресов является адресным входом устройства, 40 управляющие входы коммутатора адреса и блоков памяти являются вторым информационным входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены группа счетчиков, коммутатор данных и распределитель импульсов, вход которого подключен к выходу генератора импульсов, выходы соединены с счетными входами счетчиков группы, управляющие входы которых и управляющие входы распределителя импульсов и счетчика являются управляющим входом устройства, выходы счетчиков группы подключены к другим адрс"ным входам коммутатора адресов, выходы которого подключены к входам блоков памяти, выходы которых соединены с информационными вхо5у дами коммутатора данных, управляющие входы которого подключены к выходам распределителя импульсов, а выход соединен с другим информационным входом блока сравнения.

74Составитель В. Рудаков

Редактор А. Гулько Техред И. Верес Корректор Е. Рошко

Заказ 3299/54 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», r. Ужгород, ул. Проектная, 4