Преобразователь модулярного кода в двоичный код

Иллюстрации

Показать всеРеферат

Изобретение предназначено для применения в устройствах обработки информации, представленн.ой в виде вьгчетов в системе остаточных классов . Цель изобретения - расширение функциональных возможностей путем обессмены системы -оснований в процес.се работы. Преобразователь содержит блок 1 хранения констант, блок 2 перемножения, два мультиплек .сора 3, 4, накапливающий сумматор 5, формирователь 6 импульсов, элемент 7 эквивалентности, счетчик 8, два элемента 9, 10 ЗАПРЕТ, элемент 11 И, элемент 12 задержки и RS-триггер 13. Выбор системы оснований производится подачей на входы блока 1 соответствующего кода. Каждый вычет умножается в блоке 2 на соответствующий ортонормированный базис и суммируется с содержимым сумматора 5-, Если сумматор 5 не переполняется, то содержи-, мое счетчика 8 увеличивается на единицу и на блок 2 поступает нозая пара сомножителей. При переполнении сумматора 5 формирователь 6 закроет элемент 9, останавливая счетчик 8, и переключит на входы сумматора 5 код дополнения диапазона данной системы оснований. Когда счетчик 8 досчитает до чирла оснований данной сиетемы, элёме нт ,/ эквивалентности .остановит работу преобразователя . 1 ил, 2 табл. (Л С ч % Mk Ч S СО 00 to 4 NU

„„SU„„12 82 4.СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (51)4 Н 03 М 7/18

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ., "в„„.",","" /

К АВТОРСКОМ У СВИДЕТЕЛЬСТВУ (21) 3810164/24-24 (22) 05,1 1.84 (46) 15.06.86. Бюл. ¹ .22 (72) К.М.. Сагдеев, С.Н. Хлевной и Н.И. Швецов (53) 681.325(088.8) (56) Авторское свидетельство СССР

¹.605209, кл. G 06 F 5/02, 1977. .Авторское свидетельство СССР № 924695, кл. G 06 F 5/02, !980. (54) ПРЕОБРАЗОВАТЕЛЬ МОДУЛЯРНОГО КОДА В ДВОИЧНЫЙ КОД (57) Изобретение предназначено для применения в устройствах обработки информации, представленной в виде .вычетов в системе остаточных классов .

Цель изобретения — расширение функциональных возможностей путем обеспечения смены системы оснований в процессе работы. Преобразователь содержит блок 1 хранения констант, блок 2 перемножения, два мультиплексора 3, 4, накапливающий сумматор 5, 1 формирователь 6 импульсов, элемент 7 эквивалентности, счетчик 8, два элемента 9, 10 ЗАПРЕТ, элемент II И, элемент 12 задержки и RS-триггер 13.

Выбор системы оснований производится подачей на входы блока 1 соответст.— вующего кода. Каждый вычет умножается в блоке 2 на соответствующий ортонормированный базис и суммируется с содержимым сумматора 5. Если сумматор 5 не переполняется, то содержи-. мое счетчика 8 увеличивается на единицу и на блок 2 поступает новая пара сомножителей. При переполнении сумматора 5 формирователь 6 закроет элемент 9, останавливая счетчик 8, и переключит на входы сумматора 5 код дополнения диапазона данной системы оснований, Когда счетчик 8 досчитает до числа оснований даннойсис- темы, элемент 7 эквивалентности остановит работу преобразователя . 1 ил, 2 табл.

1238244

Изобретение относится к вычислительной технике и может быть применено при создании устройств обработки информации, использующих представление чисел в.системе остаточных классов (модулярные коды).

Цель изобретения — расширение функциональных возможностей путем обеспечения смены системы оснований в роцессе работы.

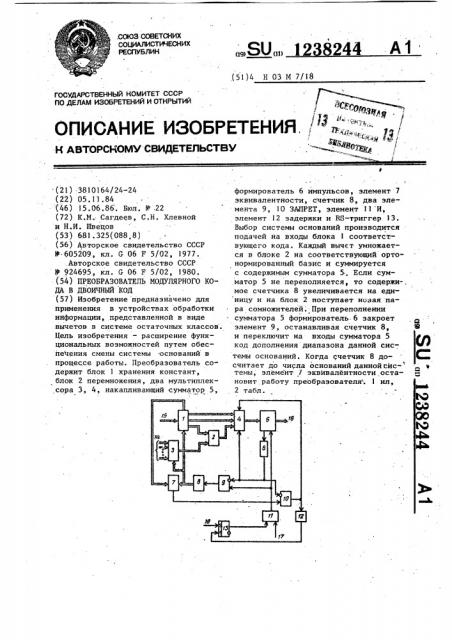

На чертеже представлена функциональная схема преобразователя.

Преобразователь модулярного кода в двоичный код содержит блок .1 хранения констант, блок 2 перемножения, первый-и второй мультиплексоры 3 и 4, накапливающий сумматор 5, формирователь 6 импульсов, элемент 7 эквивалентности, счетчик 8, первый У и второй 10 элементы ЗАПРЕТ, элемент

ll И, элемент !2 задержки и RS-триггер 13. Входы первого мультиплексора 3 являются соответствующими входными шинами 14 устройства, а входы блока 1 хранения констант являются шиной 15 управления устройства. Первые выходы блока 1 подключены к первым входам блока 2 перемножения, вторые входы которого соединены с . соответствующими выходами первого мультиплексора 3, а выходы — с первыми входами второго мультиплексора 4, вторые и третьи входы которого подключены к вторым и третьим выходам блока 1 соответственно. Выходы второго мультиплексора 4 соединены с входами накапливающего сумматора 5, выходы которого являются выходной шиной. 16 устройства, выход переполнения накапливающего сумматора 5 соединен с входом формирователя 6 импульсов, .а вход синхронизации обье-. динен с разрешающим входом первого . элемента ЗАПРЕТ 9 и подключен к выходу элемента !.1 И., один вход которого является тактовым входом 17 устройства, а другой подключен к выходу

RS-триггера 13, $-вход которого является входом 18 запуска устройства, à -R-вход соединен с выходом элемента 12 задержки. Выход формирователя 6 импульсов подключен к первому управляющему входу второго мультиплексора 4 и запрещающим входам элементов 9 и 10 ЗАПРЕТ. Выход элемента 9 соединен с входом счетчика 8, выходы которого подключены к первым входам элемента 7 эквивалентности, управляющим входам первого

Ю мультиплексора 3 и адресным входам блока 1 хранения койстайт, четвертые выходы которого соединены с вторыми входами элемента 7 эквивалентности, 5 выход которого подключен к разрешающему входу второго элемента 10 3АПРЕТ, выход которого соединен с вторым управляющим входом второго мультиплексора 4 и входом элемента 12 задержки.

В основе преобразователя лежат следующие соотношения.Преобразование числа А ведется по формуле

А= м; В;!р, (!) . l -а -1 где r; — число добавлений Р, которое .выполняется до тех пор, пока не выполнится условие !... ! 3, Б, +Р! +P „+.;, +Pl <М, что означает отсутствие переполнения сумматора по модулю М.

Поскольку (d.;,В,.+г; Р)I ) >P

i "-1 на величину Р, то для получения А<Р

45 в (2) необходимо прибавлять Р по модулю М, что эквивалентно вычитанию дополнения Р..

1

Блок 1 хранения констант может быть выполнен на постоянном запоми нающем устройстве, в котором записаны коды совокупности констант (ортонормированных векторов В;, диапазона

P представления чисел, дополнения Р

5 диапазона и числа и оснований систе мы) для М систем оснований модулярной арифметики. Выбор системы оснований определяется кодом номера системы где ct. — вычет числа А по основа-. ! нирю g, .И, = .- - =1(mod.Я ) — ортонормиро1

20 ванный вектор, являющийся константой для выбранной системы оснований;

P = П P; — диапазон представления

1=1 чисел, перекрываемый системой основа ний P

Известно, что если есть модуль

М>Р, то любое число С можно преобфал зовать как I Clр = !С+Р1,„, если С>Р, 30 где Р=М-P - дополнение диапазона P до модуля M. С учетом этого выражение (1)„мржно представить как

+г P)J„1„+Pl„(2). !

1238244 управления устройства. Блок 1 хранения констант имеет 4 группы выходов „ первые — выходы выдачи кодов ортонормированных векторов В, вторые — диаФ пазона Р представления чисел, треТаблица 1

-г

Выходы

Адресные входы

1 2 3 4 г ) О

В1Х п, ° 4

Р, Р, и, и-1

P P u

О в

P P u а,iaaf

Р P n х и-1

° °

° ° °

° ° ° ° ° 4 °

ЄЄ

N i

I ° ° °

Блок 2 перемножения выполнен в виде комбинационной схемы. Первый мультиплексор 3 изменяет состояние своих выходов НрН изменении HR единицу кода 45 на управляющих входах. Второй мультиплексор 4 имеет следующую таблицу. переключений (табл. 2).

Таблица 2

Коммутируемые входы

55. 0

Величина кода на входах управления тьи — дополнения . Р диапазона Р, четвертые — числа и оснований.

Таблица истинности блока 1 хранения констант имеет вид (табл. 1).

Накапливающий сумматор 5 имеет разрядность jlog М С где И-модуль сумматора, равный М=макс (,В; =макс Ы;гг п Ц

Р1

Длительность импульса, генерируемого формирователем 6, немного превышает период следования тактовых импульсов на входе 17. Элемент 7 эквивалентности выдает на выход единичный сигнал.при равенстве кодов на входах.

Элемечт 12 имеет задержку на один такт.

Преобразователь модулярного кода в двоичный код работает следующим образом.

В исходном состоянии триггер 13 находится в нулевом состоянии, за1238244 прещая ещая прохождение тактовых импуль5 сов через элемент 11 И. В сумматор по шине начальной установки (на чертеже не показана) записан код дополФЪ нения диапазона P. По шинам 14 поступает коды вычетов cx,,...,о „. На шину 15 управления подан код, которыи для определенной системы оснований модулярного кода определяет совокуп- 10 ности констант, записанных в блоке 1 хранения кОнстант: ортонормированных векторов В;, диапазона Р, дополнения

Р диапазона, числа и оснований.

Счетчик 8.обнулен, что обеспечива- 15 ет коммутацию первых входов мультиплексоров .3 на его выходы, т.е. на вторые входы блока 2 перемножения поступает код вычета Ы„ . Эти же нулевые потенциалы со счетчика 8, посту- 20 пая на адресные входы блока 1 хранения констант, являются адресом к ортонормированному вектору В, . В результате на первых входах блока 2 перемножения появится код В„, а на 5

25 еro выходах через время, равное вре-, мени установления переходных процессов, установится код величины ы„ В„, который поступает на первые входы. мультиплексора 4, на его второй и 30 третий входы с блока .1 хранения констант соответственно поступают коды

PиР.

Поскольку на выходе. переполнения

35 .сумматора 5, а следовательно, и на выходе формирователя 6 импульсов потенциал "0"; .то на оба входа управления мультиплексора 4 будут посту1I t l пать потенциалы логических 0, что соответствует коммутации первых входов мультиплексора 4 к выходам. Следовательно, на информационные входы сумматора 5 поступает код величины В . С четвертых выходов блока 1

11 хранения констант на вторые входы элемента 7 эквивалентности поступает код числа п оснований.

С приходом на шину 18 запуска устройства запускающего импульса RS50 триггер 13 устанавливается в единичное состояние, разрешая прохождение тактовым импульсам через элемент 11

И. Первый тактовый импульс увеличит содержимое сумматора 5 a d, В, и увеличит состояние счетчика 8 на еди55 ницу. Это приведет к подключению вторых входов мультиплексора 3 к выходам и выбору другого ортонормированного вектора В в блоке 1 хранения констант, т.е. на выходах 2 .перемножения установится код величины с(В .

Если в результате сложения в""Сумматоре 5 не произошло переполнения, т.е. Р+ Ы В, М, или иначе cC„ B„(P, то мультиплексор 4 останется в предыдущем состоянии и на информационные входы сумматора 5 поступит код величины 4 В, который на следующем такте опять увеличит значение кода, записанного в сумматоре 5. Если в результате сложения в .сумматоре 5 появится импульс переполнения, это

I означает, что Р+М,В1)М, илии, В1)Р.

Тогда формирователь 6 импульсов генерирует суммарный импульс, длина которого определяется количеством импульсов переполнения, т.е. до тех пор, пока величина в сумматоре 5 превышает его модуль M. Этот импульс запрещает прохождение следующих тактовых импульсов через элемент 7 (изменения . состояния счетчика 8 не произойдет) и скоммутирует вторые входы мульти-! плексора 4 на его выходы, таким образом на входы сумматора 5 поступает код Р. Последующие тактовые импульсы будут суммировать эту величину к содержимому сумматора до тех пор, пока величина суммы не будет приведена к разрядности сумматора 5, т.е.

1l Р+Ы В I„+Pl„+ +P)„

Следовательно, мультиплексор. 4 вернется в исходное состояние и будет подавать на информационные входы сумматора 5 код величины ы В

Далее процесс преобразования совершается аналогичным образом . Как только в сумматор 5 добавится код, o(B т.е. в счетчике 8 установится и> код числа и оснований, на выходе элемента 7 эквивалентностй появится потенциал логической "1", Если при этом будет отсутствовать сигнал переполнения в сумматоре 5, т.е. установится величина

l .: (оС:, В +г ) м I é =А+РОМ, 1 то на выходе элемента 10 появится импульс "1" (так .как на выходе формирователя 6 импульсов "0"), который подключает третьи входы мультиплексора 4 на его выходы. На входы сумматора 5 поступает код диапазона

P и защелкивается там.

1238244 формула изобретения держки с R-входом RS-триггера.

Составитель О, Ревинский

Техред М.Ходанич Корректор Т. Колб

Редактор М. Товтин

Заказ 3304/58 Тираж 816 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

Импульс с выхода, элемента 10, задержанный на один такт в элементе 12 задержки, чтобы произошло изменение состояния сумматора 5, поступает на

R вход Rs-триггера.13 и сбрасывает

его в нулевое .состояние„ запрещая прохождение тактовых импульсов. На этом работа устройства заканчивается, на шине 16 будет двоичный код числа А.

При необходимости оперативной смены оснований модулярного кода в процессе работы устройства на шину 15 управления подается код, определяющий номер нужной системы оснований, а на входные шины — коды вычетов, соответствующие данной системе оснований.

Объем памяти блока хранения констант определяется как

Q=Nf(n+2)m+Cj, где N — - количество используемых систем оснований; и — число оснований;

Г rn;P1 <=.)l<8 « / (— число двоичных разрядов, необходимых для записи В,, Р, Р; . с = jlog n f — число двоичных разрядов, определяемых числом оснований и.

Преобразователь модулярного кода в двоичный код, содержащий блок хракения констант, счетчик, накапливающий сумматор, элемент И и RS-триггер, S-вход которого является входом запуска преобразователя, прямой выход подключен к первому входу элемента И, второй вход которого является тактовым входом преобразователя,. а выход подключен к входу синхронизации на- капливающего сумматора, выходы которого являются выходной шиной преобразователя, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения смены системы оснований в процессе работы, в него введены первый и второй мультиплексоры, формирователь импульсов, элемент эквивалентности, первый и второй элементы ЗА10 ПРЕТ, элемент задержки,и блок перемножения, первые входы которого соединены .с соответствующими первыми выходами блока хранения констант, а вторые входы подключены к выходам первого мультиплексора, входы которого являются соответствующими входными шинами преобразователя,. а управляющие входы объединены с адресными входами блока хранения констант и

20 первыми входами элемента эквивалент-ности и подключены к соответствующим выходам счетчика, вход которого соединен с выходом первого элемента ЗАПРЕТ, разрешающий вход которого сое25 динен с выходом элемента И, запрещаю1щий вход объединен с запрещающим входом второго элемента ЗАПРЕТ и,первым управляющим входом второго мультиплексора и подключен к выходу формирователя импульсов, вход которого соединен с выходом переполнения накапливающего сумматора, входы которого подключены к соответствующим выходам второго мультиплЕксора, первые входы которого соединены с выходами блока перемножения, вторые и третьи входы второго. мультиплексора подключены к вторым и третьим выходам блока хранения констант, четвертые выходы которого соединены с вторыми входами элемента эквивалентности, выход которого подключен к разрешающему входу второго элемента

ЗАПРЕТ, выход которого соединен с вторым управляющим входом второго

45 мультиплексора и через элемент за-.