Многоканальное устройство для приоритетного подключения абонентов к общей магистрали

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть применено в многонашинных и многопроцессорных вычислительных системах, использзпощих для обмена данными общую магистраль . Целью изобретения является расширение функциональных возможностей за счет динамического определения приоритетов запросов внутри каждого канала. Цель достигается путем изменения схемы каналоввведением в каждый канал дополннтельно двух триггеров, формирователя импульсов , элемента 1-ШИ, элемента И и блока задержки, соединенных соответственно с другими узлами и элементами устройства. Кроме того, блок задержки имеет характерное для данного устройства схемное вьшолнение. 1 з.п.- ф-лы, 2 ил. I СО 1О со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

Р1=,СПУБЛИН

„„SU„„1239717 дц G 06 Р 9/46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАИ:ТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ. ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3790712/24-24 (22) 15.09.84 ° (46) 23.06.86. Бюл. Ф 23 (72) В.В.Туравинин, В.М.Неффа, А.N.Ñíàäèí и С.М.Корнилов (53) 681.325(088.8) (56) Авторское свидетельство СССР

9 860073, кл. G 06 F 9/46, 1981. Авторское свидетельство СССР

Р 798839, кл. G 06 F 9/46, 1981, (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ . ПРИОРИТЕТНОГО ПОДКЛН)ЧЕНИЯ АБОНЕНТОВ

К ОБЩЕЙ МАГИСТРАЛИ (57) Изобретение относится к области вычислительной техники и может быть применено в многомашинных и многопроцессорных вы ислительных системах, использующих для обмена данными общую магистраль.. Целью изобретения является расширение функциональных возможностей за счет динамического определения приоритетов запросов внутри каждого канала. Цель достигается путем изменения схемы каналов.—

/ введением в каждый канал дополнитель- но двух триггеров, формирователя импульсов, элемента ИЛИ, элемента И и блока задержки, соединенных соответственно с другими узлами и элементами устройства. Кроме того, блок задержки имеет характерное для данного устройства схемнае выполнение. 1 з.п.- Ж ф-лы, 2 ил. ничное состояние, закрывая при этом через формирователь 20 импульсов эле— менты И 13 всех каналов 3. Этот же сигнал через элемент ИЛИ 15 устанавливает триггер 6 в единичное состояние, изменяя при этом через формирователь 4 импульсов состояние шины 1.

Через время задержки элемента 5 срабатывает элемент И 10, сигнал с его выхода устанавливает триггер 8 в единичное состояние, а триггер 6 через элемент ИЛИ 14 в нулевое состояние.

На шине 1 через формирователь 4 импульсов устанавливается сигнал логи— ческой единицы, что приводит к появлению единичного сигнала на выходе элемента И 11, который поступает на вход блока 21. Поскольку на регистрах 22 блоков 21 различных каналов 3 установлены различные коды, то сигналы на вьгходах блоков 21 различных каналов 3 появляются в различное время (тем раньше, чем выше приоритет процессора, подключенного к данному каналу). Так, например, для четырехпроцессорной вычислительной системы коды приоритетов процессоров должны иметь следующий вид: 111, 011,001,000 (кодь::: записаны в порядке возрастания приоритета). Если, например, в данное время на общую магистраль претендуют два процессора, имеющие первый и второй приоритеты, т.е. их коды приоритетов соответственно равны 000 и 00), то после поступления сигнала на вход блока 21, на регистре 22 которого установлен код 000, на выходе блока. 21 появляется единичный сигнал через время задержки сигнала на од1 12397)7

Изобретение относится к вычислительной технике и может быть применено в многомашинных и многопроцессорных вычислительных системах, использующих для обмена данными общую магистраль.

Цель изобретения — расширение функциональных возможностей за счет динамического определения приоритетов запросов внутри каждого канала. 10

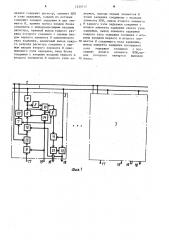

На фиг.! изображена структурная схема устройства; на фиг.2 — структурная схема блока задержки (пример для трехразрядного кода).

Устройство содержит шину 1 разре- 15 шения, шину 2 запрещения, каналы 3, каждый из которьгх содержит формирователь 4 импульсов, элемент 5 задержки, триггеры 6-9, элементы И 10-13, элементы ИЛИ 14 и 15, группу кодовых 20 входов 16 устройства, запросный вход

17 устройства, сигнальный выход 18 устройства, вход 19 конца обслуживания устройства, формирователь 20 им- пульсов, блок 2) задержки, содержащий (фиг.2) регистр 22, элемент

ИЛИ 23, узлы 24 задержки (по количеству разрядов регистра), каждый из которых содержит элементы И 25 и 26 и элемент 27 задержки. 3Р

Устройство работает следующим образом, В исходном состоянии на регистры

22 от соответствующих источников информации (например, процессоров) через соответствующие группы входов 16 парафазным кодом заносятся коды приоритетов процессоров, которые не могут быть одинаковыми, но при настройке вьгчислительной системы могут оперативно изменяться, триггеры 6-9 чаходятся в нулевом состоянии, на шинах 2 и 1 установлен сигнал логической единицы, В случайные моменты времени процессоры по мере необходимости передачи сообщений другим процес- . сорам выдают на соответствующие входы 17 сигналы, устанавливающие триггеры 9 соответствующих каналов 3 в единичное состояние (процессоры и общая магистраль на фиг.) не показаны).

Рассмотрим работу одного из каналов 3, так как в остальных каналах работа осуществляется аналогичным образом. Сигнал с единичного выхода триггера 9 через открытый элемент

И 13 устанавливает триггер 7 в едином логическом элементе И нли ИЛИ, которое обусловлено задержкой постулившего сигнала на элементе И 25 и элементе ИЛИ 23 этого блока 21. На выходе же блока 21, на регистре 22 которого установлен код 00!, появляется сигнал через время, обусловленное прохождением сигнала, поступающего на вход блока 21 через элементы: И 26, задержки 27 узла 244, эле-. мент И 25 узла 24д и элемент ИЛИ 23 данного блока 21. После появления сигнала на выходе блока 21, имеющего максимальный приоритет, срабатывает элемент И 12 канала 3, к которому подключен наиболее приоритетный процессор и через выход 18 этому процессору выдается сигнал, уведомляющий его о том, что общая магистраль им

1239717 захвачена и он может передавать по ней информацию. Этот же сигнал через элемент ИЛИ 15 рассматриваемого канала 3 переводит триггер в единичное состояние, устанавливая тем самым через формирователь 4 импульсов нулевой сигнал на шине 1 и закрывая таким образом элементы И 12 всех каналов 3. Для надежной работы устройства время задержки элементов 27 долж- !О но быть не меньше шести логических элементов. В этом случае к моменту . выдачи сигнала с выхода блока 21, на регистре 22 которого установлен код

001, элемент И 12 закрыт и процессор !5 с вторым приоритетом продолжает вы полнение текущей программы. Доступ к общей магистрали он может получить после того, как процессор с первым приоритетом заканчивает передачу ин- 20 формации и выдает на вход 19 своего канала 3 сигнал, устанавливающий триггеры 6-9 этого канала в нулевое состояние. Так как на шине 1 появляется единичный сигнал, то в канале 3, 25 к которому подключен процессор с первым приоритетом, на выходе элемента

И 11 возникает сигнал, который появляется на выходе элемента ИЛИ 23 и через элемент И 12 и выход 18 разре- gO шает этому процессору занять общую магистраль. Если запросы от процессоров по соответствующим входам 17 поступают в то время, когда магистраль занята, то они фиксируются на триггерах 9 соответствующих каналов 3 и после освобождения магистрали наиболее приоритетный процессор в результате работы каналов 3, аналогичной описанной вышее, получает доступ к ма- до гистрали. Для того, чтобы процессоры с низшими приоритетами не ожидали предоставления им магистрали бесконечно долго при интенсивных потоках запросов на магистраль от процессоров с.высокими приоритетами, необхо— димо выбрать соответствующим образом время задержки элементов 5.

Формула изобретения 5О о

1. Многоканальное устройство для приоритетного подключения абонентов к общей магистрали, содержащее в каждом канале первый формирователь им- 55 пульсов, три элемента И, первый элемент ИЛИ, элемент задержки и два триггера, причем единичный вход первого триггера соединен с выходом первого элемента И, выход первого триггера соединен с входом первого формирователя импульсов, выход которого соединен с шиной запрета общей магистрали устройства, выход первого элемента ИЛИ -соединен с входом сброса второго триггера, о т л и ч а ющ е е с я тем, что, с целью расширения функциональных возможностей за счет динамического определения приоритетов запросов внутри каждого канала, в каждый канал введены третий и четвертый триггеры, второй формирователь импульсов, второй элемент ИЛИ, четвертый элемент И и блок задержки, причем каждая группа кодовых входов устройства соединена С группой входов блока задержки одноименного канала, каждый запросный вход устройства со— единен с единичным входом третьего триггера одноименного канала, каждый сигнальный выход устройства соединен с выходом второго элемента И одноименного канала, каждый вход конца обслуживания устройства сдединен в одноименном канале с первым входом первого элемента ИЛИ и с входами сброса первого, третьего и четверто— го триггеров, прямой выход четвертого триггера соединен с первым входом третьего элемента И, второй вход и выход которого соединены соответственно с шиной разрешения общей магистрали устройства и с входом блока задержки, выход которого соединен с первым входом второго элемента И, второй вход которого соединен с шиной разрешения общей магистрали, выходы первого и второго элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с единичным входом второго триггера, выход которого соединен с первым входом четвертого элемента И, через элемент задержки — с вторым входом четвертого элемента И и с входом второго формирователя импульсов, выход которого соединен с шиной разрешения общей магистрали устройства, второй вход первого элемента ИЛИ соединен с выходом четвертого элемента И и с еди,ничным входом четвертого триггера, инверсный выход которого соединен с третьим выходомчетвертого злементаИ.

2. Устройство по п.1, о т л и - ч а ю щ е е с я тем, что блок задержки содержит регистр, элемент ИЛИ и узлы задержки, каждый из которых . содержит элемент задержки и два элемента И, причем группа входов блока соединена с информационными входами регистра, нулевой выход каждого разряда которого соединен с первым входом первого элемента И одноименного узла задержки, единичный выход каждо- 1О

ro разряда регистра соединен с первым входом второго элемента И одноименного узла задержки, вход блока соединен с вторыми входами первого и второго элементов И первого узла за- 15 держки, выходы первых элементов И узлов задержки соединены с входами элемента ИЛИ, выход второго элемента

И каждого узла задержки соединен с входом элемента задержки своего узла задержки„ выход элемента задержки каждого узла задержки соединен с вторыми входами первого и второго элементов И следующегс узла задержки, выход элемента задержки последнего узла задержки соединен с последним входсм элемента ИЛИ,выход которого является выходом блока.

1239717

Составитель М.Кудряшев

Техред lJ.Îëåéíèê Корректор E.Ðoøêo

Редактор Е.Папп

Заказ 3397/49 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4