Кодирующее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и системах для формирования контрольных кодовых комбинаций,предназначенных для обнаружения ошибок в информации, хранимой во внешней памяти ЭВМ, а также в технике связи для помехоустойчивого кодирования информации в каналах связи с использованием циклических кодов, С целью повышения быстродействия кодирующего устройства путем последовательно-параллельной обработки информации в кодирующее устройство, содержащее h -разрядный регистр сдвига, где - степень порождающего полинома, Ц сумматоров по модулю два, где К - число информационных разрядов порождающего полинома, введены () сумматоров по модулю два и запоминающее устройс тво, а ь -разрядный регистр разбит на rr vifvn -разрядных регистров сдвига. На вход устройства параллельно группам и по n-v бит подается кодовая последовательность , для которой необходимо сформировать проверочный код. Одно- . вреь-генно с подачей на вход очередной кодовой группы производится сдвиг информации во всех регистрах на 1 разряд и считывание информации из запоминающего устройства по адресу , код которого представляет собой совокупность битов, содержащихся в последних разрядах всех регистров сдвига и в К. предьщущих разрядах регистров сдвига. Информация, считанная из запоминающего устройства, суммируется с входной в сумматорах по модулю два. 2 ил, 2 табл. to оо () 00 а 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (1glSU(lI) 1 2 9 8 (П 4 Н 03 М 13/02 // G 06 Р 11/26 (21) 3654437/24-24 (22) 18 ° 10.83 (46) 23.06.86. Бюл. Ф 23 (72) Б ° С ° Березкин, IO Ф. Ратников, И.Н. Филиппов, В,П. Константинов и Г,П. Ситников (53) 621.376.56 (088.8) (56) Патент США В 3.859.630Ä кл. 340-146.1 опублик. 07.01.75.

Питерсон У., Уэлдон Э. Коды, исправляющие ошибки. М.: Мир, с. 223, рис. 7-19. (54) КОДИРУЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и мажет быть использована в вычислительных машинах и системах для формирования контрольных кодовых комбинаций, предназначенных для обнаружения ошибок в информации, хранимой во внешней памяти ЭВМ, а также в технике связи для помехоустойчивого кодирования информации в каналах связи с ис пользованием циклических кодов. С целью повышения быстродействия кодирующего устройства путем последовагельно-параллельной обработки информации в кодирующее устройство, содержащее h -разрядный регистр сдвига, где (— степень порождающего полинома, g сумматоров по модулю два, где К вЂ” число информационных разрядов порождающего полинома, введены (tw-К) сумматоров по модулю два и запоминающее устройство, а h --разрядный регистр разбит на (tg -pasрядных регистров сдвига. На вход устройства параллельно группам и по, бит подается кодовая последовательность, для которой необходимо сформировать проверочный кад. Одновременно с подачей на вход очередной кодовой группы производится сдвиг информации во всех регистрах на t разряд и считывание информации из запоминающего устройства по адресу, код которого представляет сОбой совокупность битов, содержащихся в последних разрядах всех регистров сдвига и в К предыдущих разрядах регистров сдвига. Информация, считанная из запоминающего устройства, суммируется с входной в сумматорах па модулю два. 2 ил, 2 табл.

Изобретение относится к вычислительной технике и может быть использовано в вычислительных машинах и системах для формирования контрольных кодовых комбинаций, предназначенных для обнаружения ошибок в информации, хранимой во внешней памяти ЭВМ, а также в технике связи для помехоустойчивого кодирования инфор.мации в каналах связи с использованием циклических кодов.

Цель изобретения — повышение быстродействия кодирующего устройства путем последовательно-параллельной обра.ботки информации.

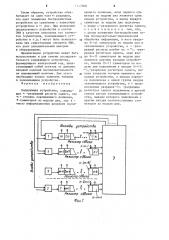

На фиг.1 приведена блок-схема кацирующего устройства, предна.значенного для формирования проверочных разрядов, циклического кода, образуеи-К мого полиномом вида X +... + х +1, на фиг.2 — принципиальная схема устройства, предназначенного для формирования проверочных разрядов циклического кода, образуемого полиномом вида 1 + х +l

Устройство содержит ll сумматоров

1 по модулю два, » »/„„ -разрядных регистров 2 сдвига, запоминающее устройство 3 (ЗУ выполнено в виде программируемой логической матрицы, фиг.2), триггеры 4, элементы И 5, диодные сборки 6 (элемент ИЛИ)..

Устройство работает следующим образом.

На вход устройства параллельно группам по w бит цддается кодовая последовательность, для которой требуется сформировать проверочный код.

Одновременно с подачей на вход очередной кодовой группы производится сдвиг информации по всех регистрах на один разряд и считывание информации из запоминающего устройства по адресу, код которого прецставляет собой совокупность битов, содержащихся в последних разрядах всех. регистров сдвига и в К предыдущих разрядах регистров сдвига. При этом информация, считанная из запоминающего устройства, поступает на вторые входы сумматоров и суммируется по модулю два с информацией, поступившей на вход устройства. Полученная сумма поступает в первые разряды регистров сдвига. Затем на вход устройства подается следующая кодовая группа и все повторяется.

В результате обработки разрядов входной последовательности в первые разрядов регистра сдвига помещена поразрядная сумма по модулю два битов входной последовательности с соответствующими битами, поступаюпими из цепи обратной связи, которые

1Î являются функцией -к последних битов регистра сдвига. В устройстве эта функция определяется за один такт с помощью таблицы, хранимой в запоминающем устройстве.

15 В запоминающем устройстве З,которое может быть как оперативным, так и постоянным, так как в нем постоянно хранится одна и та же информация, помещается таблица, сос1-»+ К

20 тоящая из 2 строк, каждая из ко" торых представляет собой,w -разрядный кодовый вектор, после » тактов его работы, если перед началом его работы в последние »+ разрядов

25 известного устройства был помещен адрес (аргумент) данной строки таблицы. Значение строки таблицы с адресом Z L Х,, может быть определено по формуле

ЗО п Ф I(У, =) z а„„„(ood ) где . j; — значение координаты вектора-строки таблицы

L . — значение координаты вектора-адреса (аргумента) строки,, значение коэффициента

h 4+1 порождающего полинома.

В качестве примера приведена табл„1, соответствующая порождающе"6 45 му полиному Х + Х + 1 при т =4.

В табл.2 приведена временная последовательность кодов, получаемая в различных цепях предлагаемого устройства в процессе формирования контрольного кода при значении входного сигнала: 1001 1111 0101 1000 и при следующих исходных значениях кода в регистрах сдвига:

Регистр 1 1000

Регистр 2 — 0101

Регистр 3 1010

Регистр 4 — 0011

1239868

Т а б л и ц а 1

Адрес (аргумент) строки таблицы

Адрес (аргумент) строки таблицы

Значение

Значение строки таблицы

f0000

1000

00000

0000

10001

1001

0001

00001

1001.0 1011

00010

0011

1010

10011

00011

0010

10100

1110

00100

0110

0111

10101

00101

1101

10f10

00110

0101

0100

00111

1100

1011 1

1100

0f00

11000

01000

1101

0101

l f 00f

01001

11010

0111

01010

11011

0110

01011

f110 l 1 100

0010

1010

01!00

11101

0011

1011

01101

0001

1001

11110

01110

0000

01111

1000

f 1111

1 L

Входной сигнал

Калы в регистрах сдвига — -т

Такт игнал ооатной связи

Регистр 3 Регистр 4

Регистр 2

Регистр для следующео цикла

I ход j Выход 3

1! 100! 1111 OIOI 1000 1000

0101 1010 0011 . 10101 1111

1010 1101 1001

0100

00011 0010

IfOt 1110 1100 00100 01tO!

001 1111

00010

1001

1001

0110 .0111 1!10

1!010 Ot11 - t001 0111 0111 1010

1100

l 0 f i 1011

0111

2 1001 11!1 0101 строки таблицы

Таблица 2

Значение контрольного кода

1010 0100 0011 0101

0111 1010 0100 0011

0111 0111 1010 Ot00

1! IO 1001 01!1 0111

9868

СЖАТОМ

Таким образом, устройство обрабатывает за один такт м разрядов, что дает повышение быстродействия устройства по сравнению с известным устройством в раз. При включении предлагаемого устройства в состав

ЭВИ в качестве отдельных его элементов (сумматоров, запоминающего устройства и т.д.) могут быть использованы уже существующие элементы ЭВИ, что дает дополнительный выигрыш в оборудовании.

Предлагаемое устройство может быть использовано и для замены последовательного кодирующего устройства, формирующего контрольный код, представляющий собой остаток от деления входной кодовой последовательности на порождающий полином. Для этого необходимо только заменить таблицу в запоминающем устройстве.

Формула изобретения

Кодирующее устройство, содержащее -разрядный регистр сдвига, где

И вЂ” степень порождающего полинома, К сумматоров по модулю два, где К— число информационных разрядов порождающего полинома, вход перного сум . матора по модулю два является одни.-. входом устройства, а выход первого сумматора по модулю два подключен к входу -разрядного регистра сдвига, о т л и ч а ю щ е е с я тем, что, с цел:ью повышения бь1стродействия путем последовательно-параллельной обработки информации, в него введены (-Ê) сумматоров по модулю два и запоминающее устройство, а i-. -разв 1 рядный регистр разбит íà t " ; -разрядных регистров сдвига, одни входы (-1) сумматоров по модулю два являются другими входами устройства, зыхоцы (Ь -1) сумматоров по модулю два подключены к входам (-1).

° "/, -разрядных регистров сдвига, выходы разрядов которых являются выходами устройства, а выходы переноса подключены к одной группе входов запоминающего устройства, а К предпоследних разрядов "lW -разрядных

25 регистров сдвига подключены к другой группе входов .запоминающего устройства, выходы которого подключены к другим входам соответствующих сумматоров по модулю два.

1239868 к

tf к и и о о

Составитель M. Сидорова

Техред П.Олейник Корректор В. Бутяга

Редактор A. Сабо

Заказ 3409/57

Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная,4