Устройство для определения параметров импульсных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в системах контроля и испытаний. Цель изобретения - повышение быстродействия и уменьшение объема памяти. Цель достигается заменой программного формирования адреса выборки следующего значения аппаратурным с помощью счетчика. Кроме того, быстродействие повышается за счет параллельности процессов обработки параметров и формирования адреса. Устройство содержит блок 1 обработки, постоянный запоминакиций блок 2, оперативный запоминаюсцш блок 3, блок 4 индикации, блок 5 приоритетного прерывания, генератор 6 тактовых импульсов , шину адреса, шину 8 данных, регистр 9 состояний, элементы ИЛИ 10, 11,аналого-цифровой преобразователь 12,счетчик 13 адреса, триггер 14, вход 15 выбора подпрограммы устройства . Зил. (/) С 1C 4ib tC to сд Риг.1

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

25 А1

t19) (Ш ао 4 С 06 F 3!05 15!46

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ г(13 1,. Я,, l3

43%|ФМЯА

Щиг.1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3751466/24-24 (22) 29.03 ° 84 (46) 30.06.86. Бюл. N 24 (71) Новосибирский электротехнический институт (72) В.М. Сидоров и А.А. Харлашкнн (531 681.325(088.8) (56) Система сбора и обработки данных для управляющей ЭВИ.-Вычисл.техника. Экспресс-информация, 123, 1981, реф. 126, с..18 — 30.

Соботка 3., Стары Я. Микропроцессорные системы. M.: Энергоиздат, 1981, с. 280 — „290. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПАРАМЕТР0В ИМПУЛЬСНЫХ СИГНАЛОВ (57) Изобретение относится к области вычислительной техники и может быть использовано в системах контроля и испытаний. Цель изобретения — повышение быстродействия и уменьшение объема памяти. Цель достигается заменой программного формирования адреса выборки следующего значения аппаратурным с помощью счетчика. Кроме того, быстродействие повышается за счет параллельности процессов обработки параметров и формирования адреса.

Устройство содержит блок 1 обработки, постоянный запоминающий блок 2, оперативный запоминающий блок 3, блок

4 индикации, блок 5 приоритетного прерывания, генератор 6 тактовых импульсов, шину адреса, шину 8 данных, регистр 9 состояний, элементы ИЛИ 10, 11, аналого-цифровой преобразователь

12 счетчик 13 адреса, триггер 14, вход 15 выбора подпрограммы устройства. Зил.

1241225

Изобретение относится к вычислительной технике и может быть использовано в системах контроля и испыта-. ний конструкций на удельные нагрузки и вибрацию, а также для научных ис-. следований.

Цель изобретения — повышение быстродействия устройства и уменьшение требуемого объема постоянной памяти.

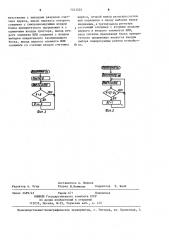

На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 граф-схема алгоритма определения амплитуды импульснОго сигнала„ на фиг. 3 — граф-схема алгоритма определения длительности импульса на уровне О,i максимального значения.

Устройство содержит блок 1 обработки, выполненный на микропроцессоре, постоянный запоминающий блок 2, оперативный запоминающий блок 3, блок 4 индикации, блок 5 приоритетного прерывания, генератор 6 тактовых импульсов, шину 7 адреса, шину 8 данных, регистр 9 состояний, элементы

ИЛИ 10 и 11, аналого †цифров преобразователь 12, счетчик 13 адреса, триггер 14 и вход 15 выбора подпрограммы работы устройства.

На фиг. 2 и 3 приняты следующие обозначения: t — длительность импульсного воздействия на уровне 0,1 амплитуды; U — амплитуда импульсного воздействия; А — накопительный регистр блока 1; B,Ñ,D,Е,Н,L — pei гистры общего назначения блока 1; ВС, РЕ,HL — сдвоенные регистры общего назначения блока 1; ОЗБ — оперативный запоминающий блок; N — ячейка памяти, адрес которой указывает регистр Ш.

Устройство может быть выполнено на однокристальном микропроцессоре

К580 ИК80 и схеме приоритетного прерывания К589 ИК14.

Устройство работает в режимах регистрации и обработки.

В режиме регистрации пусковой импульс поступает на вход триггера

14 и устанавливает его в нулевое состояние, сигнал с нулевого выхода триггера 14 поступает на вход захвата и устаноцочный вход блока 1 и переводит его адресные и информационные выходы в состояние с высоким выходным сопротивлением, а также устанавливает счетчик команд (не показан) блока 1 в нулевое состояние. Кроме того, указанный сигнал поступает через элемент ИЛИ 10 на вход выборки

50 ющем блоке 2 начиная с нулевого адреса располагается программа определения максимума импульсного сигнала.

КОды команд или констант поступают с. выходов блока 2 через шину 8 данных на информационные входы блока 1. Обращение к оперативному запоминающему блоку 3 происходит как к внешнему устройству, при этом сигнал ввода оперативного запоминающего блока 3.

Сигнал с единичного выхода триггера

14 снимает запрет на работу аналогоцифрового преобразователя 12, и с его информационных. выходов код поступает на шину 8 данных и далее на информационные входы оперативного запоминающего блока 3. Импульс синхронизации с выхода аналого-цифрового преобразователя 12 стробирует запись информации в оперативное запоминающее устройство 3 по адресу, указанному счетчиком 13 адреса, переклкчение которого происходит по спаду этого импульса синхронизации, поступающего через элемент ИЛИ 11 на счетный вход счетчика 13 адреса. При записи во

see ячейки оперативного запоминающего блока 3.происходит переполнение счетчика 13 адреса, импульс с выхода переноса которого устанавливает триггер 14 в единичное состояние, запрещая тем самым работу аналого-цифроI ваго преобразователя 12, снимает сиг25 нал с входа захвата и установочного входа блока 1 и через элемент ИЛИ 10 снимает сигнал с входа выборки оперативного запоминающего блока 3. Кроме того, импульс переполнения счетчика

y() 13 адреса поступает и на вход синхронизации блока 5 приоритетного пре рывания„ однако прерывания не происходит, так как блок 1 по выходу разрешения прерывания запрещает выборку блока 5 приоритетного прерывания.

На этом режим регистрации заканчивается и начинается обработка.

В режиме обработки блок 1 под управлением генератора б тактовых импульсов выдает в начале каждого ма4 шинного цикла на шину 8 данных код состояния, который фиксируется в регистре 9 состояний по входу выборки с помощью генератора 6 тактовых импульсов. В начале обработки блок 1

Я выдает на адресные входы постоянного запоминающего блока 2 нулевой адрес, так как в режиме регистрации счетчик команд блока 1 был установлен в нуле" все состояние. В постоянном запомина124,225 формирует регистр 9 состояний. Этот сигнал поступает через элемент ИЛИ 10 на вход выборки оперативного запоминающего блока 3 и через элемент ИЛИ 11 на счетный вход счетчика 13 адреса, который переключается по спаду этого импульса и выбирает следующий адрес оперативного запоминающего блока 3.

После. обработки всего массива данных снова происходит переполнение счетчика 13 адреса, с выхода переполнения которого сигнал, поступая на синхронизирующий вход блока 5 приоритетного прерывания, вызывает прерывание выполнения программы, так как сигнал разрешения прерывания с выхода блока

1 поступает на вход выборки блока 5 приоритетного прерывания. С помощью прерывания происходит переход от одной подпрограммы циклической обработки данных к другой или сразу к подпрограмме вывода результата на блок

4 индикации, Переходами управляет оператор, подавая на вход 15 блока

5 напряжение логической единицы или логического нуля. Блок 5 приоритетного прерывания формирует вектор прерывания, т.е. определяет адрес прерывающей подпрограммы.

Таким образом, исключаются команды подсчета и анализа числа циклов адресации ячеек оперативного запоминающего блока, т.е. сокращается время цикла обработки ячейки оперативного запоминающего блока, так как алгоритмы обработки данных сравнительно просты, исключение операций по адресной обработке позволяет сократить объем постоянного запоминающего блока и увеличить быстродействие почти вдвое при обработке больших массивов данных.

В силу того, что граф-схемы (фиг. 2 и 3) не содержат выходов из циклов, переход от одной подпрограммы к другой происходит с помощью прерывания после обработки всего массива данных.

Скорость регистрации зависит только от оперативного запоминающего блока, так как используется канал прямого доступа к памяти. Функциональные возможности устройстВа могут быть расширены путем соответствующего изменения содержимого постоянного запоминающего блока, т.е. могут определяться длительности фронтов и площади импульса на различных уровнях от максимума.

Формул а и з о б р е т е н и я

Устройство для определения параметров импульсных сигналов, содержа5 щее блок обработки, выполненный на микропроцессоре, постоянный запоминающий блок, блок приоритетного прерывания, регистр состояний, генератор тактовых импульсов и оперативный запоминающий блок, информационные входы-выходы которого соединены через шину данных с информационными входами-выходами блока обработки, с информационными выходами постоянного за15 поминающего блока и блока приоритетного прерывания и с информационным входом регистра состояний, адресные выходы блока обработки соединены соответственно с адресными входами пос20 тоянного запоминающего блока, вьжод запроса прерываний блока приоритетного прерывания соединен с входом запроса прерываний блока обработки, вход выборки постоянного запоминающе25 го блока соединен с первым выходом регистра состояний, тактовый вход блока обработки соединен с первым выходом генератора тактовых импульсов, второй выход которого соединен с синхронизирующим входом регистра состояний, выход разрешения прерывания блока обработки соединен с входом выбор. ки блока приоритетного прерывания, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия уст-ройства, в него введены два элемента

ИЛИ, счетчик адреса, триггер, блок индикации и аналого-цифровой преобра. зователь, информационный вход которо40 го является информационным входом устройства, информационные выходы аналого-цифрового преобразователя соединены через шину данных с информационными входами блока индикации и с

45 информационными входами-выходами блока обработки и оперативного запоминающего блока, вход разрешения аналогоцифрового преобразователя соединен с единичным выходом триггера, а выход готовности подключен к входу записи оперативного запоминающего блока и к первому входу первого элемента ИЛИ, нулевой выход триггера соединен с первым входом второго элемента ИЛИ, с входом захвата и с установочным

5 входом блока обработки, нулевой вход триггера является входом пуска устройства, адресные входы оперативного запоминающего блока соединены соот1241225

Составитель А. Жернов

Техред Н.Бонкало Корректор Т. Колб

Редактор А. Огар

Заказ 3489/43 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д.,4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул, Проектная, 4 ветственно с выходами разрядов счетчика адреса, выход переноса которого соединен с синхронизирующим входом блока приоритетного прерывания и сединичным входом триггера, выход вто= рого элемента ИЛИ соединен с входом выборки оперативного запоминающего блока, выход первого элемента ИЛИ соединен со счетным входом счетчика адреса, второй выход регистра состоя ний подключен к входу выборки блока индикации, а третий выход регистра состояний соединей с вторыми входами первого и второго элементов ИЛИ, вход сигнала прерывания блока приоритетного прерывания является входом выбора подпрограммы работы устройст1О ва.