Устройство для логарифмирования двоичных чисел

Иллюстрации

Показать всеРеферат

Изобретение Относится к области вычислительной техники и предназначено для логарифмирования двоичных чисел в арифметических устройствах ЭВМ и спецпроцессоров. Цель изобретения -. повышение быстродействия и сокращение аппаратурных затрат. Цель достигается применением для вычислений приближенной формулы Z In 1п Хд + (Х-Х)/(Х+Х)/2 In Хо + + 2(Х-Х)/(Х+Хд), где X - нормализованное значение аргумента; опорное значение аргумента; Z - точное значение результата; Zpp - приближенное значение результата. Устройство содержит регистры 1,2, блок памяти 3, блок деления 4, сумматор 5, регистр 6. 3 ил. а (Q (Л 1 фиг.1

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А") (19) (11) (51) 4 С 06 Р 7/556

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМЪ(СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО делАм изОБРетений и ОтнРытий (21) 3756539/24-24 (22) 19.06.84 (46) 30.06.86. Вюл . Ф 24 (72) И .Я.Миронов (53) 681. 325 (088. 8) (56) Авторское свидетельство СССР

11 981741, кл. G 06 F 7/556, 1979.

Авторское свидетельство СССР

Ф 924705, кл. G 06 F 7/556, 1980. (54) УСТРОЙСТВО ДЛЯ ЛОГАРИФМИРОВАНИЯ

ДВОИЧНЫХ ЧИСЕЛ (57) Изобретение относится к области вычислительной техники и предназначено для логарифмирования двоичных чисел в арифметических устройствах

ЭВМ и спецпроцессоров. Цель изобретения †. повышение быстродействия и сокращение аппаратурных затрат. Цель достигается применением для вычислений приближенной формулы

Z = 1n Х =Z 1n Х +

+ (X Xî)/(X+X )/2 = 1n Х, +

+ 2(Х вЂ” Х )/(Х+Х ), где Х вЂ” нормализованное значение аргумента; Х вЂ” опорное значение аргумента; Z — точное значение резуль-! тата; Z — приближенное значение результата, Устройство содержит регистры 1, 2, блок памяти 3, блок деления 4, сумматор 5, регистр 6. 3 ил.

1241237

Изобретение относится к вычислй тельной технике и предназначено для логарифмирования двоичных чисел в арифметических устройствах ЭВМ и спецпроцессоров.

Цель изобретения повышение быстродействия устройства и сокращение аппаратурных затрат.

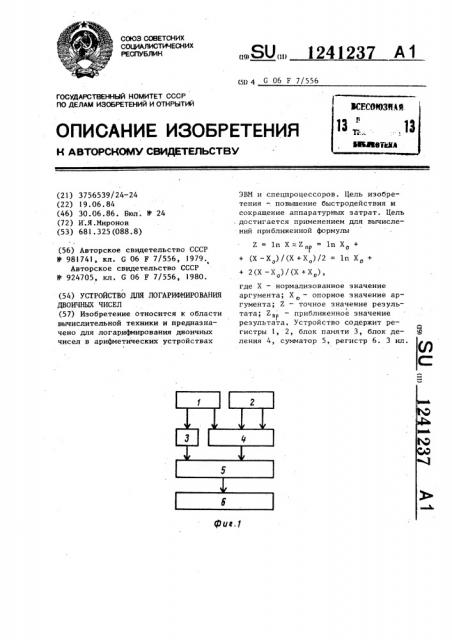

На фиг.1 представлена функциональная схема устройства для логарифмирования двоичного числа; на фиг.2

: и 3 — схема выходов соответственно, регистра старших разрядов и регистра младших разрядов.

Устройство для логарифмирования двоичных чисел (фиг.1) содержит регистр 1 старших разрядов аргумента, регистр 2 младших разрядов . аргумента, блок 3 памяти, блок 4 деления, сумматор" 5 и выходной регистр 6.

Регистр 2 старших разрядов аргумента имеет первый 7 и второй 8 выходы.

Регистр 2 младших разрядов аргумента содержит первый 9 и второй 10 выходы.

Вычисление натурального логарифма от нормализованного значения аргумейта (мантиссы двоичного числа в формате с плавающей запятой, где

0,5 Х с 1,О) в предлагаемом устройстве производится по приближенной формуле: (x — xo)

Z-=1n X Z = 1n Х + — — --.- =

"Р Х+Х о) 2

Х-Х

=1nX +2--- —, Х+Х где Х вЂ” нормализованное значение аргумента;

Х вЂ” опорное значение аргумента;

Z — точное значение результата;

Z — приближенное значение реО зультата.

Значения величин Е =lп Хо для опорных значений аргумента Х вычисляются заранее и заносятся в блок

3 памяти.

Вьжод формулы (1), анализ ее точности в зависимости от объема хранимых в блоке памяти 3 значений Z =

lп Х,обосновывается методом улучо шения сходимости ряда Тейлора для натурального логарифма.

Для вывода формулы (1) значение аргумента Х представляют в виде:

Х

Х=Х о и выводят новую переменную иэ соотношений:

Х 1+V

Х 1-У е (2) Х вЂ” Х

2.

X+ Хо

Разлагая в ряд Тейлора функцию

Z = lп Х = ln Х + lп --- = lп Х +

Х о Х о

l5 . а !

+V

+ lп (--- — )

1 — V получают

1 9

20 Х= lnX = lnX +2 V+---V +

1 r>

+ ---у +

Х= lпХ +2

1 Х-ХФЭ

+ — —. (— -- — -)

3 x+xo

Х вЂ” Х (— — - ) +

Х+ Хо

Х вЂ” Х

6 — — (— — — ) +

5 x+ x (3) При обработке в устройстве п-разрядных чисел Х, получении п-разрядных .результатов 2 = 1n Х в блоке 3 памяр ти хранится q = 2 =. 2 э величин

Z = lп Х для опорных значений аргумента Хр Адрес для выборки величины

Z = 1п Х вырабатывается на первом

О о выходе регистра 1 старших разрядов.

S5 «Х ьXЛ

Величина W = вЂ,=- вырабатывается на

2 втором выходе регистра 1 старших разрядов (старшие разряды величины W) 30 Ограничиваясь в соотношении (37 линейной частью разложения в ряд

Тейлора, получают приближенную формулу 1,17 для вычисления логарифма

Z = 1n Х.

35, Опорное значение аргумента Хо вы-!

Х бирают, так чтобы величина U = — — была х0 близка к единице.

Для формирования адреса выборки

40 из, блока 3 памяти величины Е = ln X„ при анализе нормализованного значения аргумента, а также для формирования величин (Х вЂ” Хо) и (Х + Хо), разбивают интервал изменения числа Х на

45 q = 2 интервалов.

+ Хо

Х = 0.1 а а ... а Ь с с ... с

2 8 Г 7 аВ2- в-л)

Хо 0 1 а а . а 1 О О ... Π— (6) (Х+Х )

-Х + ХХ!

О..a,a ...a b Ь с,с„... с(а (ll 1l -З, 0.1 а!аг ..арЬЬ с, с .. с 1 (n-Е 91

30 а 0 с сг

00 ... 0

Х = 0.1 а,а Х = 0.000 ...01 (!!-12- ) Х+ьХ = 0.1 а,а

Х = 0 а а„... а 1 с, с„... с(„ <„) а 1 О О ... О

X+AX — Х„= 0.000 ... О О с, с,... с („„) Хо

0.1 а,а ... а с<с ... с р >)

0.1 а а ... аВ! О О ... О

Х -Х о

1Pw 2)

2 (Х вЂ” Х) о с(я-о - 3)О.с, z с („e- ) 3 124 и на первом выходе регистра 2 млад— ших разрядов (младшие разряды величины. Щ . Величина (2 ((+2 ) (Х вЂ” Х )) вырабатывается на втором вы оде регистра 2 младших разрядов.

Рассмотрим правила формирования адреса величин Z = 1п Х а также веX+Xo личин (- — - ); (X — X ) .

2 э 0

Так как число 0,5 6 Х с 1 0, то два старших разряда находятся в состоянии

lip! ll

Представим 9 -разрядное двоичное число Х в виде !5

Х =О1 à à .. aEbc. с ...с1! 2 ) (4),где Ъ вЂ” инверсное значение разряда Ь.

Из соотношения 1,6 ) видно, что со—

Х+Х. держимым разрядов величины W = — ——

2 является содержимое (Ь-2) старших разрядов (01 а,а ...а ) числа Х, Значение величины (Х вЂ” Х ) при о

Для дополнительного кода представления двоичных чисел величина — Л Х имеет вид

1237 4

z де (01 а, а „... а ) — старшие разряды

i числа Х; (b с с ...с ) — младшие разряды г <„р! числа Х.

Тогда опорное значение аргумента

X имеет вид о

Х = 01 а а ...а 100...0 (5) о г Г

Из представлений чисел Х; Хо в соответствии с (4) и (5) видно, что содержимое разрядов (а,а ...а ) является адресом для выборки величины

Z = 1n Х из блока 3 памяти

Находят величину прямое и инверсное значение ЬЬ и содержимое остальных младших разрядов (с!с ....с(„ p >)) числа Х, а само чис— ло W стало (n+!) †разрядн.

Находят величину (Х вЂ” Хо) при

Х Х

+ ЛХ = 0.000...0100...0: — Ь Х = 1.111...1)00...0.

Тогда имеют

1241237 (Х + дХ вЂ” X ) = 0.000 ... 00 с,с ... с

ЬХ = l.!11 ... 11 0 0 ... 0 — — — — (8) Х Х 1.111 ... 11 с с ... с

2 ° (Х вЂ” Х ) = l.с с ... с(р ) (е 7) Х-Хо d

Х +Х 2 (tz) Х вЂ” х,I»ñ 2, 55, ((- ++2) Х вЂ” Х

d = 2 2 (— — — -0-)

Х + Х

Из выражения (7) и (8) видно, что величина P2() (Х-Х )) в дополнио тельном коде формируется путем выдачи старшим разрядом инверсного значения Ь и содержи- 15 мого разрядов (с с ... с(Е .) г (n-P-з) т.е. (2 (х — х )) = ь сс ...с„ у

В предлагаемом устройстве для логарифмирования двоичных чисел формирование адреса (а,a>...а ) и величин

Х + Х, tenez)

W = - — —, Q = 2 (X — Х ) произ25 водится следующим образом.

В регистре 1 старших разрядов хранятся (1+2) старших разряда аргумента Х; в регистре 2 младших разрядов хранятся остальные (n-1-2 ) младших разряда числа Х.

Первый выход регистра 1 старших разрядов, который является адресом величины Ео = 1n Хц представляет собой прямые выходы всех, исключая два старших, разрядов регистра l старших разрядов.

Х+Х

Величина W = ††--- формируется

2 путем выдачи прямого кода из регистра 1 старших разрядов, прямого и инверсного содержимого старшего разряда и прямого кода всех остальных разрядов регистра 2 младших разрядов. (е+г)

Величина Q = 2 (Х вЂ” Х ) форми- 45 о руется на втором выходе регистра 2 младших разрядов путем выдачи инверсного значения старшего и прямого кода остальных разрядов регистра 2.

Так как величина 50 то при вычислении величины, (8 г) г Х вЂ” Х, d= 2 2 (Х ° Х, достаточно в блоке 4 деления определить (n-2-1) его старших разрядов.

Для обеспечения выдачи в сумматор

5 величины необходимо выход блока 4 деления подключить к второму входу сумматора 5 со сдвигом вправо на (1+2) разрядов.

Устройство для логарифмирования двоичных чисел при реализации алгоритма по формуле !) работает следующим образом.

Нормализованное и-разрядное значение аргумента Х хранится в регистрах 1 и 2 старших и младших разрядов, имеющих разрядность соответствен-, но (1+2) (n-1-2), при этом выполняется условие 3(1+2) ) п, что позволяет получить точность результата

Z = 1п Х, при которой абсолютная ошиб-, ка не превосходит половины цены млад— шего разряда п-разрядного результата.

На первом выходе регистра 1 старших разрядов вырабатывается адрес числа Е = 1n Xб, которое поступает на выход блока 3 памяти. Адресом является содержимое f младших разрядов регистра 1 старших разрядов.

В блок 4 деления поступают вели+ х (е) чины W = ------ и Q = 2 (Х -Х ) .

2 о, (е )

Делимое Q. = 2 (Х вЂ” Х ) поступает о в блок 4 со второго выхода регистра

2 младших. разрядов, à (n+1) †разрядХ + Х ный делитель W == ----- формируется

2 на втором выходе регистра 1 старших разрядов (1+2), т.е. старших разрядов величины.W, и на первом выходе регистра. 2 младших разрядов (n-1-1), т.е. младших разрядов величины W.

На выходе блока 4 деления, обрабатывающего числа в дополнительном коде находится величина!

24!237

Е=1пХ аког. J

Составитель А.Шуляпов

Редактор Л.Пчелинская Техред Q.Гортвай

Корректор Л.Патай

Заказ 3490/44 Тираж 67!

ВПИШИ Государственного комитета СССР по делам изобретений и открытий!!3035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r.Óæãoðoä, ул.Проектная,4

Так как выход блока 4 деления соединен с вторым входом сумматора 5 со сдвигом на (К+2) разрядов вправо, а выход блока памяти 3 соединен с пер— вым входом сумматора 5, то в последний поступают величины

\ х — х

2 (- — — — )..

Х+ Хр

Выработанный в соответствии с формулой (!) результат

Х вЂ” Хо

Z = 1n Х + 2(- — — -)=Z=ln Х

Р о Х+Х, с выхода сумматора 5 поступает в выходной регистр 6 и является выходной величиной устройства.

Формула и з о б р е т е н и я

Устройство для логарифмирования двоичных чисел,. содержащее регистры старших и младших разрядов аргумента, выходной регистр, блок памяти, блок деления и сумматор, выход которого соединен с входом выходного регистра, первый выход регистра старших разрядов аргумента соединен с адресным входом блока памяти, о т— личающееся тем,что,с

10 целью повышения быстродействия, в нем второй выход регистра старших разрядов аргумента и первый выход регистра младших разрядов аргумента соединены с входом делителя бло15 ка деления, вход делимого которого соединен с вторым выходом регистра младших разрядов аргумента, выход блока памяти соединен с первым входом сумматора, выход блока деления

20 соединен с вторым входом сумматора со сдвигом в сторону младших разрядов на количество разрядов регистра старших разрядов аргумента.