Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в процессорах средней производительности. Целью изобретения является повьшение надежности устройства. Поставленная цель достигается тем, что в устройство, содержащее буферный накопитель, блок оперативной памяти, блок сравнения, регистр адреса столбца, регистр адреса строки, регистр считываемой информации, два триггера обращения , первый элемент ИЛИ, индикаторы состояния адресных шин, формирователь импульсов коррекции, введены , счетчик, триггер установки в ноль, второй элемент ИЛИ, элемент НЕ и блок выборки адреса, содержащий шифратор и элементы сравнения. В устройстве отпадает надобность в мультиплексировании данных, считываемых из разных строк накопителя с целью совмещения операции поиска адреса в блоке оперативной памяти с операцией считьшания данных из накопителя . 1 з.п. ф-лы, 2 ил. S (Л

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

„„SU„„241287 А 1 (59 4 б гт с 19/00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3768701/24 — 24 (22) 11.07.84 (46) 30.06.86. Бюл. Ф 24 (72) А.П.Кондратьев, А.С.Самарский и С.В.Фирсов (53) 681.327(088.8) устройства. Поставленная цель достигается тем, что в устройство, содержащее буферный накопитель, блок оперативной памяти, блок сравнения, регистр адреса столбца, регистр адреса строки, регистр считываемой информации, два триггера обращения, первый элемент ИЛИ, индикаторы состояния адресных шин, формирователь импульсов коррекции, введены счетчик, триггер установки в ноль, второй элемент ИЛИ, элемент НЕ и блок выборки адреса, содержащий шифратор и элементы сравнения, В устройстве отпадает надобность в мультиплексировании данных, считываемых из разных строк накопителя с целью совмещения операции поиска адреса в блоке оперативной памяти с операцией считывания данных иэ накопителя. 1 э.п. ф-лы, 2 ил. (56) Ве11 C. Gordon "Implementation

ofa Buffer memory in minicomputers

Comput Des 1971, 10, Ф 11.

Патент США У 3840863, кл. 340-172, 5, опублик. 1974. (54) БУФЕРНОЕ ЗАПОИИНАКЩЕЕ УСТРОЙ. СТВО (57) Изобретение относится к вычислительной технике и может быть использовано в процессорах средней производительности. Целью изобретения является повышение надежности

В

3Ц f pC pl ; < . у

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 13,, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1МЬЛИу f g

1 124 l 28

Изобретение относится к вычисли-тельной технике и может бьггь использовано в процессорах средней производительности.

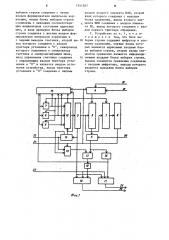

Целью изобретения является повышение надежности устройства, На фиг. 1 изображена бл« буферного запоминающего устройства; . на фиг. 2 — схема блока выборки строки. 1Î

Буферное запоминающее устройство (фиг. 1) содержит буферный накопитель 1, блок 2 оперативной памяти, блок 3 сравнения, регистр 4 адреса столбца, регистр 5 адреса .строки, .15 регистр 6 считываемой информации, индикаторы 7 - 9 состояния адресным шин, триггеры 10 и 11 обращения, блок 12 выборки строки, формирователь 13 импульсов коррекции, счетчик 14, триггер 15 установки в ноль, первый 16 и второй 17 элементы ИЛИ, элемент НЕ 18. На фиг. 1 приняты следующие обозначений. "первые информационные входы 19 устройства, вторые

25 информационные входы 20 устройства, первый 21 и второй 22 управляющие входы устройства, вход 23 установки устройства, синхронизирующая шина 24 устройства, первый 25 и второй 26 управляющие выходы устройства.

Блок 12 выборки строки (фиг.2) содержит элементы сравнения 27 — 29, шифратор 30.

Буферная память работает следую- 35 щим образом.

По адресу столбца, находящемуся в регистре 4 адреса столбца, из индикаторов состояния адресных шин 7 -

9 считываются коды заданного столб- 40 ца, характеризующие соответственно активность первой, второй и третьей строки буферной памяти.

Данные коды сравниваются в блоке 12 выборки с гроки с содержимым счетчика 14, которое равно коду максимально активной строки (11/12СС).

Унитарный код на выходе элементов сравнения прорвой, второй и третьей строки кодируется шифратором 30 в двухразрядный код адреса строки буферной памяти, имеющей максимальную активндсть. Данный адрес заносится в регистр 5 адреса строки, После этого из блока 2 оперативной памяти по адресу столбца и адресу строки считывается адрес строки ойеративной памяти, обращение к которой

7 3 в,цанный момент является наиболее вероятным. Одновременно из буферного накопителя 1 начинает считываться соответствующая информация. После окончания импульса, по которому производилось занесение в регистр 5 адреса строки, пр .-;:=-==-; —.; ся модификация счетчика 14 на "-1". Содержимое счетчика становится: равным 10/2СС, что соответствует активности наиболее активной строки после максимально активной.

Адрес,, считанный из блока 2 оперативной памяти, сравнивается в блоке 3 сравнения с адресом оперативной памяти, который поступает по входу 20 устройства. Ясли сравнение происходит, то на вход триггера 11 обраще-. ния поступает логическая "1" с выхода блока 3 сравнения. По импульсу, поступающему в конце первого такта с входной синхроннзирующей шины 24 устройства на синхровход триггера 11 обращения, он устанавливается в "1", а в триггер 10 обращения к оперативной памяти заносится "0" с выхода элемента 18 HE так как триггер 15 установки в ноль находится в "1". По ,,этому же импульсу в регистр 6 считанной информации заносится слово, считанное из буферного накопителя 1.

Логическая "1" на первом управляющем выходе 25 и "0" на втором управляющем выходе 26 устройства сообщают процессору о том, что требуемая информация считана из буферного накопителя 1 и обращения к оперативной памяти не требуется.

В случае, если сравнение не произошло, триггер 10 обращения к оперативной памяти и триггер 11 обращения устанавливаются в "0", что сообщает процессору о том, что требуемь>й адрес не найден, но поиск не закончен.

Б начале следующего, второго, такта процессора "1" со второго выхода счетчика 14 (так как сод .рлмое счетчика 14 не нулевое) заносится в триггер 15 установки в ноль. Ав регистр 5 адреса строки заносится адрес строки буферной памяти, активность которой равна 1IO/2ÑÑ.

Пссле этого содержимое счетчика модифицируется на "-1" и становится равным 01/2СС, одновременно иэ блока оперативной памяти 2 считывается адрес, соответствующий строке буферной з 1241287 памяти, активность которой равна

10/гсс.

Если во втором такте сравнения не происходит, то в конце данного такта триггер 10 обращения к оперативной памяти и триггер 11 обращения также, как и в предыдущем такте, уста1T If навливаются в 0

В третьем такте проверяется адрес блока 2 оперативной памяти, располо- 10 женной в строке, активность которой равна 01/2СС, а значение счетчика 14 после модификации становится равным

00/гсс.

И если сравнение не производится, то в четвертом такте проверяется последний непроверенный адрес блока 2 оперативной памяти, расположенный в строке буферной памяти, имеющей активность 00/2СС. 20

В начале четвертого такта логической "0" со второго выхода счетчика 14 (так как содержимое счетчика 14 равно нулю) заносится в триггер 15 установки в ноль. И если и в данном 25 ,такте сравнение не произойдет, то на всех входах первого 16 и второго 17 элементов ИЛИ будут "0". И таким образом в конце данного такта в триггер 10 обращения к оперативной памя- 30 ти заносится "1", а в триггер 11 обращения — "9". Это указывает процессору на то, что требуемой ему информации в буферной памяти нет.

В течение всех тактов процессора, в которых производится поиск требуемого адреса, "0" на первом -управляющем входе устройства, а ™1" на втором управляющем входе 22 устройства разрешают установку триггера 10 обраще- 4р ния к оперативной памяти и триггера 11 обращения.

В предлагаемой буферной памяти отпадает надобность в мультиплексирова-. нии данных, считываемых из разных 45 строк накопителя буферной памяти с целью совмещения операции поиска адреса в блоке оперативной памяти с операцией считывания данных из накопителя буферной памяти. Сам буфер- gp ный накопитель 1 может быть реализован более компактно на микросхемах памяти на большее число слов.

Формула изобретения

1. Буферное запоминающее устройство, содержащее буферный накопитель, блок оперативной памяти, блок сравнения, регистр адреса столбца, регистр адреса строки, регистр считываемой информации, два триггера обращения, первый элемент ИЛИ, индикаторы состояния адресных шин, формирователь импульсов коррекции, выходы которого соединены с информационными входами индикаторов состояния адресных шин, выходы которых соединены соответственно с первым, вторым и третьим вхо— дами формирователя импульсов коррекции, адресные входы индикаторов состояния адресных шин соединены с соответствующими входами блока оператив» ной памяти и буферного накопителя и выходами регистра адреса столбца, информационный вход которого является первым информационным входом устройства, управляющий вход регистра адреса столбца является первым управляющим входом устройства, синхровходы регистра адреса столбца, формирователя импульсов коррекции, первого триггера обращения, второго триггера обращения, регистра адреса строки, регистра считываемой информации являются синхровходом устройства, входы,регистра считываемой информации соединены с выходами буферного накопителя, адресные входы которого соединены с входами регистра адреса строки и адресными входами блока оперативной памяти, выходы которого соединены с первым входом блока сравнения, второй вход которого является вторым информационным входом устройства, выход блока сравнения соединен с первым входом первого элемента ИЛИ, выход которого соединен с четвертым входом формирователя импульсов коррекции и с первым входом второго триггера обращения, выход которого является первым управляющим выходом устройства, а вход управления второго триггера обращения соединен с управляющим входом первого триггера обращения и является вторым управляющим входом устройства, выход первого триггера обращения является вторым управляющим выходом устройства, о т л и ч а ющ е е с я тем, что, с целью повышения надежности устройства, в него введены счетчик, триггер установки в "0", второй элемент ИЛИ, элемент НЕ и блок выборки строки, первый вход которого соединен с входом регистра адреса строки, второй выход блока

1241287

Фиг.1 выборки строки соединен с пятым входом формир ов ателя импульс ов коррекциии, входы блока выборки строки соединены с выходами соответствующих индикаторов состояния адресных шин, а вход проверки блока выборки строки соединен с шестым входом формирователя импульсов коррекции и с первый выходом счетчика, второй выход которого соединен с входом триггера установки в "О", синхровход которого подключен к синхровходу счетчика и синхронизирующей шине, вход управления счетчика соединен с управляющим входом триггера установки в "О" и является входом установки устройства, выход триггера установки в "О." соединен .с первым входом второго элемента ИЛИ, второй вход которого соединен с выходом блока сравнения, выход второго эяемента ИЛИ соединен с входом элемента НЕ, вътход которого соединен с входом первого триггера обращения.

2. Устройство по п. 1, о т л ич а .ю щ е е с я тем, что блок вы19 борки строки содержит шифратор и элементьг сравнения, первые входы которых являк гся адресныин входами блока выборки строки, вторые входы элементов сравнения являются информаци15 онными входами блока выборки строки, выходы элементов сравнения соединены с входами шифратора, выходы которого являются выходами блока выборки строки.

1241287

Составитель В.Фокина Редактор Т.Парфенова Техред O.Сопко Корректор М.Пожо

Заказ 3603/46 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.ужгород, ул .Проектная, 4