Устройство задержки

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике. Может быть использовано для формирования задержанных импульсов . Целью изобретения является расширение области применения за счет исключения зависимости величины задержки от скважности входных импульсов и увеличения крутизны фронта выходного импульса. Для этого в устг ройство, содержащее логический элемент И-НЕ 1, времязадающий конденсатор 2, диод 3, входную шину 1, введены компаратор напряжений 4, ключевой элемент 5, делитель 6 напряжения , состоящий из резисторов 7 и 8. На чертеже обозначены; выход 11 устройства , выход 10 элемента И-НЕ. Для устойчивой работы устройства задержки напряжение на втором входе ратора 4, снимаемое с делителя 6 напряжения , выбирается равным или большим минимального уровня логической 1. 2 ил. 010 (Л ND 4 (рог. 7

СОЮЗ СО8ЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4 Н 03 К 5/13

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТ8ЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3835630/24-21 (22) 04.01.85 (46) 30.06.86. Бюл. Р 24 (72) Б.И. Правдин, В.Н.Семенычев и А.С.Шикин (53) 621.374(088.8) (56) Авторское свидетельство СССР

У 517151, кл. Н 03 К 5/13, 1973. (54) УСТРОЙСТВО ЗАДЕРЖКИ (57) Изобретение отнооится к импульсной технике. Может быть использовано для формирования задержанных импульсов. Целью изобретения является расширение области применения за счет исключения зависимости величины задержки от скважности входных им-

„„SU„„1241440 А 1 пульсов и увеличения крутизны фронта выходного импульса. Для этого в уст-, ройство, содержащее логический элемент И-НЕ 1, времязадающий конденса" тор 2, диод 3, входную шину 1, введены компаратор напряжений 4, ключевой элемент 5, делитель 6 напряжения, состоящий из резисторов 7 и 8.

На ; выход 11 устройства, выход 10 элемента И-НЕ. Для устойчивой работы устройства задержки напряжение на втором входе компаратора 4, снимаемое с делителя 6 напряжения, выбирается равным или большим минимального уровня логической

111 и 2 ил

1 124

Изобретение относится к.импульсной технике и может быть использовано для формирования задержанных импульсов.

Цель изобретения — расширение области применения за счет исключения зависимости величины .задержки от скважности входных импульсов и увеличения крутизны фронта выходного импульса.

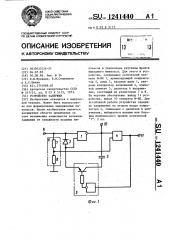

На фиг. 1 приведена схема предлагаемого устройства задержки;на фиг.2— диаграммы напряжений в соответствую щих точках устройства, поясняющие его работу.

Устройство задержки содержит логический элемент И-НЕ 1,,времязадающий конденсатор 2, диод 3, компаратор 4, ключевой элемент 5, делитель .6 напряжения, состоящий из резисторов 7 и 8. Первый вход логического элемента И-НЕ 1 подключен к входной, шине 9 и к катоду диода 3, анод которого соединен с вторым входом. логического элемента И-НЕ 1 и с выходом ключевого элемента 5,выход 10 логического элемента И-НЕ 1. через времязадающий конденсатор 2 соединен с сигнальным входом, а через компаратор 4 с управляющим входом ключево го элемента 5, делитель 6 напряжения включен между входной и общей шиной, причем средняя точка делителя 6 подключена к второму входу компаратора

4,выход 11 которого является выходом устройства.

Устройство задержки работает следующим образом.

В исходном состоянии на входной шине 9 присутствует уровень логического "0" (фиг. 2, интервал времени

t — t ) . При этом на выходе 10 логического элемента И-НЕ 1 устанавливается уровень логической "1", на выходе 11 компаратора 4 — уровень логического "0", при этом ключевой элемент 5 находится в открытом состоянии, а конденсатор 2 заряжен до уровня логической. "1".

При поступлении на входную шину уровня логической " 1" (фиг. 2, момент времени t ), диод 3 запирается, конденсатор 2. начинает заряжаться через входную и выходную цепь логического элемента И-НЕ 1, который при этом охвачен глубокой отрицательной обратной связью через конденсатор 2 и открытый ключевой элемент 5. Вслед- ствие глубокой обратной связи напря1440 2

Формула изобретения

Устройство задержки, содержащее логический элемент И-НЕ, времязадающий конденсатор и диод, подсоединенный катодом к входной шине и к первому входу логического элемента

И-НЕ, а анодом — к второму его входу, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет исключения зависимости

55 величины задержки от скважности вход-, ных импульсов и увеличения крутизны жение на выходе 10 логического элемента И-НЕ 1 уменьшается по линейному закону (фиг. 2, участок А-Б).

Когда напряжение на выходе 10 ло5 гического элемента И-НЕ 1 уменьшится до напряжения на втором входе компаратора 4, определяемого уровнем входного сигнала и коэффициентом деления разистивного делителя 6, на

10 выходе 11 компаратора 4 устанавливается уровень логической."1" (фиг.2, момент времени t ), которым закрывается ключевой элемент 5. ОтрицаВ тельная обратная связь логического элемента И-НЕ 1 при этом разрывается и на его выходе скачком устанавливается уровень логического "0".

При поступлении на входную шину уровня логического "0" (фиг, 2, мо20,мент времени t на выходе 10 логического элемента И-НЕ 1 устанавливается уровень логической " 1" на выходе компаратора 4 с задержкой, обусловленной его быстродействием

25 устанавливается уровень логического

"0" (фиг. 2, момент времени t ), ключевой элемент 5 замыкается и на первом входе компаратора 4 устанавливается напряжение, до которого

З0 разрядился конденсатор 2, начинающий заряжаться до уровня логической "1".

При этом напряжение на втором входе компаратора 4, снимаемое с делителя б напряжения, близко к "О", .т.е. всегда меньше, чем напряжение на кон35 денсаторе 2 и на первом входе компаратора. 4, что обеспечивает устойчивую работу компаратора 4 в процессе заряда конденсатора 2.

46

Для устойчивой работы устройства задержки напряжение на втором входе компаратора 4, снимаемое с делителя

6 напряжения, выбирается равным или большим минимального уровня логической "1".

f0 Риз. 2

Составитель А.Титов

Техред Л.Олейник Корректор Л.Пилипенко

Редактор М.Недолуженко Заказ 3612/54

Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5,Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4. з 1 фронта выходного импульса, в него введены компаратор напряжений, ключеной элемент, резистивный делитель напряжения, причем выход логического элемента И-НЕ через времязадающий конденсатор соединен с сигнальным входом ключевого элемента, а через компаратор напряжений — с его управ241440 4 ляющим входом, выход ключевого элемента соединен с вторым входом логического элемента И-НЕ между входом и общей шиной включен резистивный делитель напряжения, выход которого подсоединен к второму входу компаратора напряжений.