Устройство для цифровой передачи звуковых сигналов

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в цифровых системах связи. Изобретение позволяет повысить качество передачи .звуковых сигналов (например, через спутниковые ретрансляторы ) без увеличения скорости кодирования . Устройство содержит кодер I и декодер 2, соединенные каналом 3связи. Кодер 1 состоит из блока 4хранения и выборки, компаратора 5, регистра 6 последовательных приближений , первого экспандирующего преобразователя 7 и цйфроаналогового преоб (Л to 4 u ч J

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3747949/24-24 (22) 29.05.84 (46) 30.06.86. Бюл. К 24 (72) Н.Н.Маришичев, Г.В.Рабинович и В.Ф.Фиров (53) 621.39(088.8) (56) Авторское свидетельство СССР

Ф 1030975, кл.. Н 04 В 1/64, 1981.

Авторское свидетельство СССР

Ф 995305, кл. Н 03 К 13/01, 1981.

Заявка ФРГ В 3104513, кл. Н 03 К 13/01, 1982.

Применение цифровой обработки сигналов / Под ред. Э.Оппенгейма.

М.: Мир, 1980, с. 96-105.

„„SU „„1241477 А 1 (511 4 Н 03 М 3/00, Н 04 3 1/64 (54) УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ПЕРЕДА

ЧИ ЗВУКОВЫХ СИГНАЛОВ (57) Изобретение может быть использовано в цифровых системах связи.

Изобретение позволяет повысить качество передачи .звуковых сигналов (например, через спутниковые ретрансляторы) без увеличения скорости кодирования . Устройство содержит кодер

1 и декодер 2, соединенные каналом

3 связи. Кодер 1 состоит из блока

4 хранения и Выборки, компаратора 5, регистра 6 последовательных прибликений, первого экспандирующего преобоазователя 7 и цйфроаналогового преоб1

124 разователя 10, декодер 2 состоит из входного регистра 17, первого экспандирующего преобразователя 18, цифроаналогового преобразователя 21 и сглаживающего фильтра 28. Введение в кодер 1 (декодер 2) второго экспандирующего преобразователя 8 (19), коммутатора 9 (20), запоминающего регистра 11 (22), цифрового компаратора 12 (23), RS-триггера 13 (24), дешифратора 14 (25), таймера 15 (26) и элемента 16 (27) ИЛИ обеспечива1477 ет оптимальный режим кодирования (декодирования) сигнала. При этом в случае, когда передаваемый сигнал в выбранном диапазоне изменяется незначительно, кодер работает в линейном режиме с точностью до 10 двоичных разрядов, а когда изменения сигнала значительны или величина,его меньше половины выбранного дйапазона, кодер переходит в нелинейный режим с 8-разрядной точностью измерения отсчетов входного сигнала. 1 ил. 2 табл.

Изобретение относится к технике электросвязи и вычислительной технике и может быть использовано в цифровых системах связи.

Цель изобретения — повышение ка- Ь чества передачи без увеличения скорости кодирования.

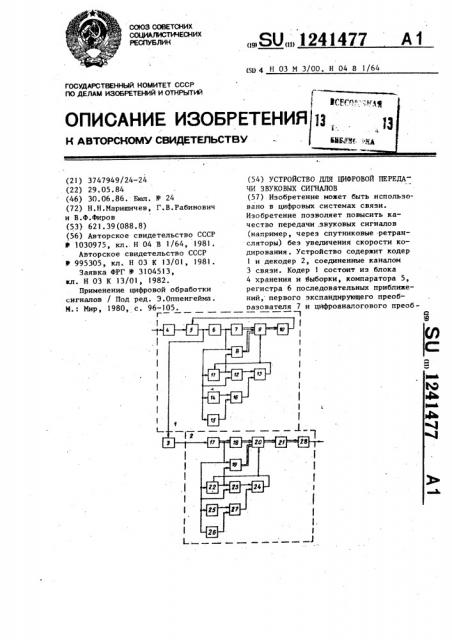

На чертеже изображена блок-схема предлагаемого устройства.

Устройство для цифровой передачи звуковых сигналов содержит кодер 1 и декодер 2, соединенные каналом 3 связи. Кодер 1 состоит из блока 4 выборкй и хранения, компаратора 5, регистра 6 последовательных приближений, первого и второго экспандирующих преобразователей 7 и 8, коммутатора 9, цифроаналогового преобразова. теля (ЦАП) 10, запоминающего регистра 11, цифрового компаратора 12, RSтриггера 13, дешифратора 14, таймера 15 и элемента 16 ИЛИ.: Вход декодера 1 через блок 4 соединен с первым входом компаратора 5, второй вход которого соединен с выходом

ЦАП 10, а выход подключен к входу регистра 6 и является выходом кодера 1. Декодер 2 состоит из входного регистра 17, первого и второго экспандирующих преобразователей 18 и 30 19, коммутатора 20, ЦАП 21, запоминающего регистра 22, цифрового компаратора. 23, RS-триггера 24, дешифратора 25, таймера 26, элемента 27 ИЛИ и сглаживающего фильтра 28. 35

Вход регистра 17 является входом декодера, а выход ЦАП 21 через сглаживающий фильтр 28 соединен с выходом декодера. Идентичные элементы кодера и декодера имеют одинаковые соединения. Входы первого преобразователя 7 (18), запоминающего регистра 11 (22), дешифратора 14 (25) и таймера

15 (26) объединены с первыми входами второго преобразователя 8 (19) и циф- рового компаратора 12 (23) и подключены к выходам регистра 6 (17). Выходы преобразователей 7 и 8 (18 и

19) соединены с соответствующими входами коммутатора 9 (20), выходы которого подключены к входам ЦАП 10 (21). Вторые входы второго преобразователя 8 (19) и цифрового компаратора 12 (23) объединены и подключены к выходам заломинающего регистра

11 (22). Выходы дешифратора 14 (25) и таймера 15 (26) соединены с входами элемента 16 (27) ИЛИ. Выходы цифрового компаратора 12 (23) и элемента 16 (27) ИЛИ подключены к первои второму входам RS-триггера 13 (24), выход которого соединен с управляющими входами коммутатора 9 (20) и запоминающего регистра 11 (22).

Устройство для цифровой переда-. чи звуковых сигналов работает следующим образом.

Звуковой сигнал поступает на вход блока 4 выборки-хранения кодера где фиксируются текущие значения этого сигнала. Полученный сигнал подается на первый вход компаратора 5, в котором каждое отсчетное значение сравнивается с последовательностью значений эталонного сигнала, поступающего на его второй вход с выхода ЦАП 10. Двоичный сиг-. нал, полученный в результате срав-.

1241477 4 нения, поступает на выход кодера 1 и на вход регистра 6 последовательных приближений, вырабатывающего последовательность двоичных чисел, величина которых последовательно 5 приближается к величине кодируемого значения сигнала. При кодировании сигналов звукового вещания регистр

6 вырабатывает последовательность

10-разрядных двоичных чисел, которые 1О подаются на входы экспандирующих преобразователей 7 и 8. Экспандирующий преобразователь 7 преобразует

10-разрядные числа, представленные через порядок и мантиссу, в 14-раз- !5 рядные двоичные числа в соответствии с табл, 1, реализуя цифровую аппроксимацию квазилогарифметическо го закона А-87,6/13. Через коммутатор 9 последовательность чисел подается на вход ЦАП 10, где преобразуется в последовательность значений эталонного сигнала, поступающего на второй вход компаратора 5. В этом режиме работы кодер

1 обеспечивает нелинейное кодирование, .т.е. обеспечивает 8-разрядную точность измерения величин отсчетов сигнала.

Выходной сигнал регистра 6 одно- 30 временно поступает на запоминающий регистр 11 и цифровой компаратор 12, с помощью которых производится сравнение порядка предыдущего числа с порядком последующего. Если эти по- З5 рядки равны, то компаратор 12 вырабатывает сигнал установки RS-триггера 13 в такое состояние, при котором его выходной сигнал запрещает запись в регистр 11 и с помощью коммутаe) тора 9 подключает ЦАП 10 к выходу второго экспандирующего преобразователя 8. Экспандирующий преобразователь 8 преобразует 14-разрядные чис- ла, представленные порядком и мантис- 4 сой, поступающие на его вход от регистра 6 последовательных приближений (разряды А, В, С, Р, Е, F, G, Н, lJ и запоминающего регистра 11 (разряды А, В, С ) в 14-разрядные у двоичные числа арифметического кода, как показано в табл. 2.

Как видно из таблицы, в этом случае кодер 1 обеспечивает кодирование с точностью до десяти двоичных раэ- Ы рядов в диапазоне уровней, ограниченном порядком числа, хранящимся в регистре 11, т.е. работает в линейном режиме. ЕсЛи очередное отсчетное значение входного сигнала выходит за пределы этого диапазона (перегрузка),, то регистр б,формирует число, .содержащее "единицы" во всех разрядах.

Эти числа обнаруживаются дешифратором 14, который вырабатывает сигнал, поступающий. через элемент 16 ИПИ на второй вход RS-триггера 13, изменяя его состояние на обратное. При этом выходной сигнал RS-триггера 13 снимает запрет записи с регистра 11 и подключает с помощью коммутатора 9 входы -ЦАП 10 к выходам экспандирующего преобразователя 7. Аналогичное переключение режима происходит и в случае, когда отсчетные значения звукового сигнала в течение времени, заданного таймером 15, не выходят за пределы половины указанного диапазона (при недогрузке). Таймер 15 вырабатывает сигнал переключения, поступающий с его выхода на вход RSтриггера 13 через элемент 16. KIH, если в течение задаваемого таймером

15 времени не происходит его установки в "0". Установка в "0" осуществляется "единицей" при Б1 или

"нулем" при S=O в следующем эа S раз. ряде числа, что свидетельствует о том, что сигнал кодируется с максимальной точностью, используя весь динамический диапазон кодирования.

При отсутствии сигналов установки в

"0" на выходе таймера 15 формируется сигнал, который изменяет состояние RS-триггера 13, поступая на его вход через элемент 16 ИЛИ, При этом кодер 1 переходит в нелинейный режим работы. Время, задаваемое таймером 15, выбирается в пределах 1-2 мс.

Таким образом, кодер 1 работает поочередно в двух режимах: нелинейном (через экспандирующий преобразователь 7) и линейном (через экспандирующий преобразователь 8)-. Управле-. ние режимом осуществляется самим сигналом: линейный pemM сохраняется, когда изменение уровня сигнала не превышает +3 дБ, а нелинейный реямм устанавливается, когда уровни сигнала меняются в более широких пределах. Взаимодействие кодера 1 с декодером 2 осуществляется через канал 3 связи. Декодер 2 работает синхронно с кодером l, поскольку управление его режимом осуществляется тем же цифровым сигналом, поступающим с выхо1241477

У а б л и ц а 1

II (V (L

Б А В С D Е F G Н I

1 1 0 0uvwхуz1,,0 0 0 1uvwху

z 0 0 О

О О О О 1 и ч w x

О О О О 0 1 u v w у z О О х у z О

О О О О.

1 1 1 1

О О и ч w х у z

1 1 и v w х у z

О 1 О О и ч w х у z 0 1 1 1 1 О и ч w х у г 1 1

Таблица 2

1Г Г TГ

Вмход

8 а Ь с d e f g h i j k 1 а

S- А В С S А В С D Е F С Н .I

1 1 0

Р g R w v w х у х 0 0 0 0

0 P Q R и v м х у а 0 0 0 да компаратора 5 кодера 1. Однако, в отличие от последнего, где экспандирование осуществляется в цепи обратной связи и приводит к компандированию передаваемого сигнала, в декодере 2 экспандированный сигнал поступает с выхода ЦАП 21 через:.сглажива-. ющий фильтр 28 на выход устройства.

При этом в устройстве обеспечиваются

1 1 1

1 1 О

1 0 1

О 1 1

0 1 О

О 0 1

О О О

1 1 1

l 1 g, 1 О 1

0 1 1

О 1 0

0 О 1

О. О О те же параметры качества, что и :в коде с квазимгновенным компандированием> но для этого не требуется повышения скорости кодирования. Кроме того, для передачи порядка чисел не требуется и дополнительной скорости передачи, поскольку этот порядок передается в моменты времени, когда устройlð ство работает в нелинейном режиме. а Ь с d e f g h i j k 1 ш

1 u v;w х у z О О О О О О

О 1 u v w х у г О О О О О

О О 1 и ч w х.у z О О О О

О О О О О 0 1 и ч w х у z

1 1 1 1 1 I О и ч w х у z

1 I 1 1 1 О и ч w х у z 1

1 1 1 О z v w х у z 1 1 1

1 1 О u v w х у z 1 1 1 1

1 0 u v w х у z 1 1 1 1 1

О u v w х у z 1 1 I 1 1 1

1241477

1 г пппб

Продолжение табл.2 ч ° ЮМ

Выход

S а Ь с d е Е N Ь i. ) !с и а

Вход

S А В С S А В С 9 Е F С Н I

1 0 0 Р Q R и ч w x у г N 0 0 P Q R w ч w х у г 0 0

0 0 0 P Q R u ч w x у г 0

0 0 0 0 Р Q R u v w х у z

1 0 0

P Q R u v w x у г

Я R u v w x y z I

1 1 1

I I P

0 1 I

0 0 I 0 N P Q R u v w x y z N 1 1 P Q R u v w x y z 1 I

I P Q R u v w х у z 1 I 1

P Q R u v w х у г 1 I 1

0 0 I

0 0 0

Ф

Формула изобретения. Тираж 816 Подписное

ВНИИПИ Заказ 3614/56

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Устройство для цифровой передачи звуковых сигналов, содержащее кодер, состоящий из компаратора, регистра последовательных приближений, первого экспандирующего преобразователя, цифроаналогового преобразователя и блока выборки и хранения, вход ° которого является входом кодера, выход подключен к первому входу компаратора второй вход которого соединен с выходом цифроаналогового преобразователя, а выход является выходом кодера

35 и подключен к входу регистра последовательных приближений, выходы которого соединены с входами первого экспандирующего преобразователя, выход кодера через канал связи соединен с декодером, состоящим иэ входного регистра, первого экспандирующего преобразователя и соединенных последовательно цифроаналогового пре45 образователя и сглаживающего фильтра, выход которого является выходом декодера, входы первого экспандирующего преобразователя соединены с выхода1ми входного регистра, вход которого

50 является входом декодера, о т л ич а ю щ е е с я тем, что, с целью повышения качества передачи без уве- личения скорости кодирования, в кодер и в декодер введены коммутатор, запоминающий регистр, дешифратор, таймер, цифровой компаратор, элемент

ИЛИ, RS-триггер и второй экспандирующий преобразователь, первые входы которого объединены с соответствующими первыми входами цифрового компаратора и соответствующими входами первого экспандирующего преобразователя, дешифратора, таймера и запоминающего регистра, выходы которого подключены к вторым входам второго экспандирующего преобразователя и цифрового компаратора, выход которого соединен с первым входом RSтриггера, выход которого подключен к управляющим входам запоминающего регистра и коммутатора, первые и вторые входы которого соединены с выходами соответствующих экспандирующих преобразователей, выходы коммутатора подключены к входам цифроаналогового преобразователя, выходы деаифратора и таймера соединены с входами элемента ИЛИ, выход которого подключен к второму входу RS-триггера.