Устройство для декодирования циклических кодов

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

13, 13 111 1ЖА

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР по делАм изобРетений и ОткРытий (21) 3836260/24-09 .(22) 04.01 85 (46) 30.06.86. Бюл. У 24 (71) Специальное. конструкторское бюро вакуумных покрытий при Госплане

ЛатвССР (72) В.Г. Бронов (53) 621.394.14(088.8)

° (56) Авторское свидетельство СССР

У 554626, кл. Н 04 Ь 3/02, 1975.

Авторское свидетельство СССР

11 431638, кл. Н 04 L 3/00, 1972. (54) УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ

ЦИКЛИЧЕСКИХ КОДОВ (57) Изобретение относится к электросвязи. Уменьшается время декодирования и увеличивается помехоустойчивость, Устройство содержит два фильтрующих блока, состоящих из регистров сдвига 1 и 2 и сумматоров по модулю два 3, 4, 5 и 6, два дешифратора (Д) 7 и 8, счетчик 9, два элемента И 10 и ll, блок синхронизации

„.Я0„„1241480 A 1 (511 4 H 03 M 5/02 (БС) 12 и задающий генератор (ЗГ) 13.

При поступлении на вход устройства циклически закодированного сообщения в виде бинарного кода БС 12 вырабатывает тактовые импульсы, синхрониэирующие работу устройства. При прохождении этого сообщения через фильтру.ющие блоки иэ него последовательно исключается информационный и фаэирующий компоненты. В случае поражения принимаемого сообщения помехами, ошибки размножаются в устройстве и единичный сигнал поступает на установочный вход счетчика 9, который подсчитывает число импульсов, определяющее искаженный участок входного со- «о

Q общения. Когда на установочном входе счетчика 9 присутствует нулевой сигнал, счетчик 9 подсчитывает число С: неискаженных символов, поступающих подряд на вход устройства. Цель достигается введением Д8 БС 12 и

3Г13. 2 ил.

Фви3»

1 124

Изобретение относится к электро1 связи и может использоваться в сНс темах передачи данных, телеуправления, телекодовой связи и телесигналиэации для повышения достоверности передаваемой информации.

Цель изобретения — уменьшение времени декодирования и увеличение помехоустойчивости.

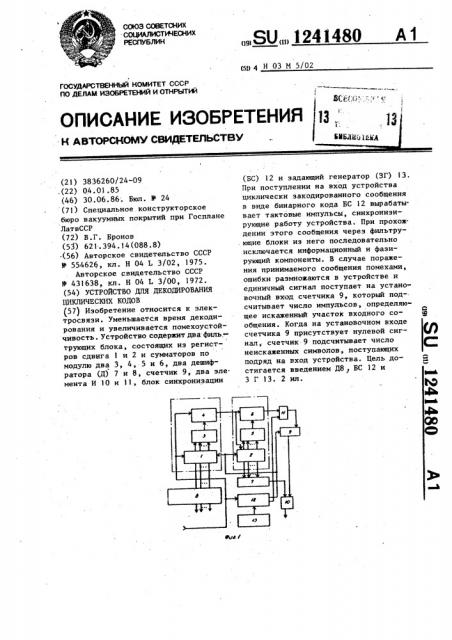

На фиг. 1 представлена структурная электрическая схема устройства для декодирования циклических кодов; на фиг. 2 — структурная электрическая схема блока синхронизации.

- Устройство для декодирования циклических кодов содержит первый и

I второй регистры 1 и 2 сдвига, первый и второй сумматоры 3 и 4 по модулю два, третий и четвертый сумматоры 5 и 6 по модулю два, дешифратор 7, дополнительный дешифратор 8, счетчик 9, первый и второй элементы И 10 и 11, блок 12 синхронизации, задающий генератор 13. Блок синхронизации 12 содержит делитель 14 частоты, блок

15 выделения первого импульса и делитель 16 частоты.

Устройство для декодирования циклических кодов работает следующим образом.

На вход устройства для декодирования циклических кодов (фиг. 1) поступает циклически закодированное сообщение (в виде бинарного кода) с периодом, равным 1 . Оно содержит просуммированные по модулю два в процессе непрерывного кодирования

К-символьное информационное и М-символьное априорно известное фазирующее кодовые слова, имеющие после кодированйя одну и ту же длину И .

Образующие палиномы информационных и фазирунищего кодовых слов Р(х) и

Ф(х) соответственно не должны иметь общих множителей. При использовании кодов длиной v=2 -1, где m =3, 4, 5,... образующие полиномы P(x) и

Ф(х) должны являться. сомножителями двучлена (Х"+1), например, коды

Боуэа-Чоудхури-Хоквингема.

При поступлении на вход устройства для декодирования циклических кодов подобным образом закодированного бинарного. сообщения блок 12 сийхронизации начинает вырабатывать тактовые импульсы, синхронизирующие работу устройства для декодироваm a циклических кодов. Одновременно, в соответствии с тактовыми им1480 2 пульсами, поступающими с первого выхода блока 12 синхронизации на счетный вход счетчика 9 и тактовые входы первого и второго регистров

1 и 2 (состоящие соответственно из

К и М разрядов), в последние последовательно записывается входное сообщение. Через {К+М) тактов отфильтрованное входное сообщение, стробируемое сигналами, снимаемыми с второго выхода блока 12 синхронизации, через второй элемент И 11 начинает поступать на установочный вход. счетчика 9 (для установки последнего в начальное состояние).

Стробирующие сигналы, формируемые на втором выходе блока 12 синхронизации, не перекрываются с фронтами тактовых сигналов и должны быть разнесены во времен:i относительно последних таким образом, чтобы во время их формирования на втором входе вто20 рого элемента И 11 сигнал на его первом входе был уже установлен.

При прохождении входного сообщения через последовательно соединенные первый и второй Хаффменовские фильтка 9. Таким образом, число нулевых символов на выходе второго Хаффменовского фильтра характеризует число безошибочно принятых символов входно ры (состоящие соответственно иэ последовательно соединенных первого регистра 1, первого и второго сумматоров 3 и 4 по модулю два и последовательно соединенных второго регистра 2, третьего и четвертого сумматоров 5 и б по модулю два из него последовательно исключаются (отфильтровываются) информационный и фазирующий компоненты. При безошибочном приеме . на выходе второго Хаффменовского фильтра через (К+М) тактов появляется сообщение, состоящее из нулевых

40 символов, которое после .стробирования поступает на установочный вход счетчика 9. Пока на установочном входе счетчика 9 присутствует нулевой сигнал, счетчик 9 подсчитывает число неискаженных символов, поступающих подряд на вход устройства для декодирования циклических кодов. При поражении принимаемого сообщения помехами ошибки размножаются устрой"0 ством для декодирования циклических кодов и на выходе второго Хаффменовского фильтра появляются единичные сигналы, поступающие после стробирования на установочный вход счетчиР 1- 2 . 6 Р (1-Р) з 1241 го сообщения. При отсутствии ошибок в сообщении на выходе второго элеl мента И 11 через (К+М) тактов формируется нулевой сигнал. Счетчик 9 подсчитывает число тактовых импульсов, поступающих на его счетный вход с выхода блока 12 синхронизации. При этом степень достоверности принятой информации определяется для случая нескоррелированных ошибок, !и подчиняющихся биноминальному закону распределения вероятностей, по выражению где r — - число проверочных символж кодового слова с образунищим полиномом (Р(х) Ф(х) ;

P — вероятность ошибочного прие ма символа;

n — - длина кодового слова; б — кратность гарантийно обнаруживаемых ошибок кода с образующим полнномом jP(x)r

«Ф(х) ;

В„ — число вариантов ошибок i-ой кратности, не обнаруживаемых данным кодом;

С вЂ” число, определяющее объем счеучика 9, причем

С= и где N — - объем счетчика 9;

К, М вЂ” числа разрядов соответствен- 35 но первого и второго регистров 1 и 2.

При подсчете счетчиком 9 необходимого числа импульсов с его выхода на второй вход первого элемента И 10 поступает единичный сигнал, разре- 40 шающий прохождение единичного им. пульсного сигнала с выхода дешифратора 7 на дополнительный выход

"Готов" устройства для декодирования циклических кодов. На время присут- 45 ствия на дополнительном выходе устройства для декодирования цикличес" ких кодов импульсного единичного сиг. нала на выходах дополнительного дешифратора 8 присутствует декоди- 50 рованное входное сообщение.

Сигнал на выходе дешифратора 7 появляется при поступлении на его входы комбинации циклового фазирования с учетом фазового сдвига. Нали- 55 чие данной комбинации иа входах дешифратора 7 при одновременном наличии единичного сигнала на выходе

480 4 счетчика 9 означает, что в первом регистре 1 в данный момент времени находится сумма по модулю два исход" ного К-символьного сообщения и первых К символов фаэируюшего кодового слова (априорно известных). Следо.вательно, дополнительный дешифратор

8, состоящий из К независимых ячеек, представляющих собой или непосредственные связи между соответствующими входами и выходами дополнительного дешифратора 8, или инверторы, настроенный на данное априорно известное фаэирующее сообщение, пропускает на свои выходы только исходное информационное сообщение, исключив из кодограммы фазирующую компоненту.

При этом соответствующая ячейка дополнительного дешифратора 8 представляет собой непосредственную связь соответствующего входа и выхода дополнительного дешифратора 8, если в соответствующем разряде первого регистра 1 содержится сумма по модулю два информационного и нулевого символа фазирующего кодовых слов.

Если в соответствующем (рассматриваемой ячейке дополнительного дешифратора 8) разряде первого регистра содержится сумма по модулю два некоторого информационного и единичного символов фазирующего кодовых слов, то одноименная ячейка дополнительного дешифратора 8 представляет собой инвертор.

Таким образом, нри прохождении .входного сообщения через первый

Хаффменовский фильтр информационных кодовых слов на его выход через К . тактов в случае безошибочного приема поступает только фазирующее кодовое слово с определенным фаэовым сдвигом, определяемым образующим полнномом

Р(х) информационных кодовых слов, а через (К+И) тактов с выхода Хаффменовского фильтра фаэирующего кодового слова. На установочный вход счетчика

9 начинает поступать последователь- ность, состоящая лищь иэ нулевых символов. Длина последней определяет неискаженный участок входного сообщения. При приеме устройством для декодирования циклических кодов участка неискаженного входного сообщения не-менее заданной длины (что определяет достоверность его приема и регулируется выбором объема счетчика 9) и при поступлении на входы дешифрато1241480

Фиг.2

ВНИИПИ Заказ 3614/56 Тираж 816 Подписное

Произв.-полигр. пр-тие, r. Ужгород, ул. Проектная, 4 ра 7 комбинации циклового фазирования с учетом фазового сдвига, на дополнительном выходе устройства для декодирования циклических кодов по5 является импульсный сигнал, на время присутствия которого на выходах устройства для декодирования циклических кодов фиксируешься исходное декодированное сообщение. !О

Блок 12 синхронизации работает следующим образом, При поступлении на его информационный вход входного сообщения по каждому переднему фрон-. ту входного сигнала (переходу с логического "О" на логическую "1") блок

15 выделения выделяет первый импульс из серии импульсов с первого выхода делителя 14. Импульсы с выхода блока

15 выделения поступают на вход установки делителя 16. С второго выхода делителя 14 на счетный вход делителя

16 поступают импульсы той же частоты, что и на его первом выходе, но сдвинутые относительно первых .на половину д периода следования. Входные импульсы делителя 14 формируются задающим генератором 13. При этом фазовая автоподстройка тактовых импульсов осуществляется по передним фронтам выходных сигналов. Импульсы с первого выхода делителя 14 поступают также на первый выход блока 12 синхронизации. С выхода делителя 16 на второй выход блока 12 синхронизации поступают тактовые импульсы, формируемые примерно на середине временных интервалов, соответствующих информационным посылкаме

Формула изобретения

Устройство для декодирования циклически кодов, содержащее последовательно соединенные первый регистР 45 сдвига, первый и второй сумматоры по модулю два, последовательно соединенные второй регистр сдвига, третий1 и четвертый сумматоры по модулю два,, последовательно соединенные дешифра- тор и первый элемент И, а также счетчик и второй элемент И, вход которого подключен к выходу четвертого сумматора по модулю два, второй вход четвертого сумматора пО модулю два подключен к выходу второго сумматора по модулю два, выходы дополнительных разрядов второго регистра сдвига подсоединены к соответствующим входам дешифратора, причем втоРой вход второго сумматора по модулЮ два является входом устройства, о т л и ч а ю щ е е с я тем, что, с целью уменьшения времени декодирования и увеличения помехоустойчивости введены последовательно соединенные задающий генератор и блок синхронизации, а также дополнительный дешифратор, при этом информационный вход блока синхронизации подключен к информационному входу первого регистра сдвига и к второму входу второго сум атора по модулю два, выход которого подсоединен к информационному входу второго регистра сдвига, первый выход блока синхронизации подсоединен к тактовым входам первого и второго регистров сдвига и счетному входу счетчика, второй выход блока синхронизации подсоединен к второму входу второго элемента И, выход которого подсоединен к установочному входу счетчика, при этом выход счетчика подсоединен к второму входу первого элемента И, а выходы разрядов первого регистра сдвига подсоединены к соответствующим входам дополнитель. ного дешифратора,- выходы которого являются выходами устройства, дополнительным выходом которого является выход ..первого элемента И.