Декодирующее устройство

Иллюстрации

Показать всеРеферат

Изобретение является усовершенствованием изобретения по авторскому свидетельству № 1127089 и позволяет расширить функциональные возможности устройства путем снижения частоты синхронизации на предельных частотах декодирования М последовательностей. Декодирующее устройство содержит три триггера.1, 2, 3, элемент ИЛИ 4 и сумматор 5 по модулю два, один из входов которого является входом управления устройства. На предельных частотах на этот вход подается логический нуль и тактирование второго и третьего триггеров 2, 3 осуществляется с задержкой относительно первого триггера 1. На низких чвстотах на вход управления подается логическая единицаJ при этом тактирование второго и третьего триггеров 2,3 осуществляется в противофазе по отношению к первому триггеру 1. 2 ил. § (Л с ISD 4 00 1Ч 0tf.

СОЮЗ СОВЕТСКИХ

РЕСПУБЛИК (19 (1})

Ш4 НОЭИ5 08

А2

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

«вщЬ4НОТЕМ А

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 1127089 (21) 3821593/24-24 (22) 05.12.84 .(46) 30.06.86. Бюл. Ф 24 (72) В.В. Кацман (53) 681.32(088.8) (56) Авторское свидетельство СССР

У 1127089, кл. Н 03 К 13/24, 1983. (54) ДЕКОДИРУИЩЕЕ УСТРОЙСТВО (57) Изобретение является усовершенствованием изобретения по авторскому свидетельству У 1127089 и позволяет расширить функциональные воэможности устройства путем снижения частоты синхронизации иа предельных частотах декодирования М последовательностей.

Декодирующее устройство содержит три триггера.1, 2, 3, элемент ИЛИ 4 и сумматор 5 по модулю два, один из входов которого является входом управления устройства. На предельных частотах на этот вход подается логический нуль и тактирование второго и третьего триггеров 2, 3 осуществляется с задержкой относительно первого триггера 1. На низких чйстотах на вход управления подается логическая единица при этом тактнрование второго и третьего триггеров 2, 3 осуще-. ствляется в противофазе по отношению к первому триггеру l. 2 нл.

1 1241

Изобретение относится к вычйслительной технике, может применяться, например, для декодирования сигналов в волоконно-оптических линиях связи и измерителях коэффициента ошибок, и является усовершенствованием изобретения по авт. св, В 1127089.

Цель изобретения — расширение

Функциональных воэможностей путем снижения частоты синхронизации на предельных частотах декодирования

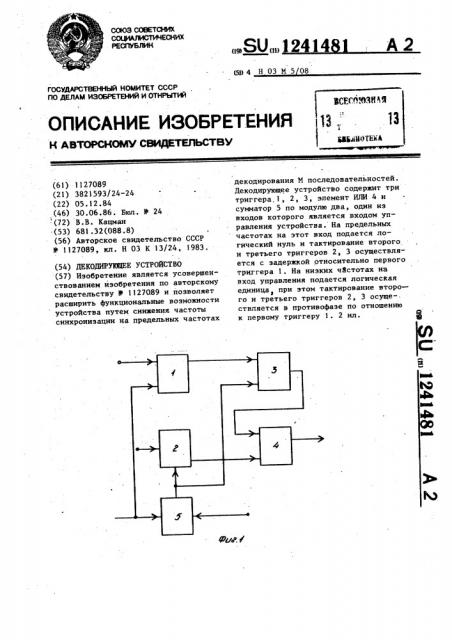

М-последовательностей, На фиг. 1 приведена функциональная схема декодирующего устройства; на фиг. 2 — временные диаграммы его работы.

Декодирующее устройство состоит из первого, второго и третьего триггеров 1-3, элемента ИЛИ 4.и сумматора 5 по модулю два, первый вход которого объединен с входом синхронизации первого триггера 1 и является тактовой шиной устройства, второй вход является входом управления устройства, а выход подключен к входам синхронизации второго и третьего триггеров

2 и 3, выходы которых соединены с входами элемента ИЛИ 4, выход которого является выходом устройства.

Информационные входы первого и второго триггеров 1 и 2 являются соот.ветствующими входными шинами устройства. Выход первого триггера 1 соединен с информационным входом третьего триггера 3. Первая и вторая входные шины служат для подачи прямого и инвертированного входного сигналов "Информация" и "Информация"

Работа декодирующего устройства основана на свойстве М-последовательностей: выборка из М-последовательности с периодом дискретизации

Т значений отстоящих одно от другого на 2" Т тактовых интервалов дает

М-последовательность с теми же структурными свойствами„ Таким образом можно декодировать импульсные значеиня кодовой последовательности 2" Т. Допустим, что максимальная частота преобразования равна F> < Ä макс а задержка сумматора 5 по модулю два ориентировочно равна 1/2F ä„

В соответствии со свойством М-последовательности можно декодировать не каждый тактовый интервал, а значения последовательности в пределах тактового интервала, равного Т, отстоящие одно от другого на величину, равную 2 Т.

481 2

На основании анализа двух стробвыборок с частотой следования Р„ /2 макс определяют единичное или нулевое значение М-последовательности. Если декодируют последовательности

Г(S(kT)) то значение первообразной М-последовательности определяют к на основании оценки значений Sl (2 kT) и Яг(2" kT), Si (2" kT) =Г18 (kT)$ g (t-t -2" kT)

Бг (2" kT) =Г(8(! Т)3 5(t-t — — -2 kT) гце Г (я (!су)) — функциональное преобразование исходной последовательности S(kT), в результате которого формируется код CMI> 3 it) — ФУнкция

Дирака; (kT) 1 когда S (2 kT) VS (2 kT) 1 г ll

0 когда S<, 2 kT) Л S (2 kT)=0Если исходная кодовая последова-i тельность S (kT) имеет структуру, представленную на фиг. 2q, принцип образования кода CNI заключается в следующем: каждое последующее эначе2 ние этой последовательности передается чередующимися импульсами положительной или отрицательной полярности, длительность котофых равна

Т а каждое нулевое значение - импульсами положительной и отрицатель-. ной полярности,, длительность каждого из которых равна Т/2.

Если сигналы "Информация" и "Информация" имеют структуру, представленную на фиг. 2Я, 28 их значения считываются тактовыми сигналами и в дискретном автономном времени 1, t 1 2, ..., и и 1, 2, ..., и, которое соответствует дискретам 2 kT. В реп зультате этого на выходе триггера 2 находится последовательность импуль сов, представленная на фиг. 2g а на выходе триггера 1 — последовательность импульсов, представленная

4 на фиг. 2 . Последовательность импульсов с выхода триггера 1 подвязывается к дискретному автоматному

t f ( времени l, 2 „ ..., n . Последовательности с выходов триггеров 2 и 1

50 суммируются при помощи элемента ИЛИ

4, в результате чего формируется низкочастотная копия сигнала S(kT) (Фиг. 2s). B этом случае на вход управления сумматора 5 по модулю два подается управляющий сигнал уровня логического "0". Если на вход сумматора 5 по модулю два поступают тактовые сигналы ц(с), тогда на вы3 12414 ходе сумматора 5 по модулю два находится сигнал u (t) и (й)=и(1+ ь1, где 7 — задержка на распространение сумматора 5 по модулю два. Для нормальной работы декодирующего устройства необходимо, чтобы эта задержка была ориентировочно равна 1/2Ецп„с .

При частоте дискретизации F« F на управляющий вход сумматора 5 по 1р модулю два подается сигнап управления, соответствующий уровню логической "1". В этом случае Т>> с.

Поэтому можно считать, что u< (t)=

=u(t), т.е. на входы синхронизации первого триггера 1, второго и третьего триггеров 2 и 3 тактовые сигналы поступают в противофазе. БлЯодаря этому на выходах первого или второго триггеров 1 и 2 едИМичный сигнал появляется тогда, когда на вход соответствующего из них поступают импульсы длительностью Т; В третьем триггере 3 происходит задержка сигналов первого триггера 1 на Т/2. щ .С выхода элемента ИЛИ 4 снимается декодированный сигнал.

Для того, чтобы обеспечить нормальное функционирование декодирующего устройства, необходимо совместить во времени сигналы "Информация" и фронты тактовых сигналов (фиг. 2д) 81 4

1, 2,; n таким образом, чтобы фронт тактового сигнала совпал во времени с отрицательным сигналом нулевой посылки длительностью Т/2.

При этом фронт тактового сигнала ,1, 2, ..., n должен совпадать во времени с нулевой посылкой длительностью Т/2 сигнала "Информация". Выполнение этого условия достигается совмещением сигналов "Такт" на выходе устройства и "Информация" таким . образом, чтобы были выполнены перечисленные указанные условия. В измерителях коэффициента ошибок эта операция выполняется автоматически по определенному алгоритму.

Формула изобретения

Декодирующее устройство по авт. св. 9 1127089 о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей путем снижения частоты синхронизации на предельных частотах декодирования

М-последовательностей, в него введен сумматор по модулю два, первый вход которого объединен с входом синхронизации первого триггера, второй вход является входом управления устройства, а выход подключен к входам синхронизации второго и третьего триггеров.

Фиг.2

ВНИИПИ Заказ 3614/56 Тираж 816 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4