Устройство коммутации асинхронных цифровых сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и обеспечивает расширение диапазона скоростей коммутируемых асинхронных цифровьпс сигналов без ухудшения точности коммутации. Устр-во содержит блок памяти информации (БПИ) 1, блок 2 передачи, блок памяти адресов (БПА) 3, формирователь 4 сигналов записи, формирователь 5 сигналов чтения, блок 6 управления коэф. деления, блок 7 делителей частоты, формирователь 8 сигналов блокировки и блок 9 синхронизации. Коммутируемой входящей линии связи (ЛС) отводится определимый временной канал. Один и тот же бит в цикле опроса в магистраль выдается многократно. Для однократной записи информационного бита в БПИ I первая передача бита сопровождается сигналом сопровождения , а последующие - без сигнала сопровождения. Для осуществления соединения временных каналов магистрали или соответствуннцих им входящих ЛС с исходящими ЛС в устр-ве осуществляется временная коммутация посредством записи адресов коммутируемых ЛС в БПА 3 в два этапа. Сначала устанавливается необходимая скорость выдачи информации в исходящую, ЛС, равную скорости входящей ЛС. Это осуществляется подачей команды адреса исходящей ЛС и адреса одной из частот в БПА 3. Каждой скорости передачи соответствует своя частота. Затем устанавливается соединение магистрали с исходящей ЛС. По команде устройства управления адрес записывается в ячейку БПА 3, после чего коммутация считается установленной.Зил. (Л С N 4 ел ND

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„, 1241522 ц 4 H 04 М 9/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

H А BTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3848716/24-09 .(22) 31.01.85 (46) 30.06.86. Бюл. Р 24 (72) Ю.К.Яковлев и В.Н.Курочкин (53) 621.394.76(088.8) (56) Иносэ X. Интегральные цифровые сети связи. M. Радио и связь,1982, с. 77 °

Авторское свидетельство СССР

Р 652727, кл. Н 04 M 9/00, 1977. (54) УСТРОЙСТВО КОММУТАЦИИ АСИНХРОННЫХ ЦИФРОВЫХ СИГНАЛОВ (57) Изобретение относится к электросвязи и обеспечивает расширение диапазона скоростей коммутируемых асинхронных цифровых сигналов без ухудшения точности коммутации. Устр-во содержит блок памяти информации (БПИ/

1, блок 2 передачи, блок памяти адресов (БПА) 3, формирователь 4 сигналов записи, формирователь 5 сигналов чтения, блок 6 управления коэф. деления, блок 7 делителей частоты, формирователь 8 сигналов блокировки и блок 9 синхронизации. Коммутируемой входящей линии связи (ЛС) отводится определнный временной канал.

Один и тот же бит в цикле опроса в магистраль выдается многократно °

Для однократной записи информационного бита в БПИ 1 первая передача бита сопровождается сигналом сопровождения, а последующие — без сигнала сопровождения. Для осуществления соединения временных каналов магистрали или соответствующих им входящих

ЛС с исходящими ЛС в устр-ве осуществляется временная коммутация посредством записи адресов коммутируемых ЛС в БПА 3 в два этапа ° Сначала устанавливается необходимая скорость выдачи информации в исходящую

ЛС, равную скорости входящей ЛС.

Это осушествляется подачей команды адреса исходящей ЛС и адреса одной из частот в БПА 3. Каждой скорости передачи соответствует своя частота.

Затем устанавливается соединение магистрали с исходящей ЛС. По команде устройства управления адрес записывается в ячейку БПА 3, после чего коммутация считается установленной.Зиад.

124

Изобретение относится к электросвязи и может быть использовано H системах для цифровой коммутации асинхронных разноскоростных сигналов телефонногс и телеграфного типа,имеющих скорости передачи да 64 коит/с.

Целью изобретения является расширение диапазона скоростей коммутируемых асинхронных цифровых сигналов без ухудшения точности коммутации.

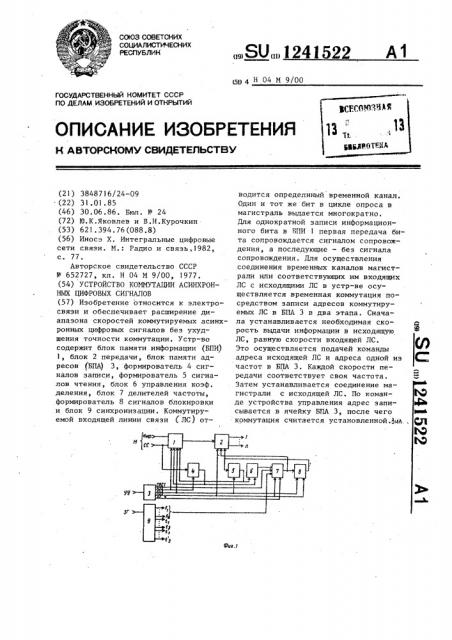

На фиг. 1 приведена структурная электрическая схема устройства коммутации асинхронных .цифровых сигналов, на фи-. 2 и 3 — временные диаграммы, поясняющие работу устройства.

Устройство содержит блок 1 памяти информации, блок 2 передачи, блок 3 памяти адресов, формирователь 4 сигналов,записи, формирователь 5 сигналов чтения, блок б управления коэффициентом деления, блок 7 делителей частоты, формирователь 8 сигналов блокировки и блок 9 синхронизации, I

Устройство коммутации асинхронных цифровых сигналов работает следующим образом.

При побитной коммутации асинхронных разноскоростных каналов в магист( раль иэ входящих линий связи циклически поступают информационные биты с сигналамн сопровождения. Коммутируемой входящей линии связи отводится определенная временная позиция — временной канал. Иэ-за неравенства длительности периодов сигналов, поступающих из Входящих линий связи, один и тот же бит В.цикле опроса в магистраль выдается многократно, так как при мультиплексировании коммутируемых входящих линий связи без потери бита цикл магистрали должен быть меньше длительности периода наибольшей скорости передачи информации. Для однократной записи информационного бита в блок 1 первая передача бита сопровождается сигналом сопровождения, поступающим на синхронизирующий вход блока 1, Последующая передача этого же бита по магистрали производится без сигнала сопровождения. Устройство не имеет внутренних блокировок, поэтому число временных каналов в магисграли раВнО числу исходящих линий сВязи,а цикл работы магистрали равен циклу обслуживания исходящих линий связи,. подключенных к устройству.

Для осуществления соединения временньи каналов магистрали или соответ

1522 ствующих им B, õoäëIIIèõ JIHHHA связи с исходящими линиями связи в устройстве осуществляется временная коммутация посредством =- аписи адре"oB коммутиру.смых линий связи в блок 3 в,цва этапа. Вначале устройство управления устанавливает неОбходимую скорос I ü Вы

IIачи информации в исходящую линию связи, равную скорости входящей линии

1б связи, путем выдачи команды,. адреса исходящей ли -ma связи и адреса одной из частот в блок 3., Частоты вырабатыВаютсл блоком 9 и подключаются к блоку /, причем каждой скорости передачи информации соответствует своя частота. Дпя проключения соответствующей àñтоты на вход делителя блока 7 по команде и адресу исходящей линии связи адрес частоты транслируемый че20 рез блок "» -аписывается В оди -из делителей, после чего частота с Выхода блока 9 поступает на вход соответствующего делителя. Делители (1,,...,п) из I;:.pîêëþ÷eíí6DI: частот выpàáàòûí;-Iþò соответствующие частоты выдачи, которыми информация выдается из блока 2 в исходящие линии связи.

Затем устройство управления устанавливает соединение i ВК магистрали.

ЗО с 1исходящей линией снл- IèI,, для чего выдает команду и адреса А1 и A.I ВК магистрали. По команде адрес А запи=ывается в а-тую ячейку блок 3, после чегс коммутация считается ус- .) тановленной.

Алгоритм работы устройства происходит согласно Временной диаграмме, изображенной на фиг. 2. Период 1 информации, соответствующий наиболь,1О шей скорости информации, меньше длительности цикла Т магистрали или цикла обслуживания исходящих линий связи. Т,. разделен на ЬК магистрали r или Временные позиций обслуживания ,1,.- исходящих линий связи. Каждый ВК нли временная позиция разделена на такты каждый из которых сопержнт в себе соответственно такты t„ -t> .. 3aлись адреса исходящей линии связи по ,;, адресу ВК канала магистрапи в блок

3,. т,е. установление соединения в устрсйстве, происходит в такты tz u каждой временной позиции (ВК).

Запись информации из магистрали в блок 1 происходит следующим образом.

Блок 3 циклически и синхронно с магистралью вырабатывает адреса А, соответствующие ВК магистрали и ис3 ходящим линиям связи. По коду адреса Аь1, равному 1, обслуживается 1 ВК магистрали и 1 исходящая линия связи, по коду адреса Аь,, равному п, обслуживается и ВК и исходящая линия связи.

Запись информации из магистрали в блок l памяти информации происходит следующим образом.

По i-,ìó коду А (i=i,...,ï) в такт tq из i-й ячейки ОЗУ блока 3 считывается j-й адрес исходящей линии связи — адрес А поступающий в блок 1 и формирователь 4. В такт

t< из j -й ячейки ОЗУ формирователя

4 по адресу А считывается адрес заI полнения j — и зоны ОЗУ блока 1 — AP.

В такт t5 в j-ю зону ОЗУ, определя.емую адресом А, и ячейку этой зоны

ОЗУ блока 1, определяемой адресом

Ay%. при наличии сигнала сопровождения магистрали, производится запись информационного бита из магистрали.

В такт tz j-ю зону ОЗУ формирователя 4, определяемую адресом А блока 3, при наличии сигнала сопровождения СС магистрали записывается новый адрес ячейки j зоны ОЗУ блока 1, 1 увеличенный на 1-(Аф1). Зоны памяти блока 1 заполняются последовательно, Последняя ячейка зоны сменяется первой, первая — второй и т,д.

Выдача информации в исходящие линии связи происходит следующим образом.

По j-му коду адреса А (j=l,...,n) в такт t èç j — и ячейки ОЗУ формирования 5 считывается адрес ячейки j-й зоны ОЗУ блока 1. В такт t из j-й зоны ОЗУ блока 1, определяемой адресом А ь блока 3, и ячейки этой зоны а

ОЗУ, определяемой адресом А формирователя 5, считывается информацион-. ный бит, поступающий в блок 2. В блок

2 поступают также сигналы, простробированные тактом t>, определяющие по

) -му коду адреса А исходящую линию связи, и сигналы ОС из формирователя 8. Передним фронтом такта 15при наличии разрешающего сигнала ОС информационный бит записывается в блок 2. Откуда передним фронтом частоты выдачи F, „ поступающей в блок 2 иэ блока 7, информация переписывается и выдается в -ю исходящую линию связи.

Для исключения потери бита скорость опроса ОЗУ блока 1 должна быть выше скорости считывания информации в исходящие линии связи, т.е. Т on241522

4 роса должна быть меньше периода частоты выдачи F . Поэтому для согласования скоростей записи информации из блока 1 в блок 2 вводится сигнал обратной связи ОС, вырабатываемый в формирователе 8 в момент выдачи информации в j--ю исходящую линию связи.

По сигналу ОС производится запись адреса следующей ячейки в J --ю зону !

О ОЗУ в формирователе 5, подлежащей считыванию в следующем цикле опроса из -й зоны ОЗУ блока I и разрешение записи информационного бита в блок

2, поступающего иэ блока 1. В формирователе 8 сигнал ОС вырабатывается

1 для -й исходящей линии связи по переднему фронту частоты выдачи F >.

Опрос сигналов ОС производится адресами Аь циклически, синхронно с оп2р росом остальных блоков устройства.

Для j-й исходящей линии связи в j-й временной позиции, определяемой адресом Ац, сигнал ОС фиксируется на выходе формирователя 8 передним

25 фронтом такта Ц, и хранится до опроса следующего сигнала. Из формирователя 8 сигнал ОС поступает на формирователь 5 и блок 2. В такт при наличии сигнала ОС формирователя

8 в j --ю ячейку ОЗУ формирователя 5, определяемую адресом А 5, записывается следующей адрес ячейки зоны ОЗУ блока 1 — А +1. Информация из зоны паЯ мяти блока 1 считывается последова35 тельно — последняя ячейка сменяется первой, первая — второй и т.д. После записи нового адреса (А +1) в формирователь 5 сигнал ОС в формирователе 8 для .! -й исходящей линии связи снимается, для чего туда поступают сигналы из блока 3, простро ированные тактрм t>. В следующем цикле опроса, если сигнал ОС отсутствует, то в формирователе 5 остает45 ся прежний адрес поэтому информаФ ция, считанная из блока 1, в блок 2 не записывается. таким образом, процессом записи информации иэ блока 1 в блок 2 управ5О ляют частоты выдачи F+-Fg путем поII дачи соответствующих сигналов обрат- . ной связи ОС из формирователя 8.

На фиг. 3 изображена временная диаграмма выдачи информации в первую

55 исходящую линию связи (j =1).

Количество ячеек зоны ОЗУ блока

1 равно 4, поэтому адрес блока чтения меняется циклически от 1 до 4.

1241522

Частота выдачи соответствует скороскбит ти В=64 ---- . Длительность периода с частоты (Тр ) больше длитег?ьности Т? .

Передним фронтом частоты Рд, произво—

:дится перепись информации с входа на выход в блоке 2, а также перевод формирователя 8 в состояние "1".

Состояние формирователя 8 циклически переписывается в блок 2. Формирова-тель 8 циклически обнуляется после операции записи (3??) в формирователь

5. Из диаграммы видно, что при отсутствии сигнала ОС, снимаемого с формирователя в формирователе 5 остается предь?дущий адрес, а в блоке 2 остается предыдущая информация. Благодаря этому обеспечивается последовательная запись информации частотой ро

Гд„со входа на выход блока 2 без пропуска бит.

Генераторы входных линий связи и задающий генератор устройства работают в асинхронном режиме. Для сглажи- 2Б вания неравномерного поступления асинхронных сигналов из магистрали и выравнивания скорости записи и чтения в памяти блока 1.для каждой исходящей линии связи отводится эо- Зб на в нескольких ячеек . Переполнение зоны памяти приводит к потере бита или проскальэывани?о. Поэтому при коммутации асинхронных сигналов вводится индивидуальная подстройка скорости выдачи информации в каждую исходящую линию связи так, чтобы число несчитанных бит информации из зоны памяти блока 1 было равно половине зоны, при этом скорость выдачи ин- яо формации в исходящую линию связи равна скорости поступления информации из входящих линий связи.

О результатах заполнения зон судят по адресам записи А и чтения ячеек

А, хранящихся в памяти формирователей 4 и 5 соответственно. Для каждой исходящей линии, связи в памяти формирователей 4 и 5 отводится своя ячейка. Адрес записи ячейки А? ?показывает номер ячейки зоны памяти блока 1, куда произошла последняя зались информации из магистрали. Адрес чтения ячейки А. показывает номер ч Я ячейки зоны памяти блока 1, откуда произошло последнее считывание бита информация в исходящую линию связи.

Формирователи 4 и 5 циклически опрашиваются адресами чтения зон А??,которые соответствуют номерам исходя?цих линий связи, Для первой исходящей линии связи в первую временную позицию, вырабатываемую адресом А, из первых ячеек памяти формирователей 4 и 5 считываются адреса А1 и А ? ?соответственно.

Эти адреса подаются в блок 6. В такт

-1- из блока 6 считывается текушее значение коэффициента деления по этим адресам, которые записываются в первый делитель блока 7 сигналом дешифратора блока 3 по переднему фронту такта f

Аналогично из блока 6 считываются текущие значения коэффициентов деления и для остальных исходящих линий связи.

Блок 7 делителей цля каждой исходящей линии связи формирует частоту выдачи. Этими частотами информация из блока 2 выдается в исходящие линии связи. Меняя коэффициенты деления в делителях, изменяют величины частот выдачи и соответственно скорости выдачи информации в исходящие линии связи, а следовательно и скорости считывания информации из памяти блока 1 путем выработки сигналов : обратной связи в формирователе 8.

Если в момент чтения информации из памяти блока 1 для исходящей линии связи число несчитанных бит равно половине зоны, то из блока 6 по адресам формирователей 4 и 5 считывается коэффициент деления, равный номинальной величине. Значение частоты выдачи и соответственно скорости выдачи информации в исходную ли.нию связи устанавливаются равными номинальной величине. !

Если B момент чтения информации для исходящей JIHH??H связи число несчитанных бит больше половины зоны

Э то ??з блока 6 по адресам А ьи А форЧ9 мирователей 4 и 5 считывается коэффициент деления меньше номинальной величины„ Значение частоты выдачи

9 формируемой делителем в блоке 6, и соответственно скорость выдачи информации в исходящую линию связи становятся больше номинальной величины.

В результате скорость считывания информации иэ эоны памяти блока 1 для исходящей линии связи увеличивается.

Число несчитаннь?х бит информации в

7 12ч15 зоне памяти блока 1 уменьшается и становится равным половине зоны.

Если в момент чтения информации для исходящей линии связи число несчитанных бит меньше половины зоны то из блока 6 по адресам Aggи А считывается коэффициент деления больше номинальной величины. Значение частоты выдачи и соответственно скорость выдачи:информации в исходящую 10 линию связи становятся меньше номинальной величины. В результате скорость считывания информации из зоны памяти блока 1 для исходящей линии связи замедляется. Число несчитанных 15 бит информации увеличивается и становится равным половине зоны, Аналогично подстройка скорости .считывания информации,иэ зон ОЗУ блока 1 производится и для остальных 20 исходящих линий связи.

Ф о р м у л а и з о б р е т е н и я

Устройство коммутации асинхронных цифровых сигналов, содержащее последовательно соединенные блок памяти информации и блок передачи, а также формирователь сигналов блокировки и блок синхронизации, о т л и ч а ю — ЗО щ е е с я тем, что, с. целью расширения диапазона скоростей коммутируемых аСинхронных цифровых сигналов без ухудшения точности коммутации, в него введены формирователь сигналов З5 записи, формирователь сигналов чтения, блок управления коэффициентом деления, блок делителей частоты и блок памяти адресов, первый выход

22 которого соединен с первым входом блока делителей частоты, выход которого подключен к объединенным второму входу блока передачи и первому входу формирователя сигналов блокировки, выход которого подключен к первому входу формирователя сигналов, чтения и к третьему входу блока передачи, четвертый вход которого объединен с вторым входом формирователя сигналов блокировки и вторыми входом блока делителей частоты и подключен к второму выходу блока памяти адресов, третий выход которого подключен к объединенным первому входу блока памяти информации и первому входу формирователя сигналов записи, второй вход которого объединен с синхронизирующим входом блока памяти информации, второй вход которого подключен к выходу формирователя сигналов записи и объединей с первым входом блока управления коэффициентом деления, второй вход которого объединен с третьим входом блока памяти информации и подключен к выходу формирователя сигналов чтения, второй вход которого объединен с четвертым входом блока памяти информации и третьим входом формирователя сигналов блокировки и подключен к четвертому выходу блока памяти адресов, пятый выход которого подключен к третьему входу блока делителей частоты, управляющий вход которого соединен с выходом блока управления коэффициентом деления, при этом параллель" ный четвертый вход блока делителей частоты соединен с параллельным выходом блока синхронизации.

1241522

bll4

И

ЬЧ

5ПИ

И s-g

Tr-д

Ек,л

Eg Rr

Яп

Ю Т«»

И jr( И

r«

Составитель ВЛ1евцов

Редактор Т.Парфенова Техред О.Гортвай

Корректор В. Бутяга

Заказ 3616/58 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое,предприятие, r Ужгород, ул . Проектная, 4