Способ измерения сдвига фаз

Иллюстрации

Показать всеРеферат

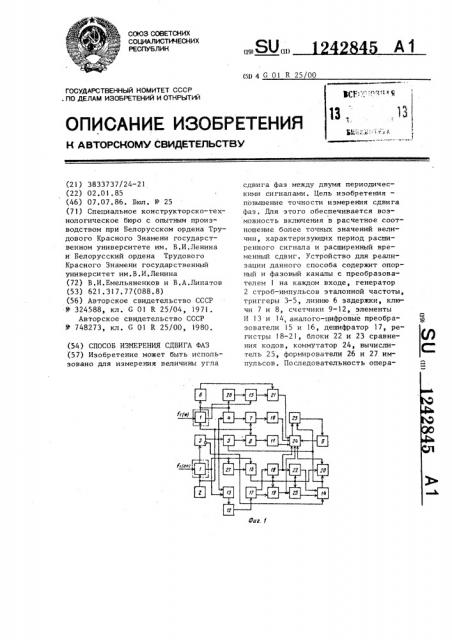

Изобретение может быть использовано для измерения величины угла сдвига фаз между двумя периодическими сигналами. Цель изобретения - повышение точности измерения сдвига фаз. этого обеспечивается возможность включения в расчетное соотношение более точных значений величин , характеризующих период расширенного сигнала и расширенный временный сдвиг. Устройство для реализации данного способа содержит опорный и фазовый каналы с преобразователем 1 на каждом входе, генератор 2 строб-импульсов эталонной частоты, триггеры 3-5, линию 6 задержки, ключи 7 и 8, счетчики 9-12, элементы И 13 и 14, аналого-цифровые преобразователи 15 и 16, дешифратор 17, регистры 18-21, блоки 22 и 23 сравнения кодов, коммутатор 24, вычислитель 25, формирователи 26 и 27 импульсов . Последовательность операс ю (Л ел

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУбЛИК (19) (11) (5D 4 G 01 R 25/00

13, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

47иг. 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР . ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3833737/24-21 (22) 02 ° 01.85 (46) 07.07.86. Бюл. 9 25 (71) Специальное конструкторско-технологическое бюро с опытным производством при Белорусском ордена Трудового Красного Знамени государственном университете им. В,И.Ленина и Белорусский ордена Трудового

Красного Знамени государственный университет им.В.И.Ленина (72) В.И.Емельяненков и В.А.Липатов (53) 621.317.77(088.8) (56) Авторское свидетельство СССР

Ф 324588, кл. G 01 R 25/04, 1971.

Авторское свидетельство СССР

У 748273, кл. G 01 R 25/00, 1980. (54) СПОСОБ ИЗМЕРЕНИЯ СДВИГА ФАЗ (57) Изобретение может быть использовано для измерения величины угла сдвига фаз между двумя периодическими сигналами. Цель изобретения повышение точности измерения сдвига фаз. Для этого обеспечивается возможность включения в расчетное соотношение более точных значений величин, характеризующих период расширенного сигнала и расширенный временньп» сдвиг. Устройство для реализации данного способа содержит опорный и фазовый каналы с преобразователем 1 на каждом входе, генератор

2 строб-импульсов эталонной частоты, триггеры 3-5, линию 6 задержки, ключи 7 и 8, счетчики 9-12, элементы

И 13 и 14, аналого-цифровые преобразователи 15 и 16, дешифратор 17, регистры 18-21, блоки 22 и 23 сравнения кодов, коммутатор 24, вычислитель 25, формирователи 26 и 27 импульсов. Последовательность опера1242845 ций, выполняемых по данному способу, раммы, поясняющие работу устройства, математическая формула расчетного приведены в описании изобретения. соотношения, а также временные диаг- 2 ил.

Изобретение относится к измерительной технике и предназначено, в частности, для измерения величины угла сдвига фаз между двумя периодическими сигналами °

Цель изобретения — повышение точности измерения сдвига фаз.

Увеличение точности измерения сдвига фаэ достигается эа счет того, что в предлагаемом способе обеспечивается возможность включения в расчетное соотношение более точных

I значений величин, характеризующих период расширенного сигнала и расширенный временной сдвиг.

На фиг, 1 представлена структурная схема устройства, реализующего пред- лагаемый способ; на фиг.2 — структурная -схема преобразователя, на фиг фиг.3 — временные диаграммы, поясняющие взаимодействие сигналов при реализации предлагаемого способа.

Способ измерения осуществляется следующим образом.

Формируют из опорного и фазового сигналов, следующих с периодом Т, и сдвинутых одна относительно другой на измеряемый фазовый сдвиг соответственно опорную и фаэовую IIQ следовательности импульсов(фиг ° Зб,в соответственно) с сохранением фазового сдвига и периода. Причем импульсы формируют таким образом, чтобы на их одноименных передних (или задних) фронтах были идентичные участки, близкие к линейным. Стробируют сфррмированную опорную последовательность импульсами эталонной последовательности (фиг.За) и выделяют выборки, амплитуда которых пропорциональна величине стробируемого сигнала в точке стробирования. Формируют пакеты из тех выборок опорной последовательности, амплитуда которых превысит заданное пороговое значение

U . Сформированные таким образом рор пакеты образуют опорную последова." тельность пакетов выборок (фиг.Зг) .

Стробируют сформированную фаэовую последовательность импульсами эталонной последовательности (фиг.За) и выделяют выборки, амплитуда которых пропорциональна величине стробируемого сигнала в точке стробирования.

Формируют пакеты иэ тех выборок фазовой последовательности, амплитуда ко; торых превысит заданное пороговое значение Б„рр, Сформированные таким образом пакеты образуют последовательность пакетов выборок (фиг.Зд).

Пороговое значение Б„ выбирают так, юаа чтобы пакеты начинались (или заканчивались) выборками, полученными при стробировании линейных участков фронтов стробируемых импульсов. Выбирают две, следующие по порядку, >0 первую и вторую выборки в начале (или конце) первого пакета опорной последовательности и измеряют их,ам— плитуды П и Б ;соответственно. Это

1 будут выборки линейного участка фронта импульса опорной последовательности. При этом первую выборку принимают,за начальную границу опорного и фазового интервалов. Выбирают в качестве конечной границы опорного интервала выборку во втором пакете опорной последовательно с ти, ближайшую к началу пакета, если первые две выборки были выбраны в начале первого пакета, или к концу пакета, если первые две выборки были выбраны в конце первого пакета, и измеряют ее амплитуду U . При этом амплиту,ца U, выбранной выборки должна быть в интервале между амплитудами U, и

Б первых,цвух выборок. Выбирают в качестве конечной границы фазового интервала выборку в первом пакете фазовой последовательности, следующем непосредственно эа первым пакетом опорной последовательности. Причем укаэанная выборка является начальной в пакете, если в качестве

1242845 4

15 начальной границы фазового интервала выбрана начальная выборка соответствующего пакета,и конечной, ес-ли в ° качестве начальной гранины фазового интервала выбрана конечная

5 выборка соответствующего пакета. Измеряют амплитуду U этой выборки .

Подсчитывают число И периодов Т, эталонной частоты, укладывающихся в опорном интервале. Подсчитывают число 10

N периодов Т эталонной частоты, укладывающихся в фазовом интервале.

По полученным данным рассчитывают неизвестный сдвиг фаз Ч с помощью следующего расчетного соотношения

U — U1

11 и„— 11, (" (1)

Uъ — U

И

П вЂ” U,, Устройство (фиг, 1), реализующее способ, содержит два канала: опорный и фазовый с преобразователем l на каждом входе, генератор 2 строб-импульсон эталонной частоты, триггеры

3-5, линию 6 задержки, ключи 7 и 8, 25 счетчики 9 — 12, элементы И 13 и 14, аналого-цифровые преобразователи 15 и 16, дешифратор 17, регистры 18-21, блоки 22 и 23 сравнения кодов, коммутатор 24., вычислитель 25, формирователи 26 и 27 импульсов, Каждый из преобразователей содержит формирователь 28 импульсов с линейным участком на переднем фронте, строб-смеситель 29, усилитель-расши—

35 ритель 30, пороговый элемент 31, ключи 32 и 33, счетчик 34 и триггер 35.

Выход генератора 2 соединен с первыми входами и а р алл ел ьных пр е о бр à 3 ователей 1 и импульсными входами клю40 чей 7 и 8, выходы которых подключены соответственно к входам счетчиков

10 и 11 ° Первый выход преобразователя 1 соединен со счетным входом триг.— гера 3, а второй выход — с входом

45 формирователя 27, информационным входом аналого-цифрового преобразователя 15 и первым входом элемента

И 13, выход формирователя 27 подключен к управляющему входу анало50 го-цифрового преобразователя i б. Первый выход преобразователя 1 фазового канала соединен с входом установки

"0" триггера 4, входом формирователя

26 и через линию б задержки с управ—

55 ляющим входом ре гис тра 2 l, а второй выход — с информацион|ьы входом аналого-цифрового преобр aan; ателя 15.

Выход формирователя 26 соединен с управляющим входом аналого-цифрового преобразователя 15. Вывод триггера 3 подключен к счетным входам триггеров

4 и 5 и второму входу элемента И 13.

Инверсный выход триггера 3 соединен с третьим входом элемента И 14, пер-, вый и второй входы которого подключены соответственно к выходам блоков

22 и 23 сравнения кодов. Выходы триггеров 4 и 5 соединены соответственно с управляющими входами ключей 7 и 8.

Выход элемента И 13 подключен к входу счетчика 12, выход которого соединен с входом дешифратора 17 ° Выход аналого-цифрового преобразователя 16 подключен к информационным входам регистров 18-20 к первым входам блоков 22 и 23 сравнения кодов. Выход аналого-цифрового преобразователя 15 соединен с информационным входом регистра 21. Первый и второй выходы дешифратора 17 подключены соответственно к управляющим входам регистров 18 и 19, выходы которых соединены соответственно с вторыми входами блоков

22 и 23 сравнения кодов соответственно. Выход элемента И 14 подключен к управляющему входу регистра 20, входу установки "0" триггера 5 и входу запуска вычислителя 25, синхронизирующий выход которого соединен с входом счетчика 9. Выходы счетчиков

10 и 11 и регистров 18-21 подключены к соответствующим коммутируемым входам коммутатора 24, выход которого соединен с информационным входом вычислителя 25. Выход счетчика 9 подключен к управляющему входу коммутатора 24.

Первым входом каждого из преобразователей 1 является импульсный вход счетчика 34, вторым входом — вход формирователя 28 импульсов. Первым выходом каждого из преобразователей

1 является выход ключа 33, вторым входом — выход ключа 32. Внутри каждого преобразователя 1 выход форьирователя 28 соединен с первым входом строб-смесителя 29, второй вход которого подключен к импульсному входу счетчика 34. Выход стробсмесителя 29 через усилитель-расширитель 30 соединен с входом порогового элемента 31 и импульсным входом ключа 32, управляющий вход которого подключен к выходу порогового элемента 31. Выход ключа 32 соединен с

1242845

20 управляющим входом счетчика 34 и импульсным входом ключа 33. Выход счетчика 34 подключен к выходу установки "1" триггера 35, выход которого соединен с управляющим входом ключа 33, Счетный вход триггера 35 подключен к выходу ключа 33.

Устройство работает следующим образом, 10

В исходном состоянии все счетчики, триггеры и регистры обнулены, ключи закрыты. На первые входы преобразователей 1 опорного и фазового каналов поступают строб-импульсы с выхода генератора 2. На вторые входы преобразователей 1 опорного и фазового каналов поступают соответственно опорный и исследуемый периодические сигнапы. Рассмотрим функционирование одного из параллельных каналов. формирователь 28 осуществляет преобразование опорного (исследуемого) периодического сигнала в последовательность импульсов с идентичными линейными участками на их передних фронтах, Причем преобразование периодических сигналов формирователями

28 в опорном и фазовом каналах осуществляется с сохранением фазового сдвига и частоты. Сформированная таким образом последовательность импульсов поступает на первый вход строб-смесителя 29, На второй вход строб-смесителя 29 поступают строб35 импульсы с выхода генерато1ра 2, На выходе строб-смесителя 29 формируются выборки, которые расширяются усилителем-расширителем 30 до необхо40 димых. длительностей и линейно усиливаются. Сформированный на выходе усилителя-расширителя 30 сигнал поступает на вход порогового .элемента

31 и импульсный вход ключа 32, При

45 превышении амплитуды импульсов расширенного сигнала заданного порогового значения U пороговый элеюр мент 31 формирует сигнал. по которо- му открывается ключ 32. При этом

50 на выходе ключа 32 формируются пакеты из трех импульсов (выборок) расширенного сигнала, амплитуда которых превышает заданное пороговое значение 11„,р, Выход ключа 32 является вторым выходом канала преобразователя l. Счетчик 34 подсчитывает поступающие на его импульсный вход импульсы с выхода генератора 2 между моментами прихода импульсов на управляющие входы счетчика 34 и импульсный вход ключа 33 с выхода ключа 32, 1(аждый импульс, поступающий на управляющий вход счетчика 34, обнуляет последний, Если между моментами обнуления счетчик 34 подсчитает хотя бы два импульса, то на его выходе появится управляющий сигнал, по которому триггер 35 установится в единичное состояние. При этом откроется управляемый триггером 35 ключ

33 H пропуcTHT HMII+JIbc поступившии в это время на его импульсный вход.

Пропущенный ключом 33 импульс поступит на счетный вход триггера 35, который по его заднему фронту возвратится в исходное (нулевое) состояние. При этом ключ 33 закроется.

Вследствие того, что интервалы между импульсами, входящие в один пакет, равны периоду Т эталонной частоты, а между пакетами больше или равны 2Т, > на выход ключа 33 (первом выходе канала преобразователя 1) будут пропускаться только первые импульсы пакетов.

Таким образом, на вторых выходах преобразователей 1 опорного и фазового каналов сформированы соответственно опорная и фазовая последовательности пакетов из тех импульсов (выборок) расширенных сигналов, амплитуда которых превышает заданное пороговое значение И„

На первых выходах йреобразователей 1 опорного и фазового каналов будут выделены первые импульсы (выборки) пакетов соответственно опорной и фазовой последовательностей пакето.э (выборок).

Па переднему фронту первого выделенного импульса первого пакета опорной последовательности, поступающего на счетный вход триггера 3, происходит переход последнего в единичное состояние, которому соответствует высокий уровень напряжения. Положитсльный перепад напряжения с выхода триггера 3 поступает на счетные входы триггеров 4 и 5, переводя их в единичное состояние соответственно. При этом открываются управляемые триггерами 4 и 5 ключи 7 и 8 и счетчики 10 и 11 начинают считать импупьсы эталонной частоты, поступающие на их входы через открытые ключи, 1242845

После перехода триггера 3 в единичное состояние на выходе элемента

И 13 появляются импульсы первого пакета опорной последовательности, которые подсчитываются счетчиком 12.

Одновременно аналого-цифровой преобразователь 16 переводит значения амплитуд импульсов первого пакета опорной последовательности в цифровой код. При этом запуск аналогоцифрового преобразователя 16 осуществляется импульсами, сформированными формирователем 27, из выборок, амплитуда которых измеряется.

Дешифратор 17 анализирует состояние счетчика 12 и после первого счетного импульса (например, по его заднему фронту) на его первом выходе формируется управляющий сигнал. По этому сигналу в регистр 18 записывается цифровой код преобразованной аналого-цифровым преобразователем

16 амплитуды U, первого импульса (выборки) первого пакета опорной последовательности. После прихода второго счетного импульса на вход счетчика 12 на втором выходе дешифратора 17 формируется управляющий сигнал. По этому сигналу в регистр

19 записывается цифровой код преобразованной аналого-цифровым преобразователем 16 амплитуды U второго импульса (выборки) первого пакета опорной последовательности, По первому выделенному импульсу первого пакета фазовой последовательности, поступающему на установочный вход "0" триггера 4, происходит переход последнего в.нулевое состояние. При этом закрывается управляемый триггером 4 ключ 7, прекращая дальнейшее поступление импульсов на вход счетчика 10.

Таким образом, счетчиком 10 было подсчитано число N, импульсов эталонной частоты, укладывающихся в фазовом интервале между первыми импульсами (выборками) первых пакетов опорной и фазовой последовательностей.

Первый выделенный импульс первого пакета фазовой последовательности поступает также на входы линии 6 задержки и формирователя 26. Формирователь 26 формирует импульс запуска аналого-цифрового преобразователя 15, который переводит в цифровой код значение амплитуды Б первог

50 импульса (выборки) первого пакета фазовой последовательности, Полученный цифровой код заносится в регистр 21 задержанным в линии 6 задержки на необходимое для преобразования время первым выделенным импульсом первого пакета фазовой последовательности

По переднему фронту первого выделенного импульса второго пакета опорной последовательности, поступающего с первого выхода преобразователя 1 опорного канала на счетный вход триггера 3, происходит его переход в нулевое состояние. При этом на выходе триггера 3 появляется напряжение, соответствующее логическому flPll а на его инверсном выходе— напряжение, соответствующее логической "1". С этого момента прекращается поступление импульсов на вход счетчика 12 с выхода элемента И 13. Цифровые коды амплитуд импульсов (выборок) второго пакета опорной последовательности сравниваются блоками 22 и 23 сравнения кодов соответственно с цифровыми кодами амплитуд

U, и U» хранящихся в регистрах 18 и

19. Как только значение цифрового кода амплитуды U очередного импульса (выборки) второго пакета опорной последовательности станет больше или равно значению цифрового кода амплитуды U первого импульса (выборки) первого пакета опорной последовательности и одновременно меньше значения цифрового кода амплитуды Б второго импульса (выборки) первого пакета опорной последовательности блоков

22 и 23 сравнения кодов, формируют управляющие сигналы, поступающие на первый и второй входы элемента И 14.

При этом на выходе элемента И 14 формируется импульс, по которому (например, по переднему фронту) цифровой код амплитуды U заносится в регистр

20, а триггер 5 устанавливается в нулевое состояние. По этому состоянию закрывается ключ 8, прекращая доступ импульсов на вход счетчика 11, Таким образом, счетчиком 11 было подсчитано число N импульсов эталонной частоты, укладывающихся в опорном интервале между первым импульсом (выборкой) первого пакета опорной последовательности и ближайшим к началу второго пакета опорной последова124284S

10 тельности импульсом (выборкой), значение амплитуды U которой находится в интервале между значениями амплитуд Б„ и П первых двух импульсов (выборок) первого пакета опорной последовательности.

Импульс, сформированный элементом И 14, поступает также на синхронизирующий вход (например, вход прерывания) вычислителя 25, по инициативе которого осуществляется занесение цифровой информации с регистрон

18-21 и счетчиков 10 и 11 в вычислитель 25. Подключение каждого из коммутируемых коммутатором 24 входов к информационному входу вычислителя 25 осуществляется счетчиком 9, на вход которого поступают импульсы с синхронизирующего выхода вычислите" ля 25 (таким выходом может являться шина, формирующая импульс готовности к приему очередной порции информации)..Каждый из укаэанных импуль" сов (например, по заднему фронту) увеличивает состояние счетчика на единицу и тем самь(м санкционирует подключение очередного коммутируемого входа коммутатора 24 к информационному входу вычислителя 25, После занесения всей необходимой(информации в вычислитель 25. последний осуществляет расчет неизвестного фазового сдвига по формуле (1).

Формула изобретения

Способ измерения сдвига фаз, заключающийся в том, что формируют импульсные последовательности из опорных и исследуемых периодических сигналов путем стробирования эталонной последонательностью импульсов выделяют фазовый и опорной интервалы вре мени, подсчитывают числа периодов эталонной последовательности импульсов в опорном и фазовом интервалах времени, отличающийся тем, что, с целью повышения тсчнос1-(4

N 1 P U — U р 1

U -U

М

Ъ

U2 U1

Uз и Uя — итуды выбогде U,, Б рок сигнала;

N число периодов эталонной часто ты „. укладывающихся н опорном интервале;

N — число периодов

Ф эталонной частоть(, укладывающихся в фазовом интервале, ти измерения, из стробированных посл(довательностей выбирают импульсы в моменты прохождения сигналов на

5 линейных участках одноименных фронтов, получают последовательности с амплитудами, пропорциональными амплитудам входных сигналов, формируют последовательности пакетов тех выборок, амплитуды которых пре— вышают заданное пороговое значение, при этом выбирают две следующие одна за другой выборки в начале или конце первого пакета опорной последовательности и измеряют их амплитуды„ причем первая выборка является начальной границей опорного и фазового интервалов, выбирают ближайшую к началу или концу второго пакета опорной последовательности выборку, измеренное значение амплитуды которой находится в интервале между амплитудами первых двух выборок, и принимают ее за конечную границу опорного интервала, выбирают в качестве конечной границы фазового интервала начальную или конечную выборку первого пакета фазовой последовательности, следующего непосредственно за первым пакетом опорной последовательности, и измеряют ее амплитуду, по полученным данным определяют сдвиг фаз (по следующему вы ражению:

1242845 а т, Фиг Ю

Составитель В.Шубин

Техред О.Сопко Корректор H.Ìóñêà

Редактор А.Козориз

Заказ 3699/43 Тираж 728

ВНИИЛИ Государственного комитета СССР по делам изобретений и открытий ! 13035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие,г.Ужгород,ул.Проектная,4